- 首页

- » 搜索

- » aodzip 发表的帖子

页次: 1

#1 Re: Openwrt/LEDE/AR9331/MT7688/RT5350 » MT7621AT 通用开发板 HATLab GateBoard-One 稳定可靠 功能丰富 » 2022-09-24 14:33:15

#2 Openwrt/LEDE/AR9331/MT7688/RT5350 » MT7621AT 通用开发板 HATLab GateBoard-One 稳定可靠 功能丰富 » 2022-09-24 09:57:26

- aodzip

- 回复: 6

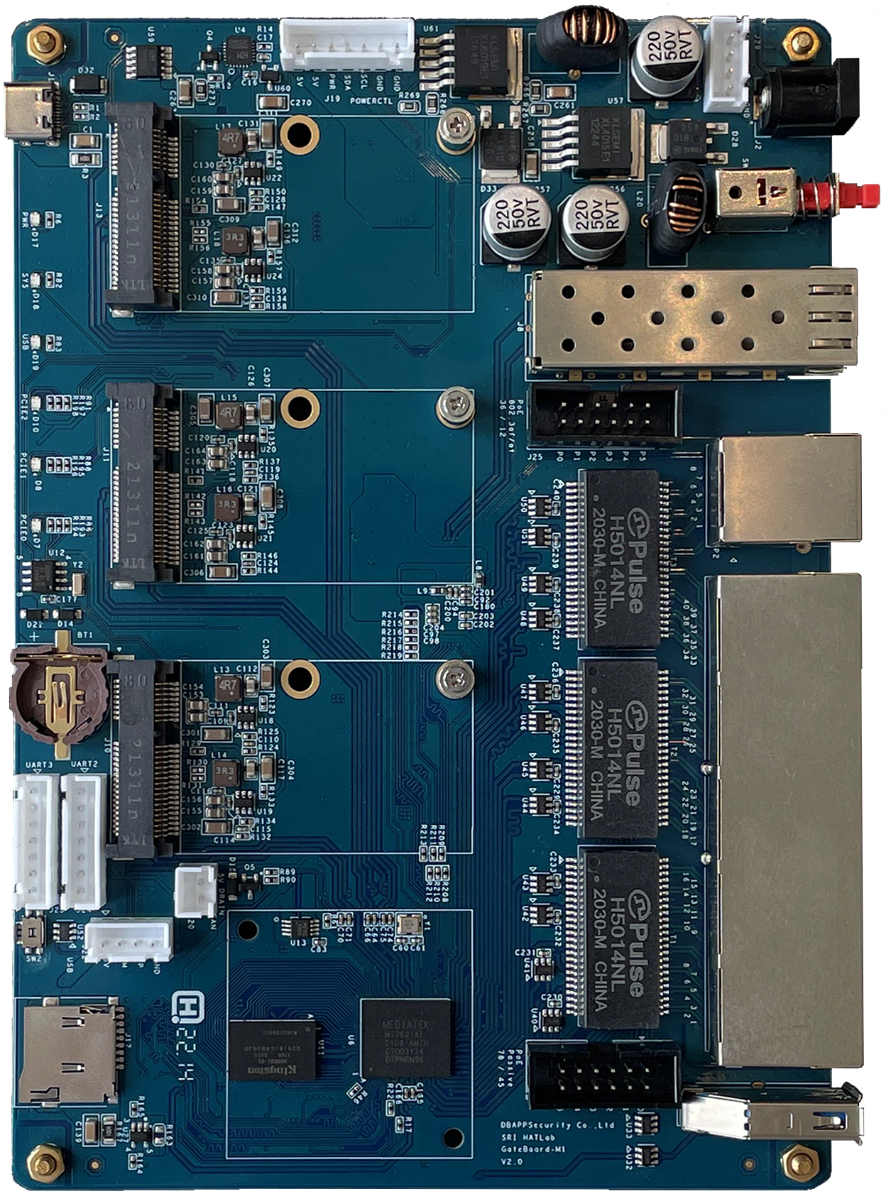

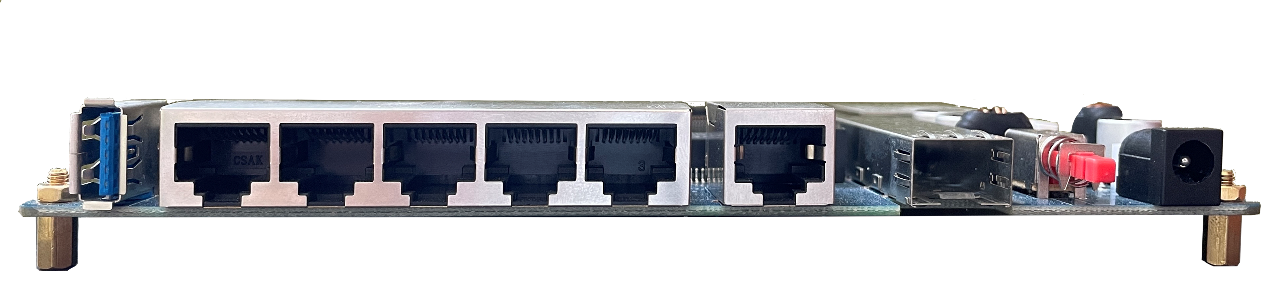

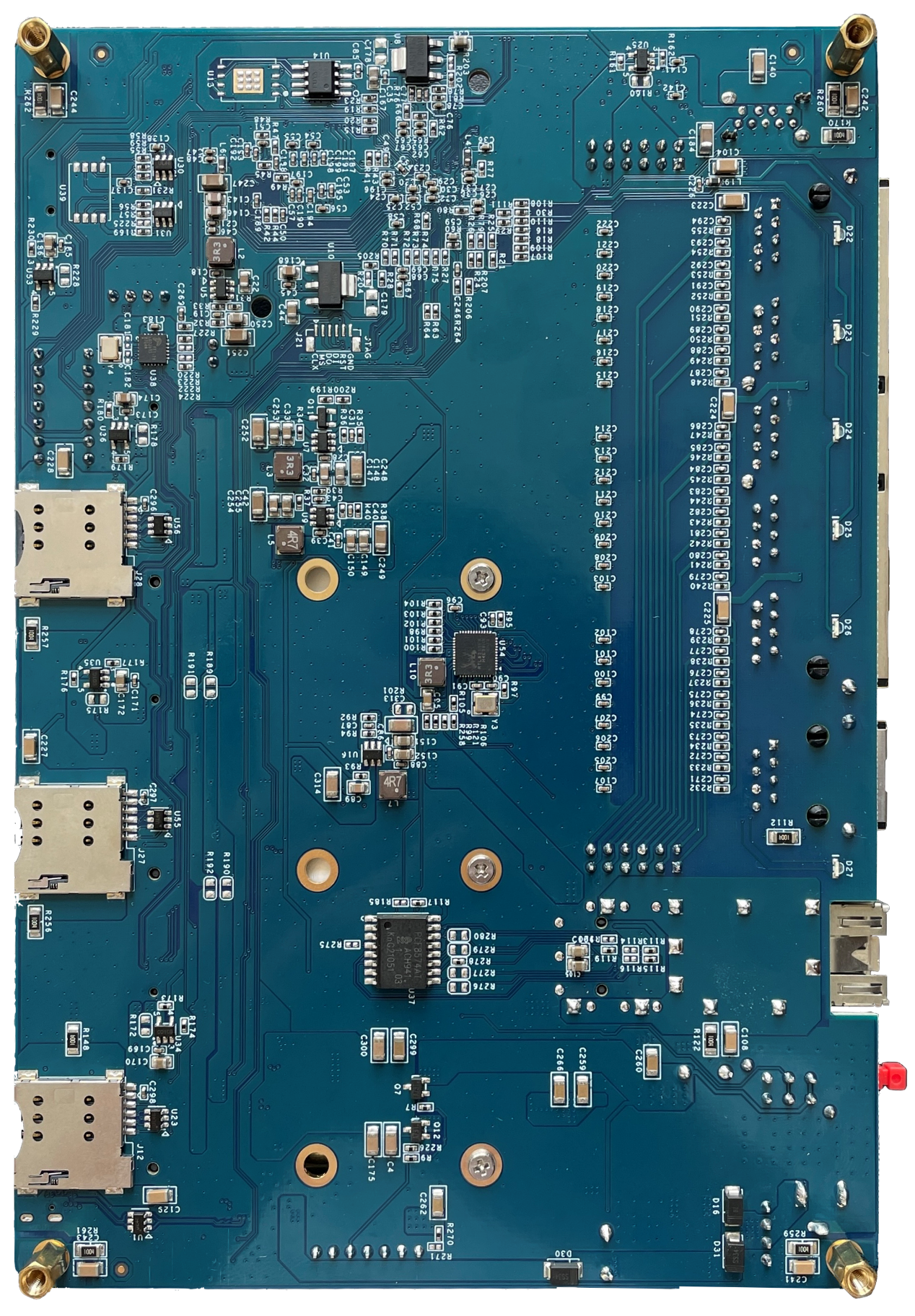

MT7621AT是一款经典的MIPS架构SoC,具有双核四线程880MHz~1200MHz的频率范围。不用过多介绍,先看一下成品图。

属性标签

MT7621AT双核四线程、全千兆1光5电、USB 3.0、TF卡、128MB NAND、Type-C Console口、MiniPCIe *3、PoE 分离器、NAT 2Gbps、交换机5Gbps、IPSec 350Mbps、IPv4 & IPv6、双看门狗电路、RS232、RS485、RTC、4G三网融合、双频WiFi

特色功能

1. U盘、TF卡、NAND三种启动设备

2. 双端口供电、0切换时间、Type-C PD(5/9/12/20 V)高功率供电、DC接口供电 宽电压范围4~24V

3. 集成USB调试串口,开发更方便

4. 全以太网口集成式PoE分离、合路器,可开发非标、国标供电、受电、中继方案

5. 支持纳秒级光纤授时功能

6. 双路四线串口,可实现RS232、RS485工业接口

开发环境

开发环境无需外部保密协议,全开源,驱动程序稳定适配节约开发时间。

主要支持版本: Linux Kernel 5.4、OpenWrt 21.02.03、 U-Boot 2022.10

次要支持版本: Debian Bullseye

可靠性与质量

整机已连续进行一年的打磨,历史迭代了15个硬件版本。

公测历时6个月,累次发售测试机80台,在近场窄带通讯、收费网关、光纤授时、嵌入式教学、个人玩家家用场景下经过丰富测试,稳定可靠。

部分客户直接使用开发板完成最终成品通过工业行业的高低温测试(-20~+85)、温度冲击测试(-20~60循环)、静电测试。

已验证模组

MT7603、MT7612、MT7615、MT7915 无线模组

ATH9K、ATH10K 无线模组

EC20、AIR720、AIR724 蜂窝模组

RTL8125B、RTL8111F、I210T 以太网控制器

ASM1061 SATA控制器

uPD720202 XHCI(USB 3.0)控制器

SM2263XT NVMe控制器

价格

单片坑网推广价 开发板259元/片

批量100台起即可定制 接口器件、功能跳线、可选芯片功能

交流群:971809157

资料库: http://47.96.30.235/web/#/12/61

BSP开源: https://github.com/DasSecurity-HatLab/openwrt

Bootloader开源: https://github.com/DasSecurity-HatLab/u-boot

淘宝链接: https://item.taobao.com/item.htm?id=678611967486

#3 Re: 全志 SOC » 贡献个V3S的原理图,顺便问下RGB数据线高低位的问题 » 2022-08-13 17:41:10

#4 Re: 全志 SOC » RGB接口和DVP接口 » 2021-10-12 10:54:47

#5 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-11-17 22:50:38

#6 全志 SOC » 主线Linux驱动 16路GPIO+全端口中断扩展芯片 AW9523B 驱动尝鲜 » 2020-11-03 19:50:09

- aodzip

- 回复: 6

I2C 16路GPIO复合全端口中断扩展芯片 AW9523B

给F1C100/200s扩展中断扩展GPIO,一拖16,对于低频率的外设中断挺管用的

https://item.szlcsc.com/159410.html

我觉得还蛮小蛮便宜的 4x4 TQFN 立创1000+:¥1.1954 / 个

测试Linux内核版本: Linux 5.4.73

&pio {

aw9523b_pins: aw9523b-pins {

pins = "PE10";

function = "gpio_in";

bias-pull-up;

};

};

&i2c0 {

pinctrl-names = "default";

pinctrl-0 = <&i2c0_pe_pins>;

status = "okay";

aw9523b: gpio-expander@5b {

compatible = "awinic,aw9523b-gpio";

reg = <0x5b>;

pinctrl-names = "default";

pinctrl-0 = <&aw9523b_pins>;

interrupt-parent = <&pio>;

interrupts = <4 10 IRQ_TYPE_EDGE_FALLING>;

gpio-controller;

#gpio-cells = <2>;

interrupt-controller;

#interrupt-cells = <2>;

wakeup-source;

};

};恒流LED部分的驱动?没有

#8 Re: 全志 SOC » 分享一下我知道的 aodzip tiny200 buildroot patch dfu windows 更新固件 » 2020-10-10 13:01:13

U-Boot 2020.07 (Oct 10 2020 - 08:45:42 +0800) Allwinner Technology CPU: Allwinner F Series (SUNIV) Model: Allwinner F1C100s Generic Device DRAM: 64 MiB MMC: mmc@1c0f000: 0, mmc@1c10000: 1 Setting up a 800x480 lcd console (overscan 0x0) In: serial Out: vga Err: vga Allwinner mUSB OTG (Peripheral) Hit any key to stop autoboot: 0 Booting from FEL... List of MTD devices: * spi-nand0 - device: spi-nand@1 - parent: spi@1c05000 - driver: spi_nand - type: NAND flash - block size: 0x20000 bytes - min I/O: 0x800 bytes - OOB size: 64 bytes - OOB available: 31 bytes - 0x000000000000-0x000008000000 : "spi-nand0" DFU waiting on SPI-NAND... musb-hdrc: peripheral reset irq lost! ##############################################################################################################################################################################################################################################################################################################################################################################################################################################################################################Skipping bad block at 0x03bc0000 #################################################################################################################################################################################################################################################################################################Skipping bad block at 0x06000000 ##############################################################################################################################################################################################################################################################Skipping bad block at 0x07fe0000 Limit reached 0x8000000 while erasing at offset 0x7fe0000Skipping bad block at 0x03bc0000

Skipping bad block at 0x06000000

Skipping bad block at 0x07fe0000请教烧写spi nand的时候跳开三块block, 程序不会出错吗?

不会的,可以放心使用

#9 Re: 全志 SOC » 分享一下我知道的 aodzip tiny200 buildroot patch dfu windows 更新固件 » 2020-10-10 13:00:52

奇怪, 我的dfu刷nor之后是这样的:

U-Boot SPL 2020.07 (Oct 09 2020 - 17:01:22 +0800) DRAM: 64 MiB Trying to boot from MMC1 Card did not respond to voltage select! spl: mmc init failed with error: -95 Trying to boot from MMC2 Card did not respond to voltage select! spl: mmc init failed with error: -95 Trying to boot from sunxi SPI U-Boot 2020.07 (Oct 09 2020 - 17:01:22 +0800) Allwinner Technology CPU: Allwinner F Series (SUNIV) Model: Allwinner F1C100s Generic Device DRAM: 64 MiB MMC: mmc@1c0f000: 0, mmc@1c10000: 1 Setting up a 800x480 lcd console (overscan 0x0) In: serial Out: vga Err: vga Allwinner mUSB OTG (Peripheral) Hit any key to stop autoboot: 0 Booting from FEL... unknown raw ID 82e625a8 List of MTD devices: No MTD device found SF: Detected w25q128 with page size 256 Bytes, erase size 4 KiB, total 16 MiB DFU waiting on SPI-NOR... Card did not respond to voltage select! Card did not respond to voltage select! Card did not respond to voltage select! unknown raw ID 82e62328 List of MTD devices: No MTD device found SF: Detected w25q128 with page size 256 Bytes, erase size 4 KiB, total 16 MiB Booting from SPI-NOR... device 0 offset 0x70000, size 0x10000 SF: 65536 bytes @ 0x70000 Read: OK device 0 offset 0x80000, size 0x580000 SF: 5767168 bytes @ 0x80000 Read: OK ## Flattened Device Tree blob at 80700000 Booting using the fdt blob at 0x80700000 Loading Device Tree to 816f9000, end 816ffc6c ... OK Cannot setup simplefb: node not found Starting kernel ... [ 0.000000] Booting Linux on physical CPU 0x0 [ 0.000000] Linux version 5.4.66 (whycan@ubuntu) (gcc version 8.4.0 (Buildroot 2020.02.4-00002-g2e2c3d224a)) #1 Fri Oct 9 10:45:59 CST 2020 [ 0.000000] CPU: ARM926EJ-S [41069265] revision 5 (ARMv5TEJ), cr=0005317f [ 0.000000] CPU: VIVT data cache, VIVT instruction cache [ 0.000000] OF: fdt: Machine model: Widora MangoPi R3 [ 0.000000] Memory policy: Data cache writeback [ 0.000000] cma: Reserved 16 MiB at 0x83000000 [ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 16256 [ 0.000000] Kernel command line: console=ttyS0,115200 earlyprintk rootwait consoleblank=0 net.ifnames=0 biosdevname=0 root=/dev/mtdblock3 overlayfsdev=/dev/mtdblock4 [ 0.000000] Dentry cache hash table entries: 8192 (order: 3, 32768 bytes, linear) [ 0.000000] Inode-cache hash table entries: 4096 (order: 2, 16384 bytes, linear) [ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off [ 0.000000] Memory: 38736K/65536K available (6144K kernel code, 248K rwdata, 1680K rodata, 1024K init, 225K bss, 10416K reserved, 16384K cma-reserved) [ 0.000000] SLUB: HWalign=32, Order=0-3, MinObjects=0, CPUs=1, Nodes=1 [ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16 [ 0.000000] random: get_random_bytes called from start_kernel+0x254/0x444 with crng_init=0 [ 0.000048] sched_clock: 32 bits at 24MHz, resolution 41ns, wraps every 89478484971ns [ 0.000136] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns [ 0.000898] Console: colour dummy device 80x30 [ 0.001007] Calibrating delay loop... 203.16 BogoMIPS (lpj=1015808) [ 0.070261] pid_max: default: 32768 minimum: 301 [ 0.070785] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes, linear) [ 0.070831] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes, linear) [ 0.072790] CPU: Testing write buffer coherency: ok [ 0.074907] Setting up static identity map for 0x80100000 - 0x80100058 [ 0.076229] devtmpfs: initialized [ 0.088171] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns [ 0.088235] futex hash table entries: 256 (order: -1, 3072 bytes, linear) [ 0.092581] pinctrl core: initialized pinctrl subsystem [ 0.095307] NET: Registered protocol family 16 [ 0.099095] DMA: preallocated 256 KiB pool for atomic coherent allocations [ 0.101486] cpuidle: using governor menu [ 0.146254] SCSI subsystem initialized [ 0.146645] usbcore: registered new interface driver usbfs [ 0.146863] usbcore: registered new interface driver hub [ 0.147061] usbcore: registered new device driver usb [ 0.147570] mc: Linux media interface: v0.10 [ 0.147728] videodev: Linux video capture interface: v2.00 [ 0.147852] pps_core: LinuxPPS API ver. 1 registered [ 0.147873] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it> [ 0.147936] PTP clock support registered [ 0.149023] ion_parse_dt_heap_common: id 4 type 4 name cma align 1000 [ 0.150038] Advanced Linux Sound Architecture Driver Initialized. [ 0.152634] clocksource: Switched to clocksource timer [ 0.184349] thermal_sys: Registered thermal governor 'step_wise' [ 0.185126] NET: Registered protocol family 2 [ 0.186738] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 4096 bytes, linear) [ 0.186828] TCP established hash table entries: 1024 (order: 0, 4096 bytes, linear) [ 0.186882] TCP bind hash table entries: 1024 (order: 0, 4096 bytes, linear) [ 0.186932] TCP: Hash tables configured (established 1024 bind 1024) [ 0.187249] UDP hash table entries: 256 (order: 0, 4096 bytes, linear) [ 0.187318] UDP-Lite hash table entries: 256 (order: 0, 4096 bytes, linear) [ 0.187830] NET: Registered protocol family 1 [ 0.190554] NetWinder Floating Point Emulator V0.97 (double precision) [ 0.192441] Initialise system trusted keyrings [ 0.193207] workingset: timestamp_bits=30 max_order=14 bucket_order=0 [ 0.215059] squashfs: version 4.0 (2009/01/31) Phillip Lougher [ 0.215677] jffs2: version 2.2. (NAND) (SUMMARY) © 2001-2006 Red Hat, Inc. [ 0.330481] Key type asymmetric registered [ 0.330523] Asymmetric key parser 'x509' registered [ 0.330703] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 249) [ 0.330731] io scheduler mq-deadline registered [ 0.330747] io scheduler kyber registered [ 0.346354] suniv-f1c100s-pinctrl 1c20800.pinctrl: initialized sunXi PIO driver [ 0.370872] Serial: 8250/16550 driver, 8 ports, IRQ sharing disabled [ 0.377160] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pa not found, using dummy regulator [ 0.378512] printk: console [ttyS0] disabled [ 0.398826] 1c25400.serial: ttyS0 at MMIO 0x1c25400 (irq = 28, base_baud = 6250000) is a 16550A [ 0.831398] printk: console [ttyS0] enabled [ 0.841222] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pd not found, using dummy regulator [ 0.862505] panel-simple panel: panel supply power not found, using dummy regulator [ 0.872238] SCSI Media Changer driver v0.25 [ 0.878154] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pc not found, using dummy regulator [ 0.891020] spi-nor spi0.0: w25q128 (16384 Kbytes) [ 0.897112] 5 fixed-partitions partitions found on MTD device spi0.0 [ 0.903585] Creating 5 MTD partitions on "spi0.0": [ 0.908395] 0x000000000000-0x000000070000 : "u-boot" [ 0.916874] 0x000000070000-0x000000080000 : "dtb" [ 0.925100] 0x000000080000-0x000000600000 : "kernel" [ 0.933612] 0x000000600000-0x000000d00000 : "rom" [ 0.941697] 0x000000d00000-0x000001000000 : "overlay" [ 0.950826] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver [ 0.957480] ehci-platform: EHCI generic platform driver [ 0.963210] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver [ 0.969438] ohci-platform: OHCI generic platform driver [ 0.975283] usbcore: registered new interface driver usb-storage [ 0.982286] usb_phy_generic usb_phy_generic.0.auto: usb_phy_generic.0.auto supply vcc not found, using dummy regulator [ 0.996003] i2c /dev entries driver [ 1.000157] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pd not found, using dummy regulator [ 1.013953] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pe not found, using dummy regulator [ 1.024945] sun4i-csi 1cb0000.csi: Packed (RAW) format enabled. [ 1.032813] sunxi-wdt 1c20ca0.watchdog: Watchdog enabled (timeout=16 sec, nowayout=0) [ 1.042862] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pf not found, using dummy regulator [ 1.080801] sunxi-mmc 1c0f000.mmc: initialized, max. request size: 16384 KB [ 1.090260] usbcore: registered new interface driver usbhid [ 1.095950] usbhid: USB HID core driver [ 1.100117] sunxi-cedar 1c0e000.video-codec: sunxi cedar version 0.01alpha [ 1.107455] sunxi-cedar 1c0e000.video-codec: cedar-ve the get irq is 20 [ 1.119301] debugfs: Directory '1c23c00.codec' with parent 'F1C100s Audio Codec' already present! [ 1.133256] sun4i-codec 1c23c00.codec: Codec <-> 1c23c00.codec mapping ok [ 1.149178] NET: Registered protocol family 17 [ 1.153855] Key type dns_resolver registered [ 1.159288] Loading compiled-in X.509 certificates [ 1.177998] sun4i-drm soc:display-engine: bound 1e00000.display-frontend (ops 0xc073b3d8) [ 1.187051] sun4i-drm soc:display-engine: bound 1e60000.display-backend (ops 0xc073ac18) [ 1.196657] sun4i-drm soc:display-engine: bound 1c0c000.lcd-controller (ops 0xc07397b8) [ 1.205217] sun4i-drm soc:display-engine: bound 1c0a000.tv-encoder (ops 0xc073a4d8) [ 1.212994] [drm] Supports vblank timestamp caching Rev 2 (21.10.2013). [ 1.219596] [drm] No driver support for vblank timestamp query. [ 1.227356] [drm] Initialized sun4i-drm 1.0.0 20150629 for soc:display-engine on minor 0 [ 1.236391] [drm] kms: can't enable cloning when we probably wanted to. [ 1.308254] Console: switching to colour frame buffer device 100x30 [ 1.347156] sun4i-drm soc:display-engine: fb0: sun4i-drmdrmfb frame buffer device [ 1.355715] cfg80211: Loading compiled-in X.509 certificates for regulatory database [ 1.373530] cfg80211: Loaded X.509 cert 'sforshee: 00b28ddf47aef9cea7' [ 1.380288] ALSA device list: [ 1.383395] #0: F1C100s Audio Codec [ 1.387651] platform regulatory.0: Direct firmware load for regulatory.db failed with error -2 [ 1.396377] cfg80211: failed to load regulatory.db [ 1.405754] random: fast init done [ 1.412139] List of all partitions: [ 1.415808] 1f00 448 mtdblock0 [ 1.415819] (driver?) [ 1.422427] 1f01 64 mtdblock1 [ 1.422434] (driver?) [ 1.429054] 1f02 5632 mtdblock2 [ 1.429062] (driver?) [ 1.435691] 1f03 7168 mtdblock3 [ 1.435698] (driver?) [ 1.442233] 1f04 3072 mtdblock4 [ 1.442239] (driver?) [ 1.448815] No filesystem could mount root, tried: [ 1.448822] ext3 [ 1.453773] ext2 [ 1.455700] ext4 [ 1.457622] squashfs [ 1.459544] vfat [ 1.461811] [ 1.465291] Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(31,3) [ 1.473628] CPU: 0 PID: 1 Comm: swapper Not tainted 5.4.66 #1 [ 1.479356] Hardware name: Allwinner suniv Family [ 1.484139] [<c010e6a8>] (unwind_backtrace) from [<c010b9c4>] (show_stack+0x10/0x14) [ 1.491891] [<c010b9c4>] (show_stack) from [<c011702c>] (panic+0xe8/0x2e4) [ 1.498779] [<c011702c>] (panic) from [<c090135c>] (mount_block_root+0x2bc/0x31c) [ 1.506264] [<c090135c>] (mount_block_root) from [<c0901568>] (prepare_namespace+0x128/0x188) [ 1.514794] [<c0901568>] (prepare_namespace) from [<c06f9cb0>] (kernel_init+0x8/0x108) [ 1.522713] [<c06f9cb0>] (kernel_init) from [<c01010e0>] (ret_from_fork+0x14/0x34) [ 1.530261] Exception stack(0xc2839fb0 to 0xc2839ff8) [ 1.535309] 9fa0: 00000000 00000000 00000000 00000000 [ 1.543477] 9fc0: 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 [ 1.551640] 9fe0: 00000000 00000000 00000000 00000000 00000013 00000000 [ 1.558250] ---[ end Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(31,3) ]---

根据你启动日志来看是比较老,建议重拉git

#10 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-10-10 12:58:12

#12 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-10-07 01:18:09

我直接使用晕哥网站的离线包 buildroot-tiny200-20200924.tgz,检出git资源,然后执行了以下操作:

(1)make widora_mangopi_r3_defconfig

(2)make

最终,出现以下错误信息,请问是我这里环境出现问题,还是作者的buildroot资源问题呢?YACC scripts/dtc/dtc-parser.tab.[ch] HOSTCC scripts/dtc/dtc-lexer.lex.o HOSTCC scripts/dtc/dtc-parser.tab.o HOSTLD scripts/dtc/dtc HOSTCC scripts/kallsyms UPD include/generated/utsrelease.h HOSTCC scripts/conmakehash HOSTCC scripts/sortextable DTC arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dtb arch/arm/boot/dts/suniv-f1c100s.dtsi:501.21-512.5: ERROR (phandle_references): /soc/i2c@1c27000: Reference to non-existent node or label "i2c0_pins" ERROR: Input tree has errors, aborting (use -f to force output) scripts/Makefile.lib:285: recipe for target 'arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dtb' failed make[3]: *** [arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dtb] Error 2 Makefile:1269: recipe for target 'dtbs' failed make[2]: *** [dtbs] Error 2 make[2]: *** 正在等待未完成的任务.... HOSTCC scripts/asn1_compiler HOSTCC scripts/extract-cert package/pkg-generic.mk:266: recipe for target '/home/book/HDD/Disk0/Document/StudyData/F1C100s/tiny200s-buildroot/output/build/linux-5.4.66/.stamp_built' failed make[1]: *** [/home/book/HDD/Disk0/Document/StudyData/F1C100s/tiny200s-buildroot/output/build/linux-5.4.66/.stamp_built] Error 2 Makefile:84: recipe for target '_all' failed make: *** [_all] Error 2

亲,这边建议直接拉取一个新鲜的呢

#14 Re: 全志 SOC » F1C100/200s 开源开发包近期更新 默认集成OverlayFS、支持多种线刷方式、集成CedarX (2020.10.1) » 2020-09-30 18:33:12

#15 Re: 全志 SOC » F1C100/200s 开源开发包近期更新 默认集成OverlayFS、支持多种线刷方式、集成CedarX (2020.10.1) » 2020-09-30 18:29:34

#17 全志 SOC » F1C100/200s 开源开发包近期更新 默认集成OverlayFS、支持多种线刷方式、集成CedarX (2020.10.1) » 2020-09-30 17:39:00

- aodzip

- 回复: 7

标题时间问就是穿越了!

项目持续更新地址

https://github.com/aodzip/buildroot-tiny200

为啥日常reset git log,这是提醒你改的太多,建议重新从头构建。

针对SPI-NOR SPI-NAND目标,在squashfs root之后又增加了一个jffs2作为overlayfs

总而言之,根文件系统能写了

想要实现“恢复出厂设置”运行 mtd -r erase /dev/mtd4

在U-Boot实现了新增了DFU模式刷写固件,上电后等待三秒钟,没有DFU请求将会继续开机。

支持了NOR NAND的全量刷写,分区部分刷写。

支持了MMC1的全量刷写。MMC0也就是TF卡槽默认不会进入DFU,除非除了MMC0无其他存储器。

集成CedarX,反正我也不会用,也没有例程。

#18 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-09-04 19:28:34

# 目前开发包对芯片驱动的支持情况

## 正常工作 && 已验证

### 启动项:

- SPI NOR Flash

- SPI NAND Flash

- MMC 0

- MMC 1

### U-Boot 驱动:

- Basic LCD

- GPIO Backlight

- USB Peripheral

- MTD Devices

### Linux 驱动:

- Simple Peripheral: GPIO, SPI, UART, IIC, SDIO, PWM

- DMA Controller

- Audio Codec: Playback, Mic-IN

- USB: Peripheral Mode, Host Mode

- DVP Camera: OV2640, OV5640

- Display Engine: Frontend, Backend, TCON

## 应该正常工作但是没有经过测试

### U-Boot 驱动:

- PWM Backlight

### Linux 驱动:

- Audio Codec: FM-IN, Line-IN

- USB: OTG Mode

- IR Receiver

- Keypad ADC

## 正在开发中且部分功能可用

### Linux 驱动:

- TV(CVBS) Encoder

- Touchscreen Sensor

- Cedar Video Engine

## 暂无计划支持

... 下方和其他没有提到的外设

### Linux 驱动:

- TV(CVBS) Decoder

- Digital Audio

- DE-interlace

- RSB Bus

- OWA Bus

#19 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-09-04 19:13:37

- aodzip

- 回复: 150

主要更新

- 新增了OV2640和OV5640摄像头的支持,不妨体验一下

其他更新

- 调整了默认的Linux内核config

- 修复了F1C100s无法启动Kernel的问题

- USB外设默认工作在MTP模式,USB连接到电脑后可直接访问根目录

- U-Boot多处优化

开发包地址

- https://github.com/aodzip/buildroot-tiny200

请注意,从老版本pull到最新的版本需要

make clean

make widora_tiny200_defconfig

make -j8才能应用上最新的更改,此操作会清空编译目录和镜像目录,注意备份重要文件。

以下由 @哇酷小二 2020-09-27 添加:

--------------------------------

tiny200 购买地址: https://item.taobao.com/item.htm?id=587925184119

以下由 @哇酷小二 2020-09-30 添加:

-------------------------------

楼主的带完整log的git仓库下载: buildroot-tiny200-20200924.tgz

需要执行 git reset --hard

仅作记录用,建议从楼主仓库拉取最新版本

#20 Re: 全志 SOC » 新买的WIDORA TINNY200 R3,不能使用USB HOST功能,但是能用USB DEVICE功能,请大家帮忙看看 » 2020-09-04 18:57:40

#23 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-20 15:03:04

执行make后报如下的错误

ERROR: No hash found for gcc-8.4.0.tar.xz

package/pkg-generic.mk:167: recipe for target '/home/zhang/buildroot-tiny200-master/output/build/host-gcc-initial-8.4.0/.stamp_downloaded' failed

make: *** [/home/zhang/buildroot-tiny200-master/output/build/host-gcc-initial-8.4.0/.stamp_downloaded] Error 1

是严格按照GitHub上的说明进行的么

#24 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-19 21:31:20

能不能先建一个分区表,把相对应的固件丢进响应分区,系统启动后通过resiz2fs来扩展分区大小

https://github.com/aodzip/buildroot-tiny200

项目已经移动到这里继续开发,今天刚推送了128M全量镜像的烧录方法

#26 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-13 17:34:56

=> ums 100 mmc 0 UMS: LUN 0, dev 0, hwpart 0, sector 0x0, count 0x3aa000 CTRL+C - Operation aborted => ums 1000 mmc 0 UMS: LUN 0, dev 0, hwpart 0, sector 0x0, count 0x3aa000 CTRL+C - Operation aborted => ums ums - Use the UMS [USB Mass Storage] Usage: ums <USB_controller> [<devtype>] <dev[:part]> e.g. ums 0 mmc 0 devtype defaults to mmc =>请问楼主 @aodzip 这个 <USB_controller> 参数代表什么意义呢?

第n个usb控制器

#31 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-12 23:32:04

请教下aodzip大佬,你的ov2640怎么测试的,我这边接上ov2640,出现/dev/video0,使用命令如下抓不到图片

# fswebcam -S 5 -d /dev/video0 -p UYVY -r 800x600 test.jpg

--- Opening /dev/video0...

Trying source module v4l2...

/dev/video0 opened.

No input was specified, using the first.

Unable to find a compatible palette format.查看csi中断次数,显示也为0

28: 0 sun4i_irq 32 Edge 1cb0000.csi

好像并没有触发csi中断

fswebcam我也没有调试通

用v4l2-ctl抓裸流是可以的

#34 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-12 15:59:31

spi flash 固件sysimage-flash.img有一点点bug, 可能这个u-boot打包的是TF卡版本的。

确实是BUG,SPI启动命令没有写进去

手动在uboot下执行一下这个

sf probe

sf read 0x80c00000 0x0f0000 0x4000

sf read 0x80008000 0x100000 0x800000

bootz 0x80008000 - 0x80c00000可以将UBOOT中

CONFIG_BOOTCOMMAND="run distro_bootcmd;sf probe;sf read 0x80c00000 0x0f0000 0x4000;sf read 0x80008000 0x100000 0x800000;bootz 0x80008000 - 0x80c00000"这样uboot在mmc启动失败后就会自动尝试从SPI NOR启动

#37 Re: 全志 SOC » AC108的开发文档,是不是普通人不太可能拿到? » 2020-08-10 23:15:09

#38 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-10 11:09:04

cd configs

ln -s ../board/widora/tiny200/widora_tiny200_defconfig .

今天我从头测试了一下,上面教程中的指令有误,应该用这个

#39 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-10 09:42:46

aodzip 大神,能不能介绍一下cedarX怎么使用?我按照 github 上“Allwinner CedarX Driver for Mainline Linux 5.4” 配置完cedarX,也编译了 libcedarc,但不知道怎么使用,是不是要像 tina 那样编译一个 tplayer 才行?还有解码出来的YUV 裸流要怎么配合 de-be 进行转换并显示?是不是要开启 drm,使用drm的接口来显示?

YUV流确实需要DRM来输出,这个开发包内DRM应该是配置好了。

Cedar VE我也不会用,只是移植了驱动。照理说是兼容全志原厂的开发方式的

如果用的是我的那个libcedarc,记得把cedarc的lib也换成arm9的

#41 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-09 20:47:10

这个问题不太应该出现,检查buildroot解压方式对不对,是否完整,第二尽量不要用root权限运行buildroot

#42 Re: 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-09 20:33:43

root@vultr:/opt/buildroot-2020.02.3# ln -s board/widora/tiny200/widora_tiny200_defconfig config/ ln: target 'config/' is not a directory: No such file or directory root@vultr:/opt/buildroot-2020.02.3# ls board/widora/tiny200/widora_tiny200_defconfig board/widora/tiny200/widora_tiny200_defconfigln命令这样用会出错, 请问这行命令的用意是什么呢?

我写的时候少了个s……改成下面这个

ln -s board/widora/tiny200/widora_tiny200_defconfig configs/

这个是为了软连接defconfig

#44 全志 SOC » Widora TINY200 R2 体验版开源开发包,修复了大部分F1C100s/F1C200s的遗留问题 » 2020-08-09 18:06:47

- aodzip

- 回复: 122

请注意,此版本为测试版,可能存在编译不通过,部分功能失效等问题,期待试用反馈,也欢迎一起修复BUG,贡献代码。

请注意,本开发包是为后续的TINY200 R3设计的,在TINY200 R3公开发售后将不再优先处理R2的问题,一周后,TINY200 R2的支持将被取消。

软件版本

Buildroot 2020.02.3 (https://buildroot.org/downloads/buildroot-2020.02.3.tar.gz)

U-Boot 2020.07 (自动下载)

Linux 5.4.52 (自动下载)

安装方法

将widora文件夹放入board文件夹

cd configs

ln -s ../board/widora/tiny200/widora_tiny200_defconfig .

make widora_tiny200_defconfig生成第一个镜像

make -j8

驱动支持情况

1. U-Boot SPL

支持切换启动串口,默认为R2版本硬件的UART1

支持启动设备智能识别,不会出现BROM从SPI引导但是SPL从MMC0引导的问题

支持从SDC0 (4-bit SDIO) 启动

支持从SDC1 (1-bit SDIO) 启动

支持从SPI NAND (GD5F1GQ4UAxxG) 启动

支持从SPI NOR 启动

2. U-Boot TPL

支持USB Device模式

支持UMS、Fastboot功能

支持mmc命令操作SDC0、SDC1

支持sf命令写入 SPI NOR

支持mtd命令写入 SPI NAND,支持OOB和ECC管理

支持LCD显示初始化

3. Linux

支持 USB OTG

支持 DE-FE DE-BE TCON 等显示组件,LCD显示正常。已配置TVE输出,但是显示错位。

支持 Audio Codec,修复了44100kHz解码声音变快的问题,已测试MIC输入和HP输出,未测试但已配置Line IN、FM IN

支持 I2C SPI UART MMC 总线外设

已配置 Cedar-VE 硬件编解码引擎,请参考(https://github.com/aodzip/cedar)安装

支持DVP-CSI摄像头,支持CLK-OUT引脚输出,板上OV2640无需额外飞线晶振或PWM,已测试RAW格式抓取

补丁包本站下载: widora.zip

以下由 @哇酷小二 2020-08-12 #39 更新

-----------------------------------------------

感谢 @歌以咏志, 我这边也编译完成了, 顺便打包了:

Q群 516836432 或 662381849 附件下载: buildroot-2020.02.3_widora_tiny200s_R2_with_aodzip_patch.tgz

md5校验码: d8304fa952e00e0fabfcff3d8659ae62

解压姿势:

tar xvf buildroot-2020.02.3_widora_tiny200s_R2_with_aodzip_patch.tgz -C /

工作目录: /opt/buildroot-2020.02.3

#50 全志 SOC » F1C100/200s U-Boot 2020.07 (USB + LCD + 1bit SDIO) » 2020-07-22 20:22:53

- aodzip

- 回复: 66

适用于F1C100/200s的U-Boot 基于2020.07 TAG

支持 MMC0(4-bit SDC0) / MMC2(1-bit SDC1) / SPI NOR启动。

SDIO WIFI + TF卡,我全都要。

支持USB mOTG Peripheral,目前开启了ums和fastboot

但是fastboot没有配分区,就拿ums写mmc玩吧。

支持LCD

Patch:

0001-v2020_07_3.zip

#51 Re: 全志 SOC » 摄像头驱动 主线DVP与MIPI-CSI2 » 2020-05-26 11:43:50

#52 Re: 全志 SOC » 摄像头驱动 主线DVP与MIPI-CSI2 » 2020-05-26 11:43:12

#53 Re: 全志 SOC » 摄像头驱动 主线DVP与MIPI-CSI2 » 2020-05-25 20:16:18

#54 Re: 全志 SOC » 摄像头驱动 主线DVP与MIPI-CSI2 » 2020-05-25 16:17:47

#55 Re: 全志 SOC » 摄像头驱动 主线DVP与MIPI-CSI2 » 2020-05-25 16:12:37

#56 Re: 全志 SOC » 摄像头驱动 主线DVP与MIPI-CSI2 » 2020-05-25 16:02:53

大佬,我移植后,运行fswebcam出现以下情况,请是什么问题?我用的摄像头是ov5647

# fswebcam -S 5 -d /dev/video0 -p YUV420P -r 320x240 test.jpg

--- Opening /dev/video0...

Trying source module v4l2...

/dev/video0 opened.

No input was specified, using the first.

Error starting stream.

VIDIOC_STREAMON: Invalid argument

Unable to use mmap. Using read instead.

Unable to use read.

请提供更详细的信息:Linux版本,media-ctl所使用的参数,dmesg日志

而且github上的版本比坑网缓存的驱动改动已经很大了,你是从github同步的代码吗?

#60 Re: 全志 SOC » Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷) » 2020-05-06 12:18:32

好像不支持 SPI FLASH, 大佬可以把这个代码合并进去吗?

https://github.com/Lichee-Pi/u-boot/commits/v3s-spi-experimental

等我有能测试SPI设备的时候再搞

#61 全志 SOC » 摄像头驱动 主线DVP与MIPI-CSI2 » 2020-05-04 03:29:16

- aodzip

- 回复: 43

白嫖: https://github.com/aodzip/sun6i-mipi-csi

MIPI-CSI2 驱动已经测试OV5640摄像头2Lane模式 1080P@15FPS 720P@30FPS

DVP没测试,因为主线本身就支持DVP,希望没给它改坏吧

以下由 @哇酷小二 2020-05-04 添加:

-------------------------------------

不方便打开github的朋友可以此处下载: sun6i-mipi-csi_20200504.7z

#63 Re: 全志 SOC » Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷) » 2020-04-27 15:48:55

Allwinner mUSB OTG (Peripheral)

Net: phy interface0

eth0: ethernet@1c30000

Warning: usb_ether MAC addresses don't match:

....

如果板子log停在 musb-hdrc: peripheral reset irq lost! 这里,是不是说明板子那边配置应该已经正常了,谢谢!

H3我不了解具体情况,我这个代码里存在部分专门为S3做的适配,H3用很可能出BUG。可能具体的一些调整操作要你自己来做了。

fastboot不认看看dmesg中有没有枚举设备,如果没有的话可能就有点麻烦

#64 Re: 全志 SOC » Linux主线已经支持 VPU H.264 硬解码多时了,有没有哪位测试过? » 2020-04-27 15:25:15

我就挖一铲子,这样通过搜索引擎过来的人也知道传统的CedarX框架也支持主线了

https://whycan.cn/t_4219.html

#71 全志 SOC » 编解码引擎 CedarX for Mainline Linux v5.4 » 2020-04-26 14:29:39

- aodzip

- 回复: 72

白嫖: https://github.com/aodzip/cedar/

配套的ion驱动: https://github.com/aodzip/cedar-ion/

想尝鲜的可以冲了

Allwinner S3 YUV to H264编码测试已经通过

#76 全志 SOC » Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷) » 2020-04-21 12:08:04

- aodzip

- 回复: 56

白嫖: https://github.com/aodzip/u-boot/tree/Allwinner-S3

可能是S3目前最好用的u-boot了

支持LCD,支持以太网,支持USB Gadget

LCD演示:

Fastboot演示:

./fel-flash.sh

sunxi-fel -p uboot output/images/u-boot-sunxi-with-spl.bin

fastboot oem format

fastboot flash loader output/images/u-boot-sunxi-with-spl.bin

fastboot flash esp output/images/boot.vfat

fastboot flash system output/images/rootfs.ext4

fastboot reboot以下是 @哇酷小二 2020-04-30 整理的修改记录:

-------------------------------------------------

https://github.com/u-boot/u-boot/commit/e4837da7828293ea49abc579f939c0f5c4b127c3

git diff e4837da7828293ea49abc579f939c0f5c4b127c3 c8aac3e1734b87c2800c05fd5428f3aae8d8ae73 > ~/uboot_s3_aodzip.diff

diff --git a/Kconfig b/Kconfig

index 8bae87e3f6..cc625d0253 100644

--- a/Kconfig

+++ b/Kconfig

@@ -589,9 +589,9 @@ config HAVE_SYS_TEXT_BASE

config SYS_TEXT_BASE

depends on HAVE_SYS_TEXT_BASE

default 0x80800000 if ARCH_OMAP2PLUS || ARCH_K3

- default 0x4a000000 if ARCH_SUNXI && !MACH_SUN9I && !MACH_SUN8I_V3S

+ default 0x4a000000 if ARCH_SUNXI && !MACH_SUN9I && (!MACH_SUN8I_V3S || !MACH_SUN8I_S3)

default 0x2a000000 if ARCH_SUNXI && MACH_SUN9I

- default 0x42e00000 if ARCH_SUNXI && MACH_SUN8I_V3S

+ default 0x42e00000 if ARCH_SUNXI && (MACH_SUN8I_V3S || MACH_SUN8I_S3)

hex "Text Base"

help

The address in memory that U-Boot will be running from, initially.

diff --git a/arch/arm/dts/Makefile b/arch/arm/dts/Makefile

index bb979550c4..bbe1887623 100644

--- a/arch/arm/dts/Makefile

+++ b/arch/arm/dts/Makefile

@@ -546,7 +546,9 @@ dtb-$(CONFIG_MACH_SUN8I_R40) += \

sun8i-r40-bananapi-m2-ultra.dtb \

sun8i-v40-bananapi-m2-berry.dtb

dtb-$(CONFIG_MACH_SUN8I_V3S) += \

- sun8i-v3s-licheepi-zero.dtb

+ sun8i-v3s-licheepi-zero.dtb

+dtb-$(CONFIG_MACH_SUN8I_S3) += \

+ sun8i-s3-generic.dtb

dtb-$(CONFIG_MACH_SUN50I_H5) += \

sun50i-h5-bananapi-m2-plus.dtb \

sun50i-h5-emlid-neutis-n5-devboard.dtb \

diff --git a/arch/arm/dts/sun8i-s3-generic.dts b/arch/arm/dts/sun8i-s3-generic.dts

new file mode 100644

index 0000000000..c1aac3d5d4

--- /dev/null

+++ b/arch/arm/dts/sun8i-s3-generic.dts

@@ -0,0 +1,135 @@

+/*

+ * Copyright (C) 2020 Aodzip <aodzip@gmail.com>

+ *

+ * This file is dual-licensed: you can use it either under the terms

+ * of the GPL or the X11 license, at your option. Note that this dual

+ * licensing only applies to this file, and not this project as a

+ * whole.

+ *

+ * a) This file is free software; you can redistribute it and/or

+ * modify it under the terms of the GNU General Public License as

+ * published by the Free Software Foundation; either version 2 of the

+ * License, or (at your option) any later version.

+ *

+ * This file is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * Or, alternatively,

+ *

+ * b) Permission is hereby granted, free of charge, to any person

+ * obtaining a copy of this software and associated documentation

+ * files (the "Software"), to deal in the Software without

+ * restriction, including without limitation the rights to use,

+ * copy, modify, merge, publish, distribute, sublicense, and/or

+ * sell copies of the Software, and to permit persons to whom the

+ * Software is furnished to do so, subject to the following

+ * conditions:

+ *

+ * The above copyright notice and this permission notice shall be

+ * included in all copies or substantial portions of the Software.

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND,

+ * EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES

+ * OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND

+ * NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT

+ * HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

+ * WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING

+ * FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR

+ * OTHER DEALINGS IN THE SOFTWARE.

+ */

+

+/dts-v1/;

+#include "sun8i-s3.dtsi"

+#include "sunxi-common-regulators.dtsi"

+

+/ {

+ model = "Allwinner S3 Generic Device";

+ compatible = "allwinner,sun8i-s3";

+

+ aliases {

+ serial0 = &uart0;

+ };

+

+ chosen {

+ stdout-path = "serial0:115200n8";

+ };

+

+ backlight: backlight {

+ compatible = "pwm-backlight";

+ pwms = <&pwm 0 50000 0>;

+ brightness-levels = <0 2 4 8 16 32 64 128 255>;

+ default-brightness-level = <8>;

+ };

+

+ panel-rgb@0 {

+ compatible = "simple-panel";

+ backlight = <&backlight>;

+

+ display-timings {

+ timing@0 {

+ clock-frequency = <50000000>;

+ hactive = <480>;

+ vactive = <272>;

+ hfront-porch = <2>;

+ hback-porch = <2>;

+ hsync-len = <41>;

+ vfront-porch = <2>;

+ vback-porch = <2>;

+ vsync-len = <10>;

+ hsync-active = <0>;

+ vsync-active = <0>;

+ de-active = <0>;

+ pixelclk-active = <1>;

+ };

+ };

+ };

+};

+

+&emac {

+ phy-handle = <&int_mii_phy>;

+ phy-mode = "mii";

+ allwinner,use-internal-phy;

+ status = "okay";

+};

+

+&mmc0 {

+ bus-width = <4>;

+ status = "okay";

+};

+

+&mmc2 {

+ non-removable;

+ max-speed = <20000000>;

+ bus-width = <8>;

+ status = "okay";

+};

+

+&spi0 {

+ status = "disabled";

+};

+

+&uart0 {

+ status = "okay";

+};

+

+&usb_otg {

+ status = "okay";

+};

+

+&usbphy {

+ status = "okay";

+};

+

+&ehci0 {

+ status = "okay";

+};

+

+&ohci0 {

+ status = "okay";

+};

+

+&pwm {

+ status = "okay";

+};

diff --git a/arch/arm/dts/sun8i-s3.dtsi b/arch/arm/dts/sun8i-s3.dtsi

new file mode 100644

index 0000000000..282aadff11

--- /dev/null

+++ b/arch/arm/dts/sun8i-s3.dtsi

@@ -0,0 +1,157 @@

+/*

+ * Copyright (C) 2020 Aodzip <aodzip@gmail.com>

+ *

+ * This file is dual-licensed: you can use it either under the terms

+ * of the GPL or the X11 license, at your option. Note that this dual

+ * licensing only applies to this file, and not this project as a

+ * whole.

+ *

+ * a) This file is free software; you can redistribute it and/or

+ * modify it under the terms of the GNU General Public License as

+ * published by the Free Software Foundation; either version 2 of the

+ * License, or (at your option) any later version.

+ *

+ * This file is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * Or, alternatively,

+ *

+ * b) Permission is hereby granted, free of charge, to any person

+ * obtaining a copy of this software and associated documentation

+ * files (the "Software"), to deal in the Software without

+ * restriction, including without limitation the rights to use,

+ * copy, modify, merge, publish, distribute, sublicense, and/or

+ * sell copies of the Software, and to permit persons to whom the

+ * Software is furnished to do so, subject to the following

+ * conditions:

+ *

+ * The above copyright notice and this permission notice shall be

+ * included in all copies or substantial portions of the Software.

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND,

+ * EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES

+ * OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND

+ * NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT

+ * HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

+ * WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING

+ * FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR

+ * OTHER DEALINGS IN THE SOFTWARE.

+ */

+/dts-v1/;

+#include "sun8i-v3s.dtsi"

+#include "sunxi-common-regulators.dtsi"

+#include <dt-bindings/input/input.h>

+

+/ {

+ #address-cells = <1>;

+ #size-cells = <1>;

+ interrupt-parent = <&gic>;

+

+ soc {

+ compatible = "simple-bus";

+ #address-cells = <1>;

+ #size-cells = <1>;

+ ranges;

+

+ syscon: syscon@1c00000 {

+ compatible = "allwinner,sun8i-v3s-system-controller", "allwinner,sun8i-h3-system-control", "syscon";

+ reg = <0x01c00000 0x1000>;

+ };

+

+ emac: ethernet@1c30000 {

+ compatible = "allwinner,sun8i-h3-emac";

+ syscon = <&syscon>;

+ reg = <0x01c30000 0x10000>;

+ interrupts = <GIC_SPI 82 IRQ_TYPE_LEVEL_HIGH>;

+ interrupt-names = "macirq";

+ resets = <&ccu RST_BUS_EMAC>;

+ reset-names = "stmmaceth";

+ clocks = <&ccu CLK_BUS_EMAC>;

+ clock-names = "stmmaceth";

+ status = "disabled";

+

+ mdio: mdio {

+ #address-cells = <1>;

+ #size-cells = <0>;

+ compatible = "snps,dwmac-mdio";

+ };

+

+ mdio-mux {

+ compatible = "allwinner,sun8i-h3-mdio-mux";

+ #address-cells = <1>;

+ #size-cells = <0>;

+

+ mdio-parent-bus = <&mdio>;

+ /* Only one MDIO is usable at the time */

+ internal_mdio: mdio@1 {

+ compatible = "allwinner,sun8i-h3-mdio-internal";

+ reg = <1>;

+ #address-cells = <1>;

+ #size-cells = <0>;

+

+ int_mii_phy: ethernet-phy@1 {

+ compatible = "ethernet-phy-ieee802.3-c22";

+ reg = <1>;

+ clocks = <&ccu CLK_BUS_EPHY>;

+ resets = <&ccu RST_BUS_EPHY>;

+ };

+ };

+

+ external_mdio: mdio@2 {

+ reg = <2>;

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

+ };

+ };

+

+ ehci0: usb@01c1a000 {

+ compatible = "allwinner,sun8i-v3s-ehci", "generic-ehci";

+ reg = <0x01c1a000 0x100>;

+ interrupts = <GIC_SPI 72 IRQ_TYPE_LEVEL_HIGH>;

+ clocks = <&ccu CLK_BUS_EHCI0>, <&ccu CLK_BUS_OHCI0>;

+ resets = <&ccu RST_BUS_EHCI0>, <&ccu RST_BUS_OHCI0>;

+ status = "disabled";

+ };

+

+ ohci0: usb@01c1a400 {

+ compatible = "allwinner,sun8i-v3s-ohci", "generic-ohci";

+ reg = <0x01c1a400 0x100>;

+ interrupts = <GIC_SPI 73 IRQ_TYPE_LEVEL_HIGH>;

+ clocks = <&ccu CLK_BUS_EHCI0>, <&ccu CLK_BUS_OHCI0>, <&ccu CLK_USB_OHCI0>;

+ resets = <&ccu RST_BUS_EHCI0>, <&ccu RST_BUS_OHCI0>;

+ status = "disabled";

+ };

+

+ spi0: spi@1c68000 {

+ compatible = "allwinner,sun8i-h3-spi";

+ reg = <0x01c68000 0x1000>;

+ interrupts = <GIC_SPI 65 IRQ_TYPE_LEVEL_HIGH>;

+ clocks = <&ccu CLK_BUS_SPI0>, <&ccu CLK_SPI0>;

+ clock-names = "ahb", "mod";

+ resets = <&ccu RST_BUS_SPI0>;

+ status = "disabled";

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

+

+ pwm: pwm@1c21400 {

+ compatible = "allwinner,sun5i-a13-pwm";

+ reg = <0x01c21400 0x8>;

+ clocks = <&osc24M>;

+ #pwm-cells = <3>;

+ status = "disabled";

+ };

+ };

+};

+

+&usb_otg {

+ phys = <&usbphy>;

+ extcon = <&usbphy>;

+};

+

+&usbphy {

+ #phy-cells = <0>;

+};

diff --git a/arch/arm/include/asm/arch-sunxi/clock_sun6i.h b/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

index ee387127f3..8001a81b8f 100644

--- a/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

+++ b/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

@@ -333,9 +333,14 @@ struct sunxi_ccm_reg {

#define AHB_GATE_OFFSET_LCD1 5

#define AHB_GATE_OFFSET_LCD0 4

#else

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+#define AHB_GATE_OFFSET_LCD1 5

+#define AHB_GATE_OFFSET_LCD0 4

+#else

#define AHB_GATE_OFFSET_LCD1 4

#define AHB_GATE_OFFSET_LCD0 3

#endif

+#endif

#define CCM_NAND_CTRL_M(x) ((x) - 1)

#define CCM_NAND_CTRL_N(x) ((x) << 16)

@@ -480,9 +485,14 @@ struct sunxi_ccm_reg {

#define AHB_RESET_OFFSET_LCD1 5

#define AHB_RESET_OFFSET_LCD0 4

#else

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+#define AHB_RESET_OFFSET_LCD1 5

+#define AHB_RESET_OFFSET_LCD0 4

+#else

#define AHB_RESET_OFFSET_LCD1 4

#define AHB_RESET_OFFSET_LCD0 3

#endif

+#endif

/* ahb_reset2 offsets */

#define AHB_RESET_OFFSET_EPHY 2

@@ -508,7 +518,12 @@ struct sunxi_ccm_reg {

/* CCM bits common to all Display Engine 2.0 clock ctrl regs */

#define CCM_DE2_CTRL_M(n) ((((n) - 1) & 0xf) << 0)

#define CCM_DE2_CTRL_PLL_MASK (3 << 24)

+

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+#define CCM_DE2_CTRL_PLL6_2X (2 << 24)

+#else

#define CCM_DE2_CTRL_PLL6_2X (0 << 24)

+#endif

#define CCM_DE2_CTRL_PLL10 (1 << 24)

#define CCM_DE2_CTRL_GATE (0x1 << 31)

diff --git a/arch/arm/include/asm/arch-sunxi/display2.h b/arch/arm/include/asm/arch-sunxi/display2.h

index 7202d2756c..ad3a81dbde 100644

--- a/arch/arm/include/asm/arch-sunxi/display2.h

+++ b/arch/arm/include/asm/arch-sunxi/display2.h

@@ -137,4 +137,12 @@ struct de_csc {

#define SUNXI_DE2_WH(w, h) (((h - 1) << 16) | (w - 1))

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+ #define SUNXI_DE2_MUX_CHAN_SZ_COUNT 2

+ #define SUNXI_DE2_BLD_ROUTE 2

+#else

+ #define SUNXI_DE2_MUX_CHAN_SZ_COUNT 1

+ #define SUNXI_DE2_BLD_ROUTE 1

+#endif

+

#endif /* _SUNXI_DISPLAY2_H */

diff --git a/arch/arm/mach-sunxi/Kconfig b/arch/arm/mach-sunxi/Kconfig

index be0822bfb7..b7cb87a98f 100644

--- a/arch/arm/mach-sunxi/Kconfig

+++ b/arch/arm/mach-sunxi/Kconfig

@@ -262,7 +262,18 @@ config MACH_SUN8I_V3S

select SUNXI_DRAM_DW

select SUNXI_DRAM_DW_16BIT

select SUPPORT_SPL

- select ARMV7_BOOT_SEC_DEFAULT if OLD_SUNXI_KERNEL_COMPAT

+

+config MACH_SUN8I_S3

+ bool "sun8i (Allwinner S3)"

+ select CPU_V7A

+ select CPU_V7_HAS_NONSEC

+ select CPU_V7_HAS_VIRT

+ select ARCH_SUPPORT_PSCI

+ select SUNXI_GEN_SUN6I

+ select SUNXI_DRAM_DW

+ select SUNXI_DRAM_DW_16BIT

+ select SUPPORT_SPL

+ select SUNXI_DE2

config MACH_SUN9I

bool "sun9i (Allwinner A80)"

@@ -321,6 +332,7 @@ config MACH_SUN8I

default y if MACH_SUNXI_H3_H5

default y if MACH_SUN8I_R40

default y if MACH_SUN8I_V3S

+ default y if MACH_SUN8I_S3

config RESERVE_ALLWINNER_BOOT0_HEADER

bool "reserve space for Allwinner boot0 header"

@@ -437,7 +449,7 @@ config DRAM_ZQ

default 123 if MACH_SUN4I || MACH_SUN5I || MACH_SUN6I || \

MACH_SUN8I_A23 || MACH_SUN8I_A33 || MACH_SUN8I_A83T

default 127 if MACH_SUN7I

- default 14779 if MACH_SUN8I_V3S

+ default 14779 if MACH_SUN8I_V3S || MACH_SUN8I_S3

default 3881979 if MACH_SUNXI_H3_H5 || MACH_SUN8I_R40 || MACH_SUN50I_H6

default 4145117 if MACH_SUN9I

default 3881915 if MACH_SUN50I

@@ -755,6 +767,7 @@ config VIDEO_SUNXI

depends on !MACH_SUNXI_H3_H5

depends on !MACH_SUN8I_R40

depends on !MACH_SUN8I_V3S

+ depends on !MACH_SUN8I_S3

depends on !MACH_SUN9I

depends on !MACH_SUN50I

depends on !MACH_SUN50I_H6

diff --git a/arch/arm/mach-sunxi/board.c b/arch/arm/mach-sunxi/board.c

index b487b265af..6aa28bbc3c 100644

--- a/arch/arm/mach-sunxi/board.c

+++ b/arch/arm/mach-sunxi/board.c

@@ -117,7 +117,7 @@ static int gpio_init(void)

sunxi_gpio_set_cfgpin(SUNXI_GPB(9), SUN8I_A83T_GPB_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPB(10), SUN8I_A83T_GPB_UART0);

sunxi_gpio_set_pull(SUNXI_GPB(10), SUNXI_GPIO_PULL_UP);

-#elif CONFIG_CONS_INDEX == 1 && defined(CONFIG_MACH_SUN8I_V3S)

+#elif CONFIG_CONS_INDEX == 1 && (defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3))

sunxi_gpio_set_cfgpin(SUNXI_GPB(8), SUN8I_V3S_GPB_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPB(9), SUN8I_V3S_GPB_UART0);

sunxi_gpio_set_pull(SUNXI_GPB(9), SUNXI_GPIO_PULL_UP);

diff --git a/arch/arm/mach-sunxi/cpu_info.c b/arch/arm/mach-sunxi/cpu_info.c

index ae4745bfec..060fbfc8a9 100644

--- a/arch/arm/mach-sunxi/cpu_info.c

+++ b/arch/arm/mach-sunxi/cpu_info.c

@@ -90,6 +90,8 @@ int print_cpuinfo(void)

printf("CPU: Allwinner R40 (SUN8I %04x)\n", sunxi_get_sram_id());

#elif defined CONFIG_MACH_SUN8I_V3S

printf("CPU: Allwinner V3s (SUN8I %04x)\n", sunxi_get_sram_id());

+#elif defined CONFIG_MACH_SUN8I_S3

+ printf("CPU: Allwinner S3 (SUN8I %04x)\n", sunxi_get_sram_id());

#elif defined CONFIG_MACH_SUN9I

puts("CPU: Allwinner A80 (SUN9I)\n");

#elif defined CONFIG_MACH_SUN50I

diff --git a/arch/arm/mach-sunxi/dram_sunxi_dw.c b/arch/arm/mach-sunxi/dram_sunxi_dw.c

index 85e7a1874e..43db624d8b 100644

--- a/arch/arm/mach-sunxi/dram_sunxi_dw.c

+++ b/arch/arm/mach-sunxi/dram_sunxi_dw.c

@@ -727,6 +727,9 @@ unsigned long sunxi_dram_init(void)

#elif defined(CONFIG_MACH_SUN8I_V3S)

/* TODO: set delays and mbus priority for V3s */

uint16_t socid = SOCID_H3;

+#elif defined(CONFIG_MACH_SUN8I_S3)

+ /* TODO: set delays and mbus priority for S3 */

+ uint16_t socid = SOCID_H3;

#elif defined(CONFIG_MACH_SUN50I)

uint16_t socid = SOCID_A64;

#elif defined(CONFIG_MACH_SUN50I_H5)

diff --git a/board/sunxi/board.c b/board/sunxi/board.c

index 6afea6ef42..769530412b 100644

--- a/board/sunxi/board.c

+++ b/board/sunxi/board.c

@@ -40,6 +40,7 @@

#include <spl.h>

#include <sy8106a.h>

#include <asm/setup.h>

+#include <splash.h>

#if defined CONFIG_VIDEO_LCD_PANEL_I2C && !(defined CONFIG_SPL_BUILD)

/* So that we can use pin names in Kconfig and sunxi_name_to_gpio() */

@@ -501,6 +502,13 @@ static void mmc_pinmux_setup(int sdc)

sunxi_gpio_set_pull(SUNXI_GPC(24), SUNXI_GPIO_PULL_UP);

sunxi_gpio_set_drv(SUNXI_GPC(24), 2);

#elif defined(CONFIG_MACH_SUN8I) || defined(CONFIG_MACH_SUN50I)

+#ifdef CONFIG_MACH_SUN8I_S3

+ for (pin = SUNXI_GPC(0); pin <= SUNXI_GPC(10); pin++) {

+ sunxi_gpio_set_cfgpin(pin, 2);

+ sunxi_gpio_set_pull(pin, SUNXI_GPIO_PULL_UP);

+ sunxi_gpio_set_drv(pin, 2);

+ }

+#else

/* SDC2: PC5-PC6, PC8-PC16 */

for (pin = SUNXI_GPC(5); pin <= SUNXI_GPC(6); pin++) {

sunxi_gpio_set_cfgpin(pin, SUNXI_GPC_SDC2);

@@ -513,6 +521,7 @@ static void mmc_pinmux_setup(int sdc)

sunxi_gpio_set_pull(pin, SUNXI_GPIO_PULL_UP);

sunxi_gpio_set_drv(pin, 2);

}

+#endif

#elif defined(CONFIG_MACH_SUN50I_H6)

/* SDC2: PC4-PC14 */

for (pin = SUNXI_GPC(4); pin <= SUNXI_GPC(14); pin++) {

@@ -916,3 +925,41 @@ int board_fit_config_name_match(const char *name)

return strcmp(name, cmp_str);

}

#endif

+

+#ifdef CONFIG_SPLASH_SCREEN

+static struct splash_location sunxi_splash_locations[] = {

+ {

+ .name = "mmc0_fs",

+ .storage = SPLASH_STORAGE_MMC,

+ .flags = SPLASH_STORAGE_FS,

+ .devpart = "0:1",

+ },

+ {

+ .name = "mmc1_fs",

+ .storage = SPLASH_STORAGE_MMC,

+ .flags = SPLASH_STORAGE_FS,

+ .devpart = "1:1",

+ },

+};

+

+int splash_screen_prepare(void)

+{

+ return splash_source_load(sunxi_splash_locations,

+ ARRAY_SIZE(sunxi_splash_locations));

+}

+

+int initr_env_dynamic_default(void)

+{

+ uint boot = sunxi_get_boot_device();

+ switch (boot) {

+ case BOOT_DEVICE_MMC1:

+ env_set("splashsource", "mmc0_fs");

+ break;

+ case BOOT_DEVICE_MMC2:

+ env_set("splashsource", "mmc1_fs");

+ break;

+ }

+ return 0;

+}

+

+#endif

diff --git a/common/board_r.c b/common/board_r.c

index 0bbeaa7594..949169895d 100644

--- a/common/board_r.c

+++ b/common/board_r.c

@@ -777,6 +777,9 @@ static init_fnc_t init_sequence_r[] = {

initr_mmc,

#endif

initr_env,

+#ifdef CONFIG_ENV_DYNAMIC_DEFAULT

+ initr_env_dynamic_default,

+#endif

#ifdef CONFIG_SYS_BOOTPARAMS_LEN

initr_malloc_bootparams,

#endif

diff --git a/configs/allwinner_s3_generic_defconfig b/configs/allwinner_s3_generic_defconfig

new file mode 100644

index 0000000000..2c368215ed

--- /dev/null

+++ b/configs/allwinner_s3_generic_defconfig

@@ -0,0 +1,54 @@

+CONFIG_ARM=y

+CONFIG_ARCH_SUNXI=y

+CONFIG_MACH_SUN8I_S3=y

+

+CONFIG_DEFAULT_DEVICE_TREE="sun8i-s3-generic"

+CONFIG_SPL=y

+CONFIG_CMD_BOOTMENU=y

+CONFIG_CMD_MEMINFO=y

+CONFIG_BOOTDELAY=0

+

+CONFIG_NETDEVICES=y

+CONFIG_SUN8I_EMAC=y

+CONFIG_NET_RANDOM_ETHADDR=y

+

+CONFIG_DM_SPI=y

+CONFIG_SUNXI_SPI=y

+

+CONFIG_MMC=y

+CONFIG_MMC_SUNXI_SLOT_EXTRA=2

+CONFIG_MMC0_CD_PIN="PF6"

+

+CONFIG_CMD_BMP=y

+CONFIG_VIDEO_BPP8=y

+CONFIG_VIDEO_SIMPLE=y

+CONFIG_VIDEO_DT_SIMPLEFB=y

+

+CONFIG_DM_REGULATOR=y

+CONFIG_REGULATOR_PWM=y

+CONFIG_DM_PWM=y

+CONFIG_PWM_SUNXI=y

+CONFIG_BACKLIGHT_PWM=y

+

+CONFIG_USB_GADGET_VBUS_DRAW=250

+

+CONFIG_USB_MUSB_GADGET=y

+CONFIG_USB_MUSB_SUNXI=y

+CONFIG_USB_MUSB_DISABLE_BULK_COMBINE_SPLIT=y

+CONFIG_USB_MUSB_PIO_ONLY=y

+CONFIG_USB_STORAGE=y

+

+CONFIG_PHY=y

+CONFIG_PHY_SUN4I_USB=y

+

+CONFIG_USB_EHCI_HCD=y

+CONFIG_USB_EHCI_GENERIC=y

+CONFIG_USB_OHCI_HCD=y

+CONFIG_USB_OHCI_GENERIC=y

+

+CONFIG_CMD_USB_MASS_STORAGE=y

+

+CONFIG_CMD_FASTBOOT=y

+CONFIG_FASTBOOT_FLASH_MMC=y

+CONFIG_FASTBOOT_FLASH_MMC_DEV=1

+CONFIG_FASTBOOT_CMD_OEM_FORMAT=y

diff --git a/drivers/clk/sunxi/Kconfig b/drivers/clk/sunxi/Kconfig

index 5ff101b993..c48717bbbc 100644

--- a/drivers/clk/sunxi/Kconfig

+++ b/drivers/clk/sunxi/Kconfig

@@ -52,11 +52,11 @@ config CLK_SUN8I_R40

on Allwinner R40 SoC.

config CLK_SUN8I_V3S

- bool "Clock driver for Allwinner V3S"

- default MACH_SUN8I_V3S

+ bool "Clock driver for Allwinner V3S/S3"

+ default MACH_SUN8I_V3S || MACH_SUN8I_S3

help

This enables common clock driver support for platforms based

- on Allwinner V3S SoC.

+ on Allwinner V3S/S3 SoC.

config CLK_SUN9I_A80

bool "Clock driver for Allwinner A80"

diff --git a/drivers/clk/sunxi/clk_v3s.c b/drivers/clk/sunxi/clk_v3s.c

index 789ac72026..2101efd11f 100644

--- a/drivers/clk/sunxi/clk_v3s.c

+++ b/drivers/clk/sunxi/clk_v3s.c

@@ -16,16 +16,22 @@ static struct ccu_clk_gate v3s_gates[] = {

[CLK_BUS_MMC0] = GATE(0x060, BIT(8)),

[CLK_BUS_MMC1] = GATE(0x060, BIT(9)),

[CLK_BUS_MMC2] = GATE(0x060, BIT(10)),

+ [CLK_BUS_EMAC] = GATE(0x060, BIT(17)),

[CLK_BUS_SPI0] = GATE(0x060, BIT(20)),

[CLK_BUS_OTG] = GATE(0x060, BIT(24)),

+ [CLK_BUS_EHCI0] = GATE(0x060, BIT(26)),

+ [CLK_BUS_OHCI0] = GATE(0x060, BIT(29)),

[CLK_BUS_UART0] = GATE(0x06c, BIT(16)),

[CLK_BUS_UART1] = GATE(0x06c, BIT(17)),

[CLK_BUS_UART2] = GATE(0x06c, BIT(18)),

+ [CLK_BUS_EPHY] = GATE(0x070, BIT(0)),

+

[CLK_SPI0] = GATE(0x0a0, BIT(31)),

- [CLK_USB_PHY0] = GATE(0x0cc, BIT(8)),

+ [CLK_USB_PHY0] = GATE(0x0cc, BIT(8)),

+ [CLK_USB_OHCI0] = GATE(0x0cc, BIT(16)),

};

static struct ccu_reset v3s_resets[] = {

@@ -34,8 +40,13 @@ static struct ccu_reset v3s_resets[] = {

[RST_BUS_MMC0] = RESET(0x2c0, BIT(8)),

[RST_BUS_MMC1] = RESET(0x2c0, BIT(9)),

[RST_BUS_MMC2] = RESET(0x2c0, BIT(10)),

+ [RST_BUS_EMAC] = RESET(0x2c0, BIT(17)),

[RST_BUS_SPI0] = RESET(0x2c0, BIT(20)),

[RST_BUS_OTG] = RESET(0x2c0, BIT(24)),

+ [RST_BUS_EHCI0] = RESET(0x2c0, BIT(26)),

+ [RST_BUS_OHCI0] = RESET(0x2c0, BIT(29)),

+

+ [RST_BUS_EPHY] = RESET(0x2c8, BIT(2)),

[RST_BUS_UART0] = RESET(0x2d8, BIT(16)),

[RST_BUS_UART1] = RESET(0x2d8, BIT(17)),

diff --git a/drivers/mmc/sunxi_mmc.c b/drivers/mmc/sunxi_mmc.c

index 9f426661c4..20a622dd2e 100644

--- a/drivers/mmc/sunxi_mmc.c

+++ b/drivers/mmc/sunxi_mmc.c

@@ -628,7 +628,7 @@ static int sunxi_mmc_probe(struct udevice *dev)

cfg->b_max = CONFIG_SYS_MMC_MAX_BLK_COUNT;

cfg->f_min = 400000;

- cfg->f_max = 52000000;

+ cfg->f_max = dev_read_u32_default(dev, "max-speed", 52000000);

priv->reg = (void *)dev_read_addr(dev);

priv->variant =

diff --git a/drivers/pwm/sunxi_pwm.c b/drivers/pwm/sunxi_pwm.c

index 8a55e4f461..154a5290ce 100644

--- a/drivers/pwm/sunxi_pwm.c

+++ b/drivers/pwm/sunxi_pwm.c

@@ -47,6 +47,9 @@ static int sunxi_pwm_config_pinmux(void)

{

#ifdef CONFIG_MACH_SUN50I

sunxi_gpio_set_cfgpin(SUNXI_GPD(22), SUNXI_GPD_PWM);

+#endif

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+ sunxi_gpio_set_cfgpin(SUNXI_GPB(4), SUN4I_GPB_PWM);

#endif

return 0;

}

diff --git a/drivers/usb/musb-new/musb_core.c b/drivers/usb/musb-new/musb_core.c

index f678aa4826..2574a6fd4b 100644

--- a/drivers/usb/musb-new/musb_core.c

+++ b/drivers/usb/musb-new/musb_core.c

@@ -1875,6 +1875,7 @@ allocate_instance(struct device *dev,

musb->controller = dev;

+ musb->dyn_fifo = config->dyn_fifo;

return musb;

}

diff --git a/drivers/video/sunxi/sunxi_de2.c b/drivers/video/sunxi/sunxi_de2.c

index 8333ddc44c..13be7a11e0 100644

--- a/drivers/video/sunxi/sunxi_de2.c

+++ b/drivers/video/sunxi/sunxi_de2.c

@@ -23,12 +23,21 @@

DECLARE_GLOBAL_DATA_PTR;

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+enum {

+ /* Maximum LCD size we support */

+ LCD_MAX_WIDTH = 1024,

+ LCD_MAX_HEIGHT = 768,

+ LCD_MAX_LOG2_BPP = VIDEO_BPP32,

+};

+#else

enum {

/* Maximum LCD size we support */

LCD_MAX_WIDTH = 3840,

LCD_MAX_HEIGHT = 2160,

LCD_MAX_LOG2_BPP = VIDEO_BPP32,

};

+#endif

static void sunxi_de2_composer_init(void)

{

@@ -43,13 +52,19 @@ static void sunxi_de2_composer_init(void)

reg_value &= ~(0x01 << 24);

writel(reg_value, SUNXI_SRAMC_BASE + 0x04);

#endif

-

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+ unsigned int hz = 300000000;

+ int pll = clock_get_pll6() * 2;

+ int div = 1;

+ while ((pll / div) > hz)

+ div++;

+ writel(CCM_DE2_CTRL_GATE | CCM_DE2_CTRL_PLL6_2X | CCM_DE2_CTRL_M(div), &ccm->de_clk_cfg);

+#else

clock_set_pll10(432000000);

-

/* Set DE parent to pll10 */

clrsetbits_le32(&ccm->de_clk_cfg, CCM_DE2_CTRL_PLL_MASK,

CCM_DE2_CTRL_PLL10);

-

+#endif

/* Set ahb gating to pass */

setbits_le32(&ccm->ahb_reset1_cfg, 1 << AHB_RESET_OFFSET_DE);

setbits_le32(&ccm->ahb_gate1, 1 << AHB_GATE_OFFSET_DE);

@@ -74,14 +89,13 @@ static void sunxi_de2_mode_set(int mux, const struct display_timing *mode,

struct de_ui * const de_ui_regs =

(struct de_ui *)(de_mux_base +

SUNXI_DE2_MUX_CHAN_REGS +

- SUNXI_DE2_MUX_CHAN_SZ * 1);

+ SUNXI_DE2_MUX_CHAN_SZ * SUNXI_DE2_MUX_CHAN_SZ_COUNT);

struct de_csc * const de_csc_regs =

(struct de_csc *)(de_mux_base +

SUNXI_DE2_MUX_DCSC_REGS);

u32 size = SUNXI_DE2_WH(mode->hactive.typ, mode->vactive.typ);

int channel;

u32 format;

-

/* enable clock */

#ifdef CONFIG_MACH_SUN8I_H3

setbits_le32(&de_clk_regs->rst_cfg, (mux == 0) ? 1 : 4);

@@ -108,13 +122,12 @@ static void sunxi_de2_mode_set(int mux, const struct display_timing *mode,

writel(0x00000101, &de_bld_regs->fcolor_ctl);

- writel(1, &de_bld_regs->route);

+ writel(SUNXI_DE2_BLD_ROUTE, &de_bld_regs->route);

writel(0, &de_bld_regs->premultiply);

writel(0xff000000, &de_bld_regs->bkcolor);

writel(0x03010301, &de_bld_regs->bld_mode[0]);

-

writel(size, &de_bld_regs->output_size);

writel(mode->flags & DISPLAY_FLAGS_INTERLACED ? 2 : 0,

&de_bld_regs->out_ctl);

diff --git a/drivers/video/sunxi/sunxi_dw_hdmi.c b/drivers/video/sunxi/sunxi_dw_hdmi.c

index c87c919a52..949b41732e 100644

--- a/drivers/video/sunxi/sunxi_dw_hdmi.c

+++ b/drivers/video/sunxi/sunxi_dw_hdmi.c

@@ -395,6 +395,8 @@ U_BOOT_DRIVER(sunxi_dw_hdmi) = {

.priv_auto_alloc_size = sizeof(struct sunxi_dw_hdmi_priv),

};

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

U_BOOT_DEVICE(sunxi_dw_hdmi) = {

.name = "sunxi_dw_hdmi"

};

+#endif

diff --git a/drivers/video/sunxi/sunxi_lcd.c b/drivers/video/sunxi/sunxi_lcd.c

index 619f5892f5..bc0a782a1c 100644

--- a/drivers/video/sunxi/sunxi_lcd.c

+++ b/drivers/video/sunxi/sunxi_lcd.c

@@ -24,7 +24,7 @@ struct sunxi_lcd_priv {

static void sunxi_lcdc_config_pinmux(void)

{

-#ifdef CONFIG_MACH_SUN50I

+#if defined(CONFIG_MACH_SUN50I) || defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

int pin;

for (pin = SUNXI_GPD(0); pin <= SUNXI_GPD(21); pin++) {

@@ -144,7 +144,7 @@ U_BOOT_DRIVER(sunxi_lcd) = {

.priv_auto_alloc_size = sizeof(struct sunxi_lcd_priv),

};

-#ifdef CONFIG_MACH_SUN50I

+#if defined(CONFIG_MACH_SUN50I) || defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

U_BOOT_DEVICE(sunxi_lcd) = {

.name = "sunxi_lcd"

};

diff --git a/include/configs/sunxi-common.h b/include/configs/sunxi-common.h

index 0ef289fd64..da3080cc32 100644

--- a/include/configs/sunxi-common.h

+++ b/include/configs/sunxi-common.h

@@ -144,12 +144,12 @@

#define CONFIG_SYS_MMC_MAX_DEVICE 4

#endif

-#ifndef CONFIG_MACH_SUN8I_V3S

-/* 64MB of malloc() pool */

-#define CONFIG_SYS_MALLOC_LEN (CONFIG_ENV_SIZE + (64 << 20))

-#else

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

/* 2MB of malloc() pool */

#define CONFIG_SYS_MALLOC_LEN (CONFIG_ENV_SIZE + (2 << 20))

+#else

+/* 64MB of malloc() pool */

+#define CONFIG_SYS_MALLOC_LEN (CONFIG_ENV_SIZE + (64 << 20))

#endif

/*

@@ -301,19 +301,8 @@ extern int soft_i2c_gpio_scl;

#define RAMDISK_ADDR_R __stringify(SDRAM_OFFSET(FE00000))

#else

-/*

- * 160M RAM (256M minimum minus 64MB heap + 32MB for u-boot, stack, fb, etc.

- * 32M uncompressed kernel, 16M compressed kernel, 1M fdt,

- * 1M script, 1M pxe and the ramdisk at the end.

- */

-#ifndef CONFIG_MACH_SUN8I_V3S

-#define BOOTM_SIZE __stringify(0xa000000)

-#define KERNEL_ADDR_R __stringify(SDRAM_OFFSET(2000000))

-#define FDT_ADDR_R __stringify(SDRAM_OFFSET(3000000))

-#define SCRIPT_ADDR_R __stringify(SDRAM_OFFSET(3100000))

-#define PXEFILE_ADDR_R __stringify(SDRAM_OFFSET(3200000))

-#define RAMDISK_ADDR_R __stringify(SDRAM_OFFSET(3300000))

-#else

+

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

/*

* 64M RAM minus 2MB heap + 16MB for u-boot, stack, fb, etc.

* 16M uncompressed kernel, 8M compressed kernel, 1M fdt,

@@ -325,6 +314,18 @@ extern int soft_i2c_gpio_scl;

#define SCRIPT_ADDR_R __stringify(SDRAM_OFFSET(1900000))

#define PXEFILE_ADDR_R __stringify(SDRAM_OFFSET(1A00000))

#define RAMDISK_ADDR_R __stringify(SDRAM_OFFSET(1B00000))

+#else

+/*

+ * 160M RAM (256M minimum minus 64MB heap + 32MB for u-boot, stack, fb, etc.

+ * 32M uncompressed kernel, 16M compressed kernel, 1M fdt,

+ * 1M script, 1M pxe and the ramdisk at the end.

+ */

+#define BOOTM_SIZE __stringify(0xa000000)

+#define KERNEL_ADDR_R __stringify(SDRAM_OFFSET(2000000))

+#define FDT_ADDR_R __stringify(SDRAM_OFFSET(3000000))

+#define SCRIPT_ADDR_R __stringify(SDRAM_OFFSET(3100000))

+#define PXEFILE_ADDR_R __stringify(SDRAM_OFFSET(3200000))

+#define RAMDISK_ADDR_R __stringify(SDRAM_OFFSET(3300000))

#endif

#endif

@@ -427,6 +428,14 @@ extern int soft_i2c_gpio_scl;

#include <config_distro_bootcmd.h>

+#ifdef CONFIG_CMD_FASTBOOT

+#define FASTBOOT_SETTINGS \

+ "boot_targets=fel mmc_auto usb0 fastboot\0" \

+ "bootcmd_fastboot=fastboot usb 0\0"

+#else

+#define FASTBOOT_SETTINGS

+#endif

+

#ifdef CONFIG_USB_KEYBOARD

#define CONSOLE_STDIN_SETTINGS \

"preboot=usb start\0" \

@@ -436,11 +445,25 @@ extern int soft_i2c_gpio_scl;

"stdin=serial\0"

#endif

+#ifdef CONFIG_DM_VIDEO

+#define CONFIG_VIDEO_BMP_RLE8

+#define CONFIG_BMP_16BPP

+#define CONFIG_BMP_24BPP

+#define CONFIG_BMP_32BPP

+#define CONFIG_SPLASH_SCREEN

+#define CONFIG_SPLASH_SOURCE

+#define SPLASHIMAGE_ENV_SETTINGS "splashimage=" __stringify(SDRAM_OFFSET(2000000)) "\0"

+#define CONFIG_ENV_DYNAMIC_DEFAULT

+#else

+#define SPLASHIMAGE_ENV_SETTINGS

+#endif

+

#ifdef CONFIG_VIDEO

#define CONSOLE_STDOUT_SETTINGS \

"stdout=serial,vga\0" \

"stderr=serial,vga\0"

-#elif CONFIG_DM_VIDEO

+#else

+#if CONFIG_DM_VIDEO && !defined(CONFIG_SPLASH_SCREEN)

#define CONSOLE_STDOUT_SETTINGS \

"stdout=serial,vidconsole\0" \

"stderr=serial,vidconsole\0"

@@ -449,6 +472,7 @@ extern int soft_i2c_gpio_scl;

"stdout=serial\0" \

"stderr=serial\0"

#endif

+#endif

#ifdef CONFIG_MTDIDS_DEFAULT

#define SUNXI_MTDIDS_DEFAULT \

@@ -464,11 +488,18 @@ extern int soft_i2c_gpio_scl;

#define SUNXI_MTDPARTS_DEFAULT

#endif

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+#define PARTS_DEFAULT \

+ "name=loader,start=8k,size=1024k;" \

+ "name=esp,size=16M,bootable,uuid=${uuid_gpt_esp};" \

+ "name=system,size=-,uuid=${uuid_gpt_system};"

+#else

#define PARTS_DEFAULT \

"name=loader1,start=8k,size=32k,uuid=${uuid_gpt_loader1};" \

"name=loader2,size=984k,uuid=${uuid_gpt_loader2};" \

"name=esp,size=128M,bootable,uuid=${uuid_gpt_esp};" \

"name=system,size=-,uuid=${uuid_gpt_system};"

+#endif

#define UUID_GPT_ESP "c12a7328-f81f-11d2-ba4b-00a0c93ec93b"

@@ -490,6 +521,7 @@ extern int soft_i2c_gpio_scl;

#define CONFIG_EXTRA_ENV_SETTINGS \

CONSOLE_ENV_SETTINGS \

+ SPLASHIMAGE_ENV_SETTINGS \

MEM_LAYOUT_ENV_SETTINGS \

DFU_ALT_INFO_RAM \

"fdtfile=" FDTFILE "\0" \

@@ -500,10 +532,12 @@ extern int soft_i2c_gpio_scl;

"uuid_gpt_system=" UUID_GPT_SYSTEM "\0" \

"partitions=" PARTS_DEFAULT "\0" \

BOOTCMD_SUNXI_COMPAT \

- BOOTENV

+ BOOTENV \

+ FASTBOOT_SETTINGS

#else /* ifndef CONFIG_SPL_BUILD */

#define CONFIG_EXTRA_ENV_SETTINGS

#endif

#endif /* _SUNXI_COMMON_CONFIG_H */

+

diff --git a/include/init.h b/include/init.h

index 2a33a3fd1e..95bb92f51c 100644

--- a/include/init.h

+++ b/include/init.h

@@ -203,6 +203,7 @@ int update_flash_size(int flash_size);

int arch_early_init_r(void);

void pci_init(void);

int misc_init_r(void);

+int initr_env_dynamic_default(void);

#if defined(CONFIG_VID)

int init_func_vid(void);

#endif

diff --git a/scripts/config_whitelist.txt b/scripts/config_whitelist.txt

index 6908431d03..b3414bb3a0 100644

--- a/scripts/config_whitelist.txt

+++ b/scripts/config_whitelist.txt

@@ -426,6 +426,7 @@ CONFIG_ENV_ADDR_FLEX

CONFIG_ENV_CALLBACK_LIST_DEFAULT

CONFIG_ENV_CALLBACK_LIST_STATIC

CONFIG_ENV_COMMON_BOOT

+CONFIG_ENV_DYNAMIC_DEFAULT

CONFIG_ENV_EEPROM_IS_ON_I2C

CONFIG_ENV_FLAGS_LIST_DEFAULT

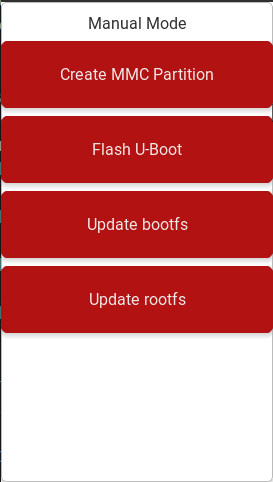

CONFIG_ENV_FLAGS_LIST_STATIC#79 全志 SOC » [刷机工具] 发个带GUI支持触屏的卡刷小程序 » 2020-04-09 14:44:06

- aodzip

- 回复: 1

https://github.com/aodzip/AWFlashTool

东西全在代码里了,记得看看Makefile | Config.h | lv_conf.h | lv_drv_conf.h

make -j8 #编译

make flash #帮你写到刷好buildroot的卡里

如触摸无操作,5秒后自动全来一遍

如果触摸任意位置,则停止倒计时,可以手动选择操作

TF卡的第一个分区(FAT32分区)中

依照如下结构创建images文件夹

.

├── bootfs.tar

├── rootfs.tar

└── u-boot-sunxi-with-spl.bin

u-boot-sunxi-with-spl.bin 将被刷入uboot启动位置

bootfs.tar 将被用于填充启动分区

rootfs.tar 将被用于填充系统分区

#80 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » MT7601u rx urb failed: -71 解决方案 » 2020-04-09 09:59:09

- aodzip

- 回复: 2

典型症状如下

[ 85.238760] usb 1-1.4: new high-speed USB device number 35 using ehci-platform

[ 85.418843] usb 1-1.4: New USB device found, idVendor=148f, idProduct=7601, bcdDevice= 0.00

[ 85.427206] usb 1-1.4: New USB device strings: Mfr=1, Product=2, SerialNumber=3

[ 85.434540] usb 1-1.4: Product: 802.11 n WLAN

[ 85.438909] usb 1-1.4: SerialNumber: 1.0

[ 85.658773] usb 1-1.4: reset high-speed USB device number 35 using ehci-platform

[ 85.711960] mt7601u 1-1.4:1.0: ASIC revision: 76010001 MAC revision: 76010500

[ 85.720941] mt7601u 1-1.4:1.0: Firmware Version: 0.1.00 Build: 7640 Build time: 201302052146____

[ 86.167971] mt7601u 1-1.4:1.0: EEPROM ver:0c fae:00

[ 86.366367] mt7601u 1-1.4:1.0: rx urb failed: -71

[ 86.371220] mt7601u 1-1.4:1.0: Error: MCU resp urb failed:-71

[ 86.376970] mt7601u 1-1.4:1.0: Error: MCU resp evt:0 seq:5-4!

[ 86.386490] mt7601u 1-1.4:1.0: rx urb failed: -71

[ 86.391620] mt7601u 1-1.4:1.0: Error: MCU resp urb failed:-71

[ 86.397381] mt7601u 1-1.4:1.0: Error: MCU resp evt:0 seq:5-4!

[ 86.406739] mt7601u 1-1.4:1.0: rx urb failed: -71

[ 86.411822] mt7601u 1-1.4:1.0: Error: MCU resp urb failed:-71

[ 86.417575] mt7601u 1-1.4:1.0: Error: MCU resp evt:0 seq:5-4!

[ 86.426855] mt7601u 1-1.4:1.0: rx urb failed: -71

[ 86.431907] mt7601u 1-1.4:1.0: Error: MCU resp urb failed:-71

[ 86.437675] mt7601u 1-1.4:1.0: Error: MCU resp evt:0 seq:5-4!

[ 86.446980] mt7601u 1-1.4:1.0: rx urb failed: -71

[ 86.452029] mt7601u 1-1.4:1.0: Error: MCU resp urb failed:-71

[ 86.457789] mt7601u 1-1.4:1.0: Error: MCU resp evt:0 seq:5-4!

[ 86.463589] mt7601u 1-1.4:1.0: Error: mt7601u_mcu_wait_resp timed out

[ 86.778760] mt7601u 1-1.4:1.0: Vendor request req:07 off:0080 failed:-71

[ 87.088761] mt7601u 1-1.4:1.0: Vendor request req:02 off:0080 failed:-71

[ 87.398756] mt7601u 1-1.4:1.0: Vendor request req:02 off:0080 failed:-71

[ 87.405586] mt7601u: probe of 1-1.4:1.0 failed with error -110

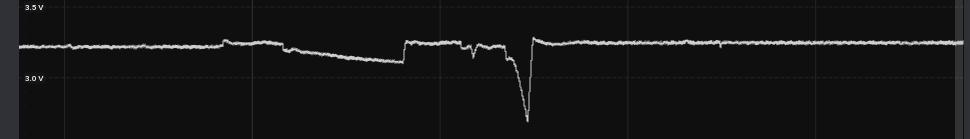

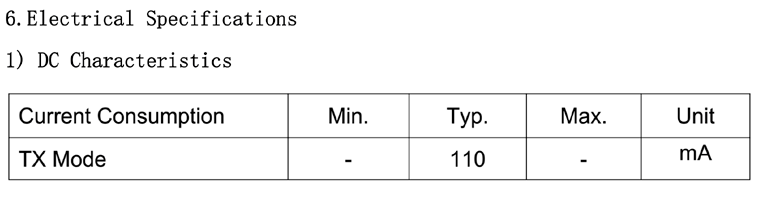

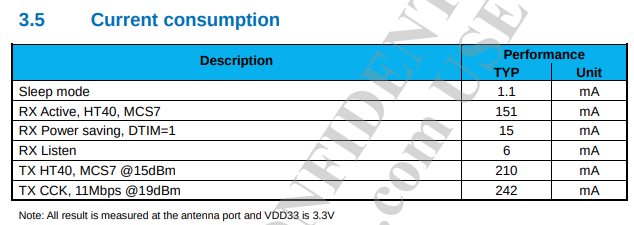

[ 87.420875] usb 1-1.4: USB disconnect, device number 35解决方案

我跟你讲这芯片超耗电的

模块厂商会说这模块典型耗电110mA,相信的话就GG

来看看MTK怎么说的

加电容也许不是最好的办法,但是能稍微缓解(470uF)

还是换更好的供电吧,小LDO基本都秒杀了,按300mA的典型值设计吧

#81 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 谁知道 Reuuimlla Technology Co., Ltd. 的前后来历 » 2020-04-05 16:40:33

- aodzip

- 回复: 3

今天在看某BSP源码的时候发现了这么一个神秘的公司

https://www.reuuimllatech.com/

我TM都要笑死了,了解的大佬快给我讲讲

#83 Re: 全志 SOC » Allwinner S3 uboot 2020.01 (LCD + 以太网 + USB 挂载 + FastBoot + SDC 2) 不开源 » 2020-04-03 18:58:20

#84 全志 SOC » Allwinner S3 uboot 2020.01 (LCD + 以太网 + USB 挂载 + FastBoot + SDC 2) 不开源 » 2020-04-03 14:56:24

- aodzip

- 回复: 15

Allwinner S3上接近完整的uboot 2020.01体验

支持480*272 RGB屏幕初始化,秒出开机图像,支持PWM0调光

支持以太网,TFTP/PXE相关的指令

支持USB挂载MMC0 或 MMC1 ,直接烧写Flash

支持USB挂载fastboot协议刷机指令

支持根据开机存储器自动修改bootarg,固化烧录不需要更改boot.scr或默认开机指令

boot.cmd转换成boot.scr

转换了才能用哦

mkimage -C none -A arm -T script -d boot.cmd boot.scr#87 全志 SOC » Allwinner S3 Ubuntu Minimal 18.04.4 LTS 镜像 » 2020-03-13 15:59:37

- aodzip

- 回复: 10

HOWTO:

1. buildroot 编译好

uboot 2020.01了解一下? [https://whycan.cn/t_3865.html]

BCM43438蓝牙驱动也了解一下? [https://whycan.cn/t_2537.html]

NMI驱动要不也加上? [https://whycan.cn/t_3762.html] [https://whycan.cn/t_3714.html]

2. rootfs用debootstrap一换

咋用阿? [http://linux-sunxi.org/Debootstrap]

3. modules记得也拷贝进去

4. ubuntu走起来

还是不会?

TF卡镜像: (等晕哥发连接吧,这论坛传不来这么大的)

用户名: root 密码: (空)

演示视频:

你们肯定好奇的一个东西

root@armhf:~# free -m

total used free shared buff/cache available

Mem: 116 26 39 1 50 82

Swap: 127 0 127#90 全志 SOC » Allwinner S3 uboot 2020.01 (开机Logo + LCD + 以太网 + SDC 2) » 2020-03-13 12:28:17

- aodzip

- 回复: 12

去下个uboot 2020.01,把压缩包里的文件覆盖下就OK

有大佬整个patch的好活么?

目前支持的功能:

开机:TF卡启动,eMMC启动

DisplayEngine2:反正能亮

LCD:面板配置文件和背光控制已迁移至DTS

开机LOGO:替换uboot分区下的splash.bmp即可

以太网:TFTP调试必备

make allwinner_s3_generic_defconfig

#95 Re: 全志 SOC » Allwinner S3 增加 AXP209 PMIC 的一些记录 » 2020-02-26 17:09:05

本帖子中对NMI Controller的dtsi修改有误,需要参考 https://whycan.cn/p_34557.html 中对NMI控制器驱动进行patch和dtsi修改

修改后按下AXP209的电源按钮时,Linux正确触发event

#96 全志 SOC » sun8iw8p1(V3 V3s S3 S3L) 的 NMI中断驱动patch 和 dtsi修改 » 2020-02-26 17:04:23

- aodzip

- 回复: 6

linux-5.3.12/drivers/irqchip/irq-sunxi-nmi.c

关注和sun8i字样相关的修改

/*

* Allwinner A20/A31 SoCs NMI IRQ chip driver.

*

* Carlo Caione <carlo.caione@gmail.com>

*

* This file is licensed under the terms of the GNU General Public

* License version 2. This program is licensed "as is" without any

* warranty of any kind, whether express or implied.

*/

#define DRV_NAME "sunxi-nmi"

#define pr_fmt(fmt) DRV_NAME ": " fmt

#include <linux/bitops.h>

#include <linux/device.h>

#include <linux/io.h>

#include <linux/irq.h>

#include <linux/interrupt.h>

#include <linux/irqdomain.h>

#include <linux/of_irq.h>

#include <linux/of_address.h>

#include <linux/of_platform.h>

#include <linux/irqchip.h>

#include <linux/irqchip/chained_irq.h>

#define SUNXI_NMI_SRC_TYPE_MASK 0x00000003

#define SUNXI_NMI_IRQ_BIT BIT(0)

#define SUN6I_R_INTC_CTRL 0x0c

#define SUN6I_R_INTC_PENDING 0x10

#define SUN6I_R_INTC_ENABLE 0x40

/*

* For deprecated sun6i-a31-sc-nmi compatible.

* Registers are offset by 0x0c.

*/

#define SUN6I_R_INTC_NMI_OFFSET 0x0c

#define SUN6I_NMI_CTRL (SUN6I_R_INTC_CTRL - SUN6I_R_INTC_NMI_OFFSET)

#define SUN6I_NMI_PENDING (SUN6I_R_INTC_PENDING - SUN6I_R_INTC_NMI_OFFSET)

#define SUN6I_NMI_ENABLE (SUN6I_R_INTC_ENABLE - SUN6I_R_INTC_NMI_OFFSET)

#define SUN7I_NMI_CTRL 0x00

#define SUN7I_NMI_PENDING 0x04

#define SUN7I_NMI_ENABLE 0x08

#define SUN9I_NMI_CTRL 0x00

#define SUN9I_NMI_ENABLE 0x04

#define SUN9I_NMI_PENDING 0x08

#define SUN8I_NMI_CTRL 0xd0

#define SUN8I_NMI_ENABLE 0xd4

#define SUN8I_NMI_PENDING 0xd8

enum {

SUNXI_SRC_TYPE_LEVEL_LOW = 0,

SUNXI_SRC_TYPE_EDGE_FALLING,

SUNXI_SRC_TYPE_LEVEL_HIGH,

SUNXI_SRC_TYPE_EDGE_RISING,

};

struct sunxi_sc_nmi_reg_offs {

u32 ctrl;

u32 pend;

u32 enable;

};

static const struct sunxi_sc_nmi_reg_offs sun6i_r_intc_reg_offs __initconst = {

.ctrl = SUN6I_R_INTC_CTRL,

.pend = SUN6I_R_INTC_PENDING,

.enable = SUN6I_R_INTC_ENABLE,

};

static const struct sunxi_sc_nmi_reg_offs sun6i_reg_offs __initconst = {

.ctrl = SUN6I_NMI_CTRL,

.pend = SUN6I_NMI_PENDING,

.enable = SUN6I_NMI_ENABLE,

};

static const struct sunxi_sc_nmi_reg_offs sun7i_reg_offs __initconst = {

.ctrl = SUN7I_NMI_CTRL,

.pend = SUN7I_NMI_PENDING,

.enable = SUN7I_NMI_ENABLE,

};

static const struct sunxi_sc_nmi_reg_offs sun9i_reg_offs __initconst = {

.ctrl = SUN9I_NMI_CTRL,

.pend = SUN9I_NMI_PENDING,

.enable = SUN9I_NMI_ENABLE,

};

static const struct sunxi_sc_nmi_reg_offs sun8i_reg_offs __initconst = {

.ctrl = SUN8I_NMI_CTRL,

.pend = SUN8I_NMI_PENDING,

.enable = SUN8I_NMI_ENABLE,

};

static inline void sunxi_sc_nmi_write(struct irq_chip_generic *gc, u32 off,

u32 val)

{

irq_reg_writel(gc, val, off);

}

static inline u32 sunxi_sc_nmi_read(struct irq_chip_generic *gc, u32 off)

{

return irq_reg_readl(gc, off);

}

static void sunxi_sc_nmi_handle_irq(struct irq_desc *desc)

{

struct irq_domain *domain = irq_desc_get_handler_data(desc);

struct irq_chip *chip = irq_desc_get_chip(desc);

unsigned int virq = irq_find_mapping(domain, 0);

chained_irq_enter(chip, desc);

generic_handle_irq(virq);

chained_irq_exit(chip, desc);

}

static int sunxi_sc_nmi_set_type(struct irq_data *data, unsigned int flow_type)

{

struct irq_chip_generic *gc = irq_data_get_irq_chip_data(data);

struct irq_chip_type *ct = gc->chip_types;

u32 src_type_reg;

u32 ctrl_off = ct->regs.type;

unsigned int src_type;

unsigned int i;

irq_gc_lock(gc);

switch (flow_type & IRQF_TRIGGER_MASK) {

case IRQ_TYPE_EDGE_FALLING:

src_type = SUNXI_SRC_TYPE_EDGE_FALLING;

break;

case IRQ_TYPE_EDGE_RISING:

src_type = SUNXI_SRC_TYPE_EDGE_RISING;

break;

case IRQ_TYPE_LEVEL_HIGH:

src_type = SUNXI_SRC_TYPE_LEVEL_HIGH;

break;

case IRQ_TYPE_NONE:

case IRQ_TYPE_LEVEL_LOW:

src_type = SUNXI_SRC_TYPE_LEVEL_LOW;

break;

default:

irq_gc_unlock(gc);

pr_err("Cannot assign multiple trigger modes to IRQ %d.\n",

data->irq);

return -EBADR;

}

irqd_set_trigger_type(data, flow_type);

irq_setup_alt_chip(data, flow_type);

for (i = 0; i < gc->num_ct; i++, ct++)

if (ct->type & flow_type)

ctrl_off = ct->regs.type;

src_type_reg = sunxi_sc_nmi_read(gc, ctrl_off);

src_type_reg &= ~SUNXI_NMI_SRC_TYPE_MASK;

src_type_reg |= src_type;

sunxi_sc_nmi_write(gc, ctrl_off, src_type_reg);

irq_gc_unlock(gc);

return IRQ_SET_MASK_OK;

}

static int __init sunxi_sc_nmi_irq_init(struct device_node *node,

const struct sunxi_sc_nmi_reg_offs *reg_offs)

{

struct irq_domain *domain;

struct irq_chip_generic *gc;

unsigned int irq;

unsigned int clr = IRQ_NOREQUEST | IRQ_NOPROBE | IRQ_NOAUTOEN;

int ret;

domain = irq_domain_add_linear(node, 1, &irq_generic_chip_ops, NULL);

if (!domain) {

pr_err("Could not register interrupt domain.\n");

return -ENOMEM;

}

ret = irq_alloc_domain_generic_chips(domain, 1, 2, DRV_NAME,

handle_fasteoi_irq, clr, 0,

IRQ_GC_INIT_MASK_CACHE);

if (ret) {

pr_err("Could not allocate generic interrupt chip.\n");

goto fail_irqd_remove;

}

irq = irq_of_parse_and_map(node, 0);

if (irq <= 0) {

pr_err("unable to parse irq\n");

ret = -EINVAL;

goto fail_irqd_remove;

}

gc = irq_get_domain_generic_chip(domain, 0);

gc->reg_base = of_io_request_and_map(node, 0, of_node_full_name(node));

if (IS_ERR(gc->reg_base)) {

pr_err("unable to map resource\n");

ret = PTR_ERR(gc->reg_base);

goto fail_irqd_remove;

}

gc->chip_types[0].type = IRQ_TYPE_LEVEL_MASK;

gc->chip_types[0].chip.irq_mask = irq_gc_mask_clr_bit;

gc->chip_types[0].chip.irq_unmask = irq_gc_mask_set_bit;

gc->chip_types[0].chip.irq_eoi = irq_gc_ack_set_bit;

gc->chip_types[0].chip.irq_set_type = sunxi_sc_nmi_set_type;

gc->chip_types[0].chip.flags = IRQCHIP_EOI_THREADED | IRQCHIP_EOI_IF_HANDLED;

gc->chip_types[0].regs.ack = reg_offs->pend;

gc->chip_types[0].regs.mask = reg_offs->enable;

gc->chip_types[0].regs.type = reg_offs->ctrl;

gc->chip_types[1].type = IRQ_TYPE_EDGE_BOTH;

gc->chip_types[1].chip.name = gc->chip_types[0].chip.name;

gc->chip_types[1].chip.irq_ack = irq_gc_ack_set_bit;

gc->chip_types[1].chip.irq_mask = irq_gc_mask_clr_bit;

gc->chip_types[1].chip.irq_unmask = irq_gc_mask_set_bit;

gc->chip_types[1].chip.irq_set_type = sunxi_sc_nmi_set_type;

gc->chip_types[1].regs.ack = reg_offs->pend;

gc->chip_types[1].regs.mask = reg_offs->enable;

gc->chip_types[1].regs.type = reg_offs->ctrl;

gc->chip_types[1].handler = handle_edge_irq;

/* Disable any active interrupts */

sunxi_sc_nmi_write(gc, reg_offs->enable, 0);