- 首页

- » 搜索

- » flyaqiao 发表的帖子

页次: 1

#1 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 优惠券转让 » 2024-03-30 15:39:43

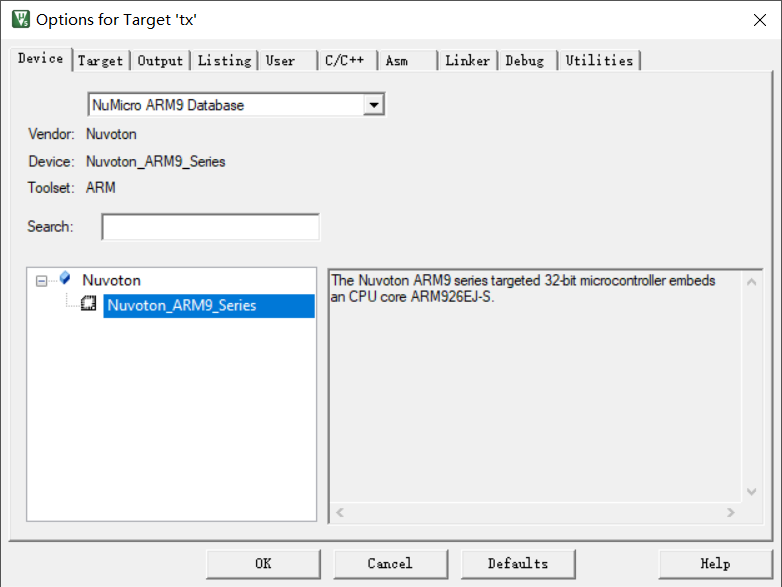

#2 全志 SOC » 这种USB口的4G模块不停的连上又断开,是因为4G模块供电不足吗? » 2024-03-28 08:50:35

- flyaqiao

- 回复: 0

[ 11.235851] hub 1-1:1.0: USB hub found

[ 11.239773] hub 1-1:1.0: 4 ports detected

[ 11.481159] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pd not found, using dummy regulator

[ 11.727682] usb 1-1.2: new high-speed USB device number 3 using musb-hdrc

[ 11.985753] rndis_host 1-1.2:1.0: rndis media connect

[ 12.047681] rndis_host 1-1.2:1.0 eth0: register 'rndis_host' at usb-musb-hdrc.1.auto-1.2, RNDIS device, 20:89:84:6a:96:ab

[ 12.087252] option 1-1.2:1.2: GSM modem (1-port) converter detected

[ 12.095155] option 1-1.2:1.3: GSM modem (1-port) converter detected

[ 12.132738] usb 1-1.2: GSM modem (1-port) converter now attached to ttyUSB1

[ 12.159168] option 1-1.2:1.4: GSM modem (1-port) converter detected

[ 12.167096] option 1-1.2:1.5: GSM modem (1-port) converter detected

[ 12.206155] usb 1-1.2: GSM modem (1-port) converter now attached to ttyUSB3

[ 12.232906] option 1-1.2:1.6: GSM modem (1-port) converter detected

[ 12.240780] option 1-1.2:1.7: GSM modem (1-port) converter detected

[ 12.278435] usb 1-1.2: GSM modem (1-port) converter now attached to ttyUSB5

[ 12.503790] usb 1-1.4: new high-speed USB device number 4 using musb-hdrc

[ 13.025401] usb 1-1.4: Vendor: Realtek

[ 13.029227] usb 1-1.4: Product: 802.11n

[ 13.033113] usb 1-1.4: RTL8188FU rev B (SMIC) 1T1R, TX queues 2, WiFi=1, BT=0, GPS=0, HI PA=0

[ 13.041735] usb 1-1.4: RTL8188FU MAC: 34:7d:e4:17:34:2d

[ 13.047026] usb 1-1.4: rtl8xxxu: Loading firmware rtlwifi/rtl8188fufw.bin

[ 13.098325] usb 1-1.4: Firmware revision 4.0 (signature 0x88f1)

[ 13.126463] do the RAM reset

[ 13.861109] usb 1-1.2: USB disconnect, device number 3

[ 13.866833] rndis_host 1-1.2:1.0 eth0: unregister 'rndis_host' usb-musb-hdrc.1.auto-1.2, RNDIS device

[ 13.944640] option 1-1.2:1.2: device disconnected

[ 13.977692] option1 ttyUSB1: GSM modem (1-port) converter now disconnected from ttyUSB1

[ 13.986118] option 1-1.2:1.3: device disconnected

[ 13.991721] option 1-1.2:1.4: device disconnected

[ 14.091107] option1 ttyUSB3: GSM modem (1-port) converter now disconnected from ttyUSB3

[ 14.099528] option 1-1.2:1.5: device disconnected

[ 14.105314] option 1-1.2:1.6: device disconnected

[ 14.228209] option1 ttyUSB5: GSM modem (1-port) converter now disconnected from ttyUSB5

[ 14.236644] option 1-1.2:1.7: device disconnected

[ 14.803587] usb 1-1.2: new high-speed USB device number 5 using musb-hdrc

[ 15.170539] rndis_host 1-1.2:1.0 eth0: register 'rndis_host' at usb-musb-hdrc.1.auto-1.2, RNDIS device, 20:89:84:6a:96:ab

[ 15.308672] option 1-1.2:1.2: GSM modem (1-port) converter detected

[ 15.316505] option 1-1.2:1.3: GSM modem (1-port) converter detected

[ 15.346426] usb 1-1.2: GSM modem (1-port) converter now attached to ttyUSB1

[ 15.392434] option 1-1.2:1.4: GSM modem (1-port) converter detected

[ 15.400312] option 1-1.2:1.5: GSM modem (1-port) converter detected

[ 15.456933] usb 1-1.2: GSM modem (1-port) converter now attached to ttyUSB3

[ 15.489482] option 1-1.2:1.6: GSM modem (1-port) converter detected

[ 15.497351] option 1-1.2:1.7: GSM modem (1-port) converter detected

[ 15.555790] usb 1-1.2: GSM modem (1-port) converter now attached to ttyUSB5

[ 16.089706] musb-hdrc musb-hdrc.1.auto: int hwep alloc failed for 1x8

[ 19.990255] usb 1-1.2: USB disconnect, device number 5

[ 19.995984] rndis_host 1-1.2:1.0 eth0: unregister 'rndis_host' usb-musb-hdrc.1.auto-1.2, RNDIS device

[ 20.116549] option 1-1.2:1.2: device disconnected

[ 20.152529] option1 ttyUSB1: GSM modem (1-port) converter now disconnected from ttyUSB1

[ 20.160956] option 1-1.2:1.3: device disconnected

[ 20.166817] option 1-1.2:1.4: device disconnected

[ 20.284815] option1 ttyUSB3: GSM modem (1-port) converter now disconnected from ttyUSB3

[ 20.293163] option 1-1.2:1.5: device disconnected

[ 20.298922] option 1-1.2:1.6: device disconnected

[ 20.437184] option1 ttyUSB5: GSM modem (1-port) converter now disconnected from ttyUSB5

#3 Re: 全志 SOC » 成功移植go编译器到f1c100s » 2023-12-01 15:14:18

#4 Re: Nuvoton N32905/N32926/NUC972/N9H20/N9H26/N9H30 » NUC972 成功移植Threadx 6.x, 记录一下移植过程... » 2023-11-13 13:58:31

#5 Re: Nuvoton N32905/N32926/NUC972/N9H20/N9H26/N9H30 » NUC972 成功移植Threadx 6.x, 记录一下移植过程... » 2023-11-02 17:26:16

#6 Re: 全志 SOC » V3s/S3/f1c100s通过USB启动Linux,并把SD NAND/TF卡挂载为U盘, 可以dd或Win32DiskImager任烧写 » 2023-10-27 09:23:23

#7 Re: 全志 SOC » SPI NOR FLASH上运行,USB HUB芯片无法识别 » 2023-10-26 22:58:00

问题是设备树中的内核地址和uboot参数中的内核地址不一样,很奇怪这种情况系统能正常启动

diff --git a/board/sipeed/lichee/nano/devicetree/linux/devicetree.dts b/board/sipeed/lichee/nano/devicetree/linux/devicetree.dts

index 93aa99c57b..6e432c250b 100644

--- a/board/sipeed/lichee/nano/devicetree/linux/devicetree.dts

+++ b/board/sipeed/lichee/nano/devicetree/linux/devicetree.dts

@@ -78,19 +78,19 @@

partition@1 {

label = "kernel";

- reg = <0x70000 0x590000>;

+ reg = <0x100000 0x500000>;

read-only;

};

partition@2 {

label = "rom";

- reg = <0x600000 0x700000>;

+ reg = <0x600000 0x800000>;

read-only;

};

partition@3 {

label = "overlay";

- reg = <0xd00000 0x300000>;

+ reg = <0xE00000 0x200000>;

};

};

};uboot中内核地址是:sf_kernel_offset=0x100000

但usb也必须配置成otg模式,没想通.改成host就不能识别了

&usb_otg {

- dr_mode = "host"; /* otg host peripheral */

+ dr_mode = "otg"; /* otg host peripheral */

status = "okay";

};#9 Nuvoton N32905/N32926/NUC972/N9H20/N9H26/N9H30 » NUC972 成功移植Threadx 6.x, 记录一下移植过程... » 2023-10-26 19:10:22

- flyaqiao

- 回复: 7

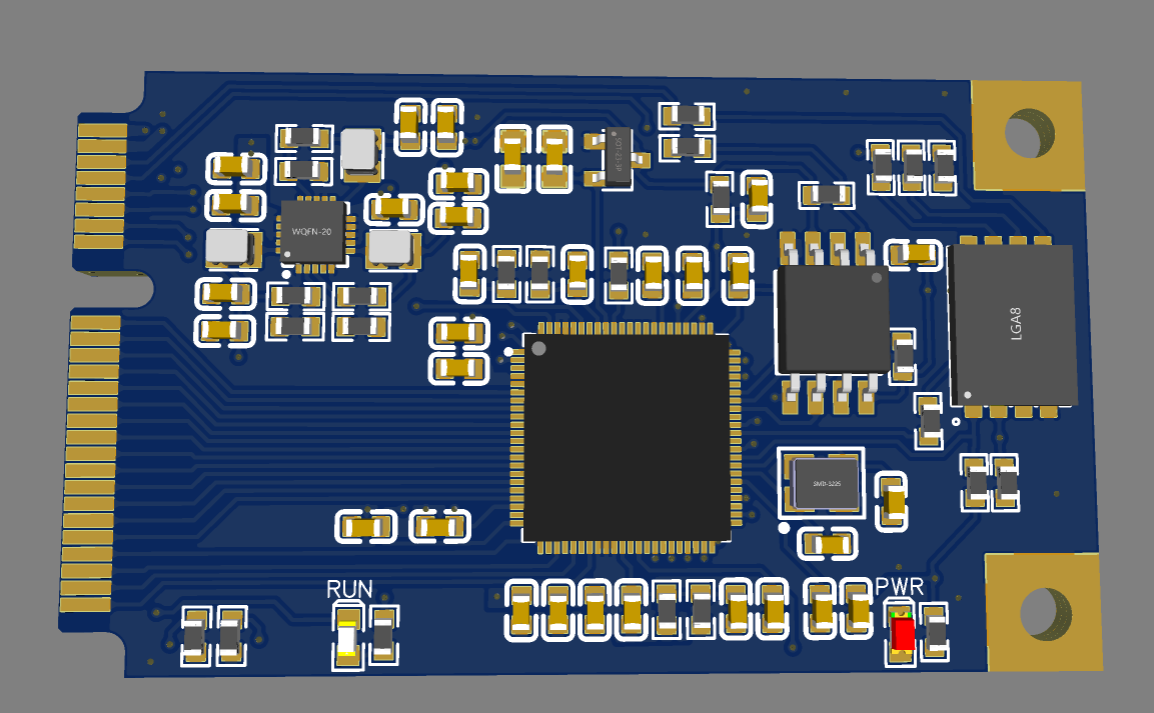

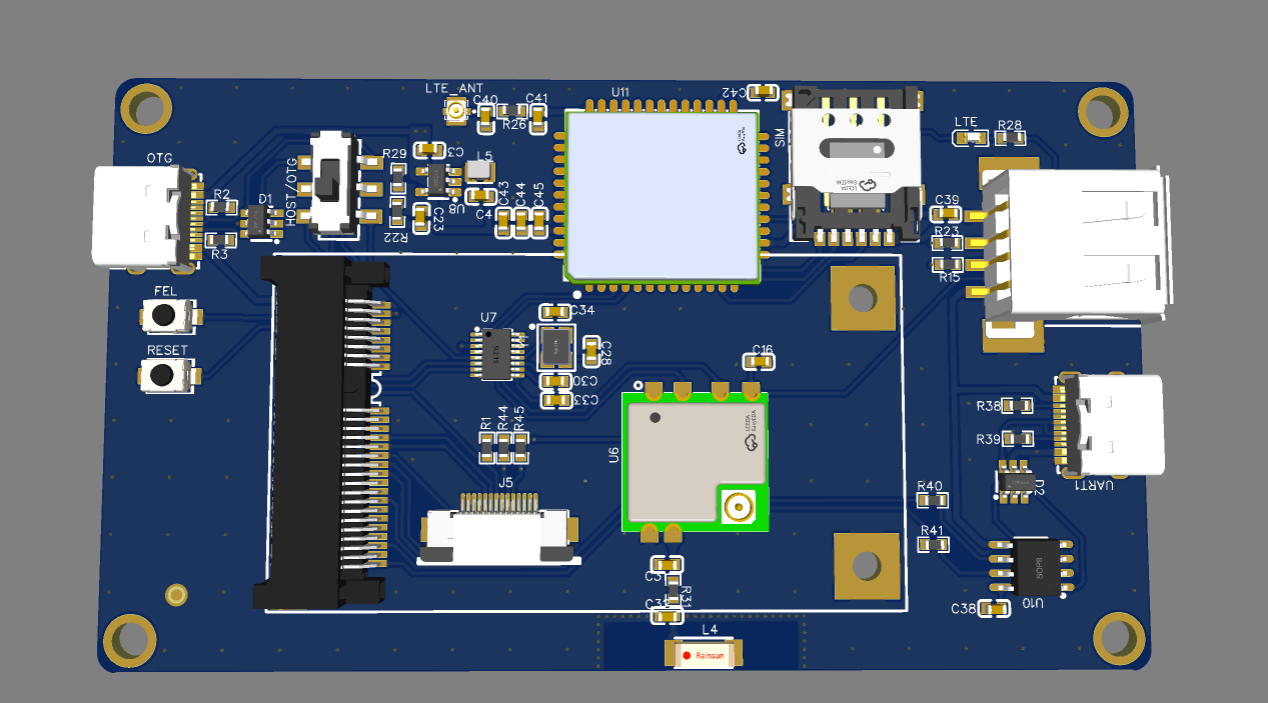

项目需要,使用的nuc972主芯片,需要支持网络协议,就打算移植一下azure的tx,filex,netxduo,下面新记录一下tx的移植过程:

由于新唐的arm9中断处理和定时器初始化的寄存器并不同于tx官方的arm9的port,所以官方的port无法正常运行.

1.首先从github下载最新的tx代码.

git clone https://github.com/azure-rtos/threadx.git

2.创建tx的keil工程,nuc972官方没有提供iar工程,所以这里都使用keil,编译成lib的形式.

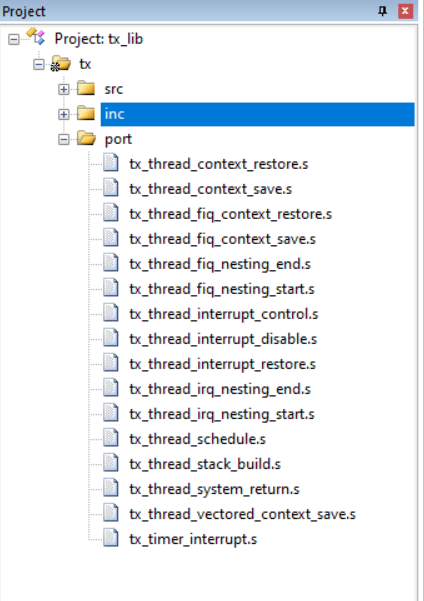

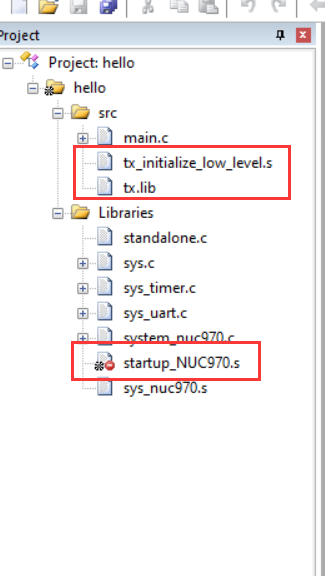

项目结构:

共三个目录:将tx的common/src目录下的所有文件添加到src目录

将tx的common/inc目录下的所有文件添加到inc目录

将tx的ports/arm9/ac5/inc目录下的所有文件添加到inc目录(其实就一个tx_port.h)

将tx的ports/arm9/ac5/src目录下的所有文件添加到port目录

如图:

设置DEVICE:

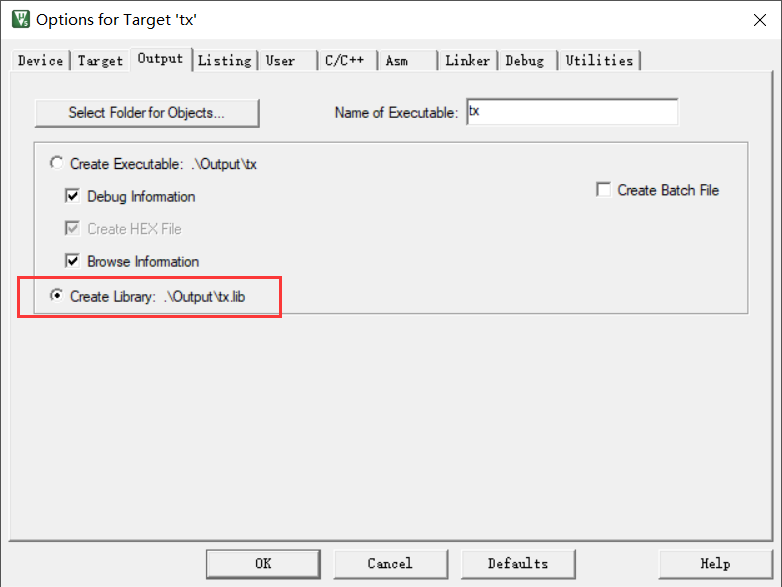

设置Output:

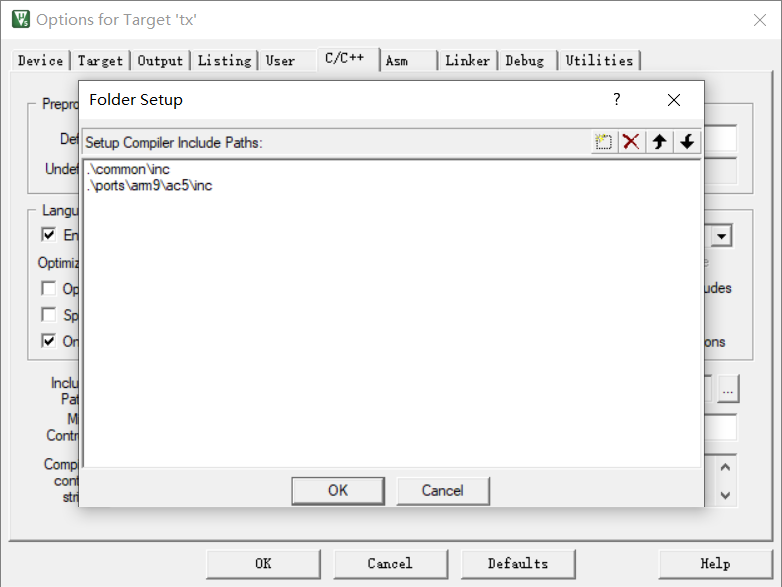

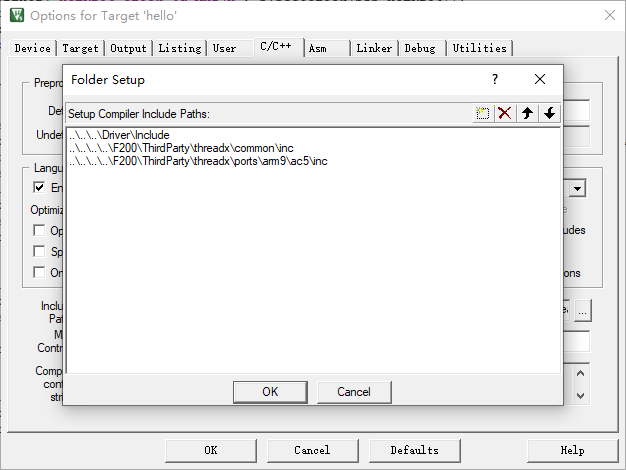

设置Include:

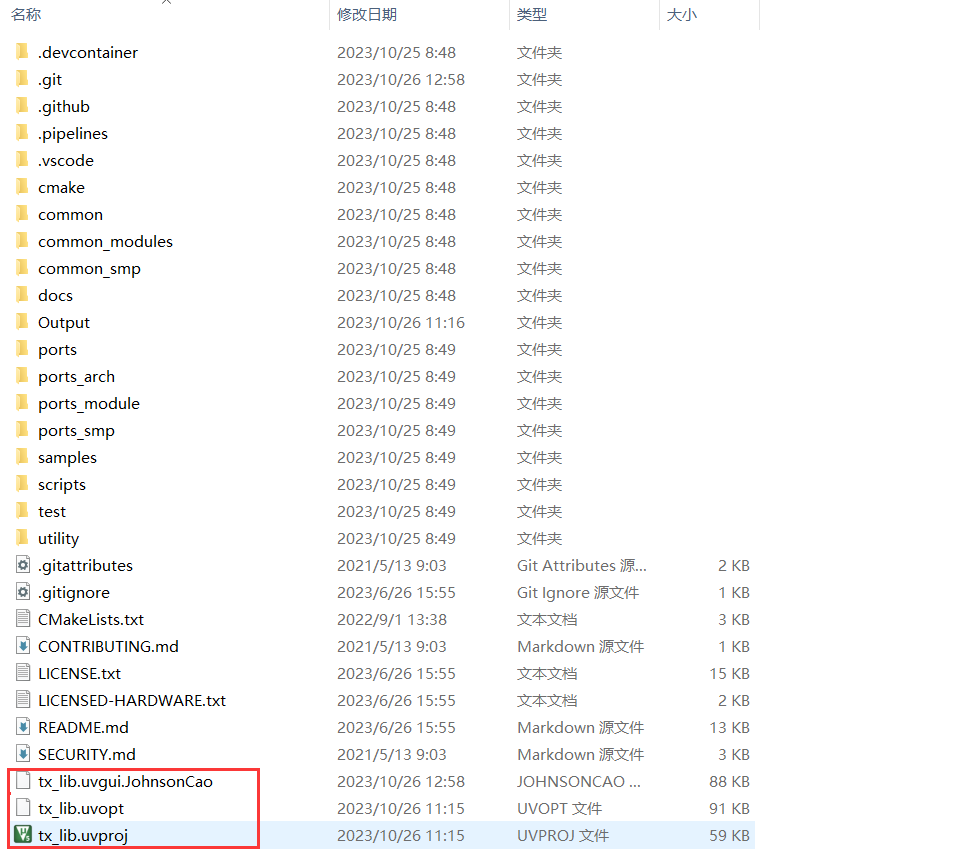

编译生成tx.lib文件备用,也可以直接下载工程文件并到tx根目录下:tx_lib_20231026182439.rar

以上就是tx库的生成过程

3.打开新唐官方Non-OS BSP中的hello工程

将刚才生成的tx.lib放到hello目录下

将ports/arm9/ac5/example_build下的tx_initialize_low_level.s放到hello目录下,移植的主要工作就是修改这个文件,这里先放上我移植好的文件

tx_initialize_low_level_20231026183734.rar

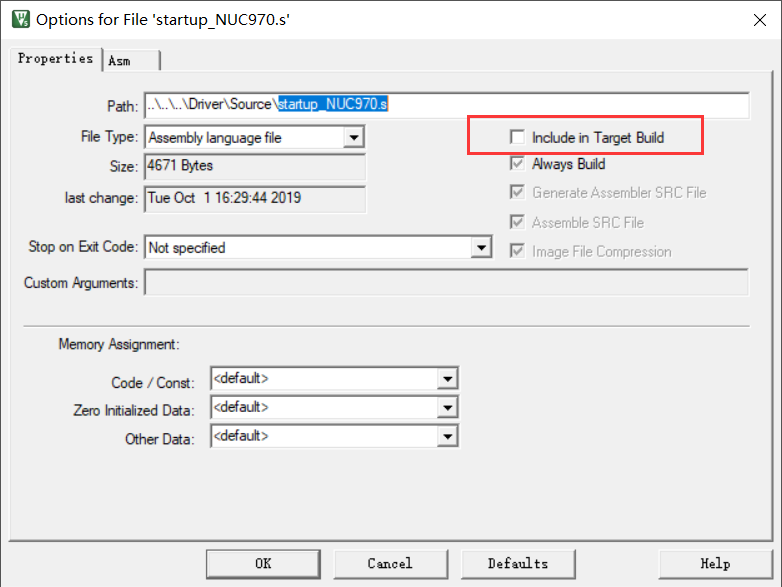

打开工程加入刚才的两个文件,并在项目中排除startup_NUC970.s文件

此时编译项目应该没有错误

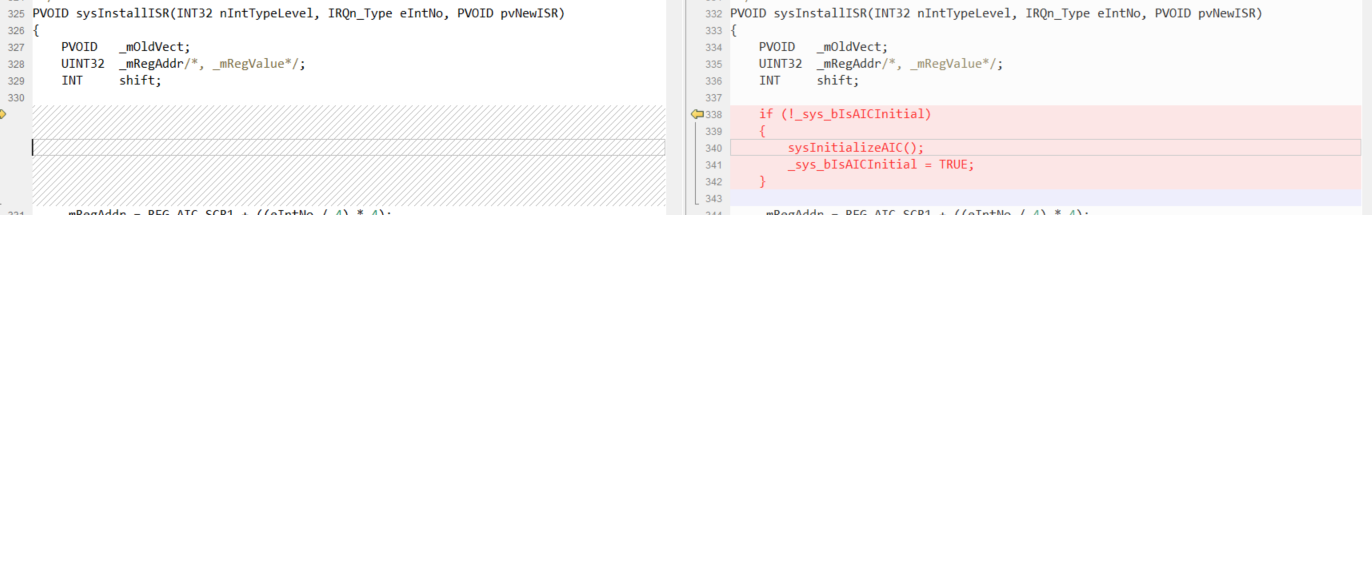

移植之前先修改sys.c文件,删除注册中断回调时的sysInitializeAIC调用

中断入口将由tx_initialize_low_level.s中的__tx_irq_handler接管,所以不能再动态修改中断入口

;/**************************************************************************/

;/* */

;/* Copyright (c) Microsoft Corporation. All rights reserved. */

;/* */

;/* This software is licensed under the Microsoft Software License */

;/* Terms for Microsoft Azure RTOS. Full text of the license can be */

;/* found in the LICENSE file at https://aka.ms/AzureRTOS_EULA */

;/* and in the root directory of this software. */

;/* */

;/**************************************************************************/

;

;

;/**************************************************************************/

;/**************************************************************************/

;/** */

;/** ThreadX Component */

;/** */

;/** Initialize */

;/** */

;/**************************************************************************/

;/**************************************************************************/

;

;

;#define TX_SOURCE_CODE

;

;

;/* Include necessary system files. */

;

;#include "tx_api.h"

;#include "tx_initialize.h"

;#include "tx_thread.h"

;#include "tx_timer.h"

;

;

SVC_MODE EQU 0xD3 ; Disable IRQ/FIQ SVC mode

IRQ_MODE EQU 0xD2 ; Disable IRQ/FIQ IRQ mode

FIQ_MODE EQU 0xD1 ; Disable IRQ/FIQ FIQ mode

SYS_MODE EQU 0xDF ; Disable IRQ/FIQ SYS mode

HEAP_SIZE EQU 4096 ; Heap size

UND_STACK_SIZE EQU 256

ABT_STACK_SIZE EQU 256

FIQ_STACK_SIZE EQU 512 ; FIQ stack size

SVC_STACK_SIZE EQU 1024

SYS_STACK_SIZE EQU 1024 ; SYS stack size (used for nested interrupts)

IRQ_STACK_SIZE EQU 1024 ; IRQ stack size

;

;

;/* ARM9 ARMulator Timer and Interrupt controller information. This depends on

; the ARMulator's Interrupt Controller and Timer being enabled in the default.ami.

; In addition, the addresses must match those specified in the peripherals.ami file.

; Please refer to section 2.10 and 4.16 of the Debug Target Guide, version 1.2. */

;

TMR0_CLK EQU 0x00E4E1C0

TMR0_IRQn EQU 16

REG_TMR_TISR EQU 0xB8001060 ; Timer Interrupt Status Register

REG_AIC_BA EQU 0xB8002000 ; Interrupt Controller

REG_AIC_IPER EQU 0xB8002118 ; Interrupt priority encoding register

REG_AIC_ISNR EQU 0xB8002120 ; Interrupt source number register

REG_AIC_MDCR EQU 0xB8002138 ; Mask disable command register

REG_AIC_MDCRH EQU 0xB800213C ; Mask disable command register (High)

REG_AIC_EOSCR EQU 0xB8002150

;

;

IMPORT _tx_thread_system_stack_ptr

IMPORT _tx_initialize_unused_memory

IMPORT _tx_thread_context_save

IMPORT _tx_thread_context_restore

IF :DEF:TX_ENABLE_FIQ_SUPPORT

IMPORT _tx_thread_fiq_context_save

IMPORT _tx_thread_fiq_context_restore

ENDIF

IF :DEF:TX_ENABLE_IRQ_NESTING

IMPORT _tx_thread_irq_nesting_start

IMPORT _tx_thread_irq_nesting_end

ENDIF

IF :DEF:TX_ENABLE_FIQ_NESTING

IMPORT _tx_thread_fiq_nesting_start

IMPORT _tx_thread_fiq_nesting_end

ENDIF

IMPORT _tx_timer_interrupt

IMPORT __main

IMPORT _tx_version_id

IMPORT _tx_build_options

IMPORT sysIrqHandlerTable

IMPORT sysSetTimerReferenceClock

IMPORT sysStartTimer

IMPORT sysGetSdramSizebyMB

IMPORT |Image$$RW_RAM1$$ZI$$Limit|

;

AREA NUC_INIT, CODE, READONLY

;

;/* Define the ARM9 vector area. This should be located or copied to 0. */

;

ENTRY

EXPORT Reset_Go

EXPORT __vectors

__vectors

B Reset_Go

LDR pc,=__tx_undefined ; Undefined handler

LDR pc,=__tx_swi_interrupt ; Software interrupt handler

LDR pc,=__tx_prefetch_handler ; Prefetch exception handler

LDR pc,=__tx_abort_handler ; Abort exception handler

LDR pc,=__tx_reserved_handler ; Reserved exception handler

LDR pc,=__tx_irq_handler ; IRQ interrupt handler

LDR pc,=__tx_fiq_handler ; FIQ interrupt handler

;

;

Reset_Go

; Disable Interrupt in case code is load by ICE while other firmware is executing

LDR r0, =REG_AIC_MDCR

LDR r1, =0xFFFFFFFF

STR r1, [r0]

LDR r0, =REG_AIC_MDCRH

STR r1, [r0]

;--------------------------------

; Initial Stack Pointer register

;--------------------------------

;INIT_STACK

LDR r1, =|Image$$RW_RAM1$$ZI$$Limit| ; Get end of non-initialized RAM area

LDR r2, =HEAP_SIZE ; Pickup the heap size

ADD r1, r2, r1 ; Setup heap limit

ADD r1, r1, #4 ; Setup stack limit

; /* Setup the system mode stack for nested interrupt support */

LDR r2, =SYS_STACK_SIZE ; Pickup stack size

MOV r3, #SYS_MODE ; Build SYS mode CPSR

MSR CPSR_c, r3 ; Enter SYS mode

ADD r1, r1, r2 ; Calculate start of SYS stack

BIC r1, r1, #7 ; Ensure 8-byte alignment

MOV sp, r1 ; Setup SYS stack pointer

LDR r2, =FIQ_STACK_SIZE ; Pickup stack size

MOV r0, #FIQ_MODE ; Build FIQ mode CPSR

MSR CPSR_c, r0 ; Enter FIQ mode

ADD r1, r1, r2 ; Calculate start of FIQ stack

BIC r1, r1, #7 ; Ensure 8-byte alignment

MOV sp, r1 ; Setup FIQ stack pointer

MOV sl, #0 ; Clear sl

MOV fp, #0 ; Clear fp

MOV r0, #IRQ_MODE ; Build IRQ mode CPSR

MSR CPSR_c, r0 ; Enter IRQ mode

ADD r1, r1, r2 ; Calculate start of IRQ stack

BIC r1, r1, #7 ; Ensure 8-byte alignment

MOV sp, r1 ; Setup IRQ stack pointer

LDR r2, =SVC_STACK_SIZE ; Pickup SVC (SVC stack size)

MOV r0, #SVC_MODE ; Build SVC mode CPSR

MSR CPSR_c, r0 ; Enter SVC mode

ADD r1, r1, r2 ; Calculate start of SVC stack

BIC r1, r1, #7 ; Ensure 8-byte alignment

MOV sp, r1 ; Setup SVC stack pointe

;------------------------------------------------------

; Set the normal exception vector of CP15 control bit

;------------------------------------------------------

MRC p15, 0, r0 , c1, c0 ; r0 := cp15 register 1

BIC r0, r0, #0x2000 ; Clear bit13 in r1

MCR p15, 0, r0 , c1, c0 ; cp15 register 1 := r0

IMPORT __main

;-----------------------------

; enter the C code

;-----------------------------

B __main

AREA ||.text||, CODE, READONLY

;/**************************************************************************/

;/* */

;/* FUNCTION RELEASE */

;/* */

;/* _tx_initialize_low_level ARM9/AC5 */

;/* 6.0.1 */

;/* AUTHOR */

;/* */

;/* William E. Lamie, Microsoft Corporation */

;/* */

;/* DESCRIPTION */

;/* */

;/* This function is responsible for any low-level processor */

;/* initialization, including setting up interrupt vectors, setting */

;/* up a periodic timer interrupt source, saving the system stack */

;/* pointer for use in ISR processing later, and finding the first */

;/* available RAM memory address for tx_application_define. */

;/* */

;/* INPUT */

;/* */

;/* None */

;/* */

;/* OUTPUT */

;/* */

;/* None */

;/* */

;/* CALLS */

;/* */

;/* None */

;/* */

;/* CALLED BY */

;/* */

;/* _tx_initialize_kernel_enter ThreadX entry function */

;/* */

;/* RELEASE HISTORY */

;/* */

;/* DATE NAME DESCRIPTION */

;/* */

;/* 06-30-2020 William E. Lamie Initial Version 6.0.1 */

;/* */

;/**************************************************************************/

;VOID _tx_initialize_low_level(VOID)

;{

EXPORT _tx_initialize_low_level

_tx_initialize_low_level

PRESERVE8

;

;

; /****** NOTE ****** We must be in SVC MODE at this point. Some monitors

; enter this routine in USER mode and require a software interrupt to

; change into SVC mode. */

;

LDR r2, =SVC_STACK_SIZE ; Pickup SVC

MOV r0, #SVC_MODE ; Build SVC mode CPSR

MSR CPSR_c, r0 ; Enter SVC mode

MOV r1, sp

ADD r1, r1, r2 ; Calculate start of SVC stack

LDR r3, =_tx_thread_system_stack_ptr ; Pickup stack pointer

STR r1, [r3, #0] ; Save the system stack

;

; /* Save the system stack pointer. */

; _tx_thread_system_stack_ptr = (VOID_PTR) (sp);

;

LDR r1, =_tx_thread_system_stack_ptr ; Pickup address of system stack ptr

LDR r0, [r1, #0] ; Pickup system stack

ADD r0, r0, #4 ; Increment to next free word

;

; /* Save the first available memory address. */

; _tx_initialize_unused_memory = (VOID_PTR) |Image$$ZI$$Limit| + HEAP + [SYS_STACK] + FIQ_STACK + IRQ_STACK;

;

LDR r2, =_tx_initialize_unused_memory ; Pickup unused memory ptr address

STR r0, [r2, #0] ; Save first free memory address

;

; /* Setup Timer for periodic interrupts. */

;

; /* Setup ARMulator Timer0 for periodic interrupts. */

PUSH {lr} ; Save ISR lr

LDR r1,=TMR0_CLK

MOV r0,#0

BL sysSetTimerReferenceClock

MOV r2,#1 ; PERIODIC_MODE

MOV r1,#0x64 ; TX_TIMER_TICKS_PER_SECOND

MOV r0,#0 ; TIMER0

BL sysStartTimer

POP {lr} ; Recover ISR lr

; /* Done, return to caller. */

;

IF {INTER} = {TRUE}

BX lr ; Return to caller

ELSE

MOV pc, lr ; Return to caller

ENDIF

;}

;

;

;/* Define initial heap/stack routine for the ARM RealView (and ADS) startup code. This

; routine will set the initial stack to use the ThreadX IRQ & FIQ &

; (optionally SYS) stack areas. */

;

; EXPORT __user_initial_stackheap

;__user_initial_stackheap

; LDR r0, =|Image$$ZI$$Limit| ; Get end of non-initialized RAM area

; LDR r2, =HEAP_SIZE ; Pickup the heap size

; ADD r2, r2, r0 ; Setup heap limit

; ADD r3, r2, #4 ; Setup stack limit

; MOV r1, r3 ; Setup start of stack

; IF :DEF:TX_ENABLE_IRQ_NESTING

; LDR r12, =SYS_STACK_SIZE ; Pickup IRQ system stack

; ADD r1, r1, r12 ; Setup the return system stack

; BIC r1, r1, #7 ; Ensure 8-byte alignment

; ENDIF

; LDR r12, =FIQ_STACK_SIZE ; Pickup FIQ stack size

; ADD r1, r1, r12 ; Setup the return system stack

; BIC r1, r1, #7 ; Ensure 8-byte alignment

; LDR r12, =IRQ_STACK_SIZE ; Pickup IRQ system stack

; ADD r1, r1, r12 ; Setup the return system stack

; BIC r1, r1, #7 ; Ensure 8-byte alignment

; IF {INTER} = {TRUE}

; BX lr ; Return to caller

; ELSE

; MOV pc, lr ; Return to caller

; ENDIF

;

;

;/* Define shells for each of the interrupt vectors. */

;

EXPORT __tx_undefined

__tx_undefined

B __tx_undefined ; Undefined handler

;

EXPORT __tx_swi_interrupt

__tx_swi_interrupt

B __tx_swi_interrupt ; Software interrupt handler

;

EXPORT __tx_prefetch_handler

__tx_prefetch_handler

B __tx_prefetch_handler ; Prefetch exception handler

;

EXPORT __tx_abort_handler

__tx_abort_handler

B __tx_abort_handler ; Abort exception handler

;

EXPORT __tx_reserved_handler

__tx_reserved_handler

B __tx_reserved_handler ; Reserved exception handler

;

;

EXPORT __tx_irq_handler

EXPORT __tx_irq_processing_return

__tx_irq_handler

;

; /* Jump to context save to save system context. */

B _tx_thread_context_save

__tx_irq_processing_return

;

; /* At this point execution is still in the IRQ mode. The CPSR, point of

; interrupt, and all C scratch registers are available for use. In

; addition, IRQ interrupts may be re-enabled - with certain restrictions -

; if nested IRQ interrupts are desired. Interrupts may be re-enabled over

; small code sequences where lr is saved before enabling interrupts and

; restored after interrupts are again disabled. */

;

;

; /* Check for Timer0 interrupts on the ARMulator. */

LDR r0,=REG_AIC_IPER

LDR r0,[r0]

MOV r1,#0x3f

AND r0,r1,r0,LSR #2

PUSH {r0}

LDR r2,=TMR0_IRQn ; Pickup Timer0 interrupt present bit

CMP r2, r0 ;

BNE _tx_not_timer_interrupt ; If 0, not a timer interrupt

LDR r0,=REG_TMR_TISR

LDR r0,[r0]

AND r0,r0,#1

CMP r0,#0

BEQ _tx_not_timer_interrupt

LDR r1,=REG_TMR_TISR ; Build address of Timer0 clear register

MOV r0,#1 ;

STR r0, [r1] ; Clear timer 0 interrupt

BL _tx_timer_interrupt ; Timer interrupt handler

_tx_not_timer_interrupt

;

; /* Interrupt nesting is allowed after calling _tx_thread_irq_nesting_start

; from IRQ mode with interrupts disabled. This routine switches to the

; system mode and returns with IRQ interrupts enabled.

;

; NOTE: It is very important to ensure all IRQ interrupts are cleared

; prior to enabling nested IRQ interrupts. */

IF :DEF:TX_ENABLE_IRQ_NESTING

BL _tx_thread_irq_nesting_start

ENDIF

;

;

; /* Application IRQ handlers can be called here! */

;

; LDR r0,=REG_AIC_IPER

; LDR r0,[r0]

; MOV r1,#0x3f

; AND r0,r1,r0,LSR #2

POP {r0}

SUB sp,sp,#8

STR r0,[sp,#4]

LDR r0,=REG_AIC_ISNR

LDR r0,[r0]

STR r0,[sp,#0]

LDR r0,[sp,#4]

CMP r0,#0

BEQ _irq_exit

LDR r0,[sp,#0]

CMP r0,#0

BEQ _irq_clear

LDR r1,=sysIrqHandlerTable

LDR r2,[sp,#4]

LDR r0,[r1,r2,LSL #2]

BLX r0

_irq_clear

MOV r0,#1

LDR r1,=REG_AIC_EOSCR

STR r0,[r1]

_irq_exit

ADD sp,sp,#8

; /* If interrupt nesting was started earlier, the end of interrupt nesting

; service must be called before returning to _tx_thread_context_restore.

; This routine returns in processing in IRQ mode with interrupts disabled. */

IF :DEF:TX_ENABLE_IRQ_NESTING

BL _tx_thread_irq_nesting_end

ENDIF

;

; /* Jump to context restore to restore system context. */

B _tx_thread_context_restore

;

;

; /* This is an example of a vectored IRQ handler. */

;

EXPORT __tx_example_vectored_irq_handler

__tx_example_vectored_irq_handler

;

;

; /* Save initial context and call context save to prepare for

; vectored ISR execution. */

;

; STMDB sp!, {r0-r3} ; Save some scratch registers

; MRS r0, SPSR ; Pickup saved SPSR

; SUB lr, lr, #4 ; Adjust point of interrupt

; STMDB sp!, {r0, r10, r12, lr} ; Store other scratch registers

; BL _tx_thread_vectored_context_save ; Vectored context save

;

; /* At this point execution is still in the IRQ mode. The CPSR, point of

; interrupt, and all C scratch registers are available for use. In

; addition, IRQ interrupts may be re-enabled - with certain restrictions -

; if nested IRQ interrupts are desired. Interrupts may be re-enabled over

; small code sequences where lr is saved before enabling interrupts and

; restored after interrupts are again disabled. */

;

;

; /* Interrupt nesting is allowed after calling _tx_thread_irq_nesting_start

; from IRQ mode with interrupts disabled. This routine switches to the

; system mode and returns with IRQ interrupts enabled.

;

; NOTE: It is very important to ensure all IRQ interrupts are cleared

; prior to enabling nested IRQ interrupts. */

; IF :DEF:TX_ENABLE_IRQ_NESTING

; BL _tx_thread_irq_nesting_start

; ENDIF

;

; /* Application IRQ handlers can be called here! */

;

; /* If interrupt nesting was started earlier, the end of interrupt nesting

; service must be called before returning to _tx_thread_context_restore.

; This routine returns in processing in IRQ mode with interrupts disabled. */

; IF :DEF:TX_ENABLE_IRQ_NESTING

; BL _tx_thread_irq_nesting_end

; ENDIF

;

; /* Jump to context restore to restore system context. */

; B _tx_thread_context_restore

;

;

IF :DEF:TX_ENABLE_FIQ_SUPPORT

EXPORT __tx_fiq_handler

EXPORT __tx_fiq_processing_return

__tx_fiq_handler

;

; /* Jump to fiq context save to save system context. */

B _tx_thread_fiq_context_save

__tx_fiq_processing_return

;

; /* At this point execution is still in the FIQ mode. The CPSR, point of

; interrupt, and all C scratch registers are available for use. */

;

; /* Interrupt nesting is allowed after calling _tx_thread_fiq_nesting_start

; from FIQ mode with interrupts disabled. This routine switches to the

; system mode and returns with FIQ interrupts enabled.

;

; NOTE: It is very important to ensure all FIQ interrupts are cleared

; prior to enabling nested FIQ interrupts. */

IF :DEF:TX_ENABLE_FIQ_NESTING

BL _tx_thread_fiq_nesting_start

ENDIF

;

; /* Application FIQ handlers can be called here! */

;

; /* If interrupt nesting was started earlier, the end of interrupt nesting

; service must be called before returning to _tx_thread_fiq_context_restore. */

IF :DEF:TX_ENABLE_FIQ_NESTING

BL _tx_thread_fiq_nesting_end

ENDIF

;

; /* Jump to fiq context restore to restore system context. */

B _tx_thread_fiq_context_restore

;

;

ELSE

EXPORT __tx_fiq_handler

__tx_fiq_handler

B __tx_fiq_handler ; FIQ interrupt handler

ENDIF

;

; /* Reference build options and version ID to ensure they come in. */

;

LDR r2, =_tx_build_options ; Pickup build options variable address

LDR r0, [r2, #0] ; Pickup build options content

LDR r2, =_tx_version_id ; Pickup version ID variable address

LDR r0, [r2, #0] ; Pickup version ID content

;

;

END这个代码主要干以下任务:

__vectors初始化中断向量表

Reset_Go程序入口,初始化AIC和堆栈,并跳转main函数

_tx_initialize_low_level是tx_kernel_enter调用,用来初始化timer0做为OS的tick定时器,并初始化_tx_thread_system_stack_ptr和_tx_initialize_unused_memory

后的就是中断处理函数,主要是__tx_irq_handler

LDR r0,=REG_AIC_IPER

LDR r0,[r0]

MOV r1,#0x3f

AND r0,r1,r0,LSR #2

PUSH {r0}

LDR r2,=TMR0_IRQn ; Pickup Timer0 interrupt present bit

CMP r2, r0 ;

BNE _tx_not_timer_interrupt ; If 0, not a timer interrupt

LDR r0,=REG_TMR_TISR

LDR r0,[r0]

AND r0,r0,#1

CMP r0,#0

BEQ _tx_not_timer_interrupt

LDR r1,=REG_TMR_TISR ; Build address of Timer0 clear register

MOV r0,#1 ;

STR r0, [r1] ; Clear timer 0 interrupt

BL _tx_timer_interrupt ; Timer interrupt handler这段代码检查是不是Timer0定时器中断,如果是则调用_tx_timer_interrupt,否则跳转到_tx_not_timer_interrupt执行正常中断处理

这里的PUSH {r0}注意,由于REG_AIC_IPER只能读取一次,这里压栈保存,方便后面正常中断处理使用

POP {r0} ; 弹出前面压入的中断号

SUB sp,sp,#8 ; 在栈中为临时变量留出空间

STR r0,[sp,#4]

LDR r0,=REG_AIC_ISNR

LDR r0,[r0]

STR r0,[sp,#0]

LDR r0,[sp,#4]

CMP r0,#0

BEQ _irq_exit

LDR r0,[sp,#0]

CMP r0,#0

BEQ _irq_clear

LDR r1,=sysIrqHandlerTable

LDR r2,[sp,#4]

LDR r0,[r1,r2,LSL #2]

BLX r0

_irq_clear

MOV r0,#1

LDR r1,=REG_AIC_EOSCR

STR r0,[r1]

_irq_exit

ADD sp,sp,#8 ; 返还临时变量占用的空间这就是正常中断处理了,作用等同于sys.c中的sysIrqHandler函数

移植到此就完成了

4.验证

修改main.c文件

/**************************************************************************//**

* @file main.c

* @version V1.00

* $Date: 15/05/07 5:38p $

* @brief NUC970 Driver Sample Code

*

* @note

* Copyright (C) 2015 Nuvoton Technology Corp. All rights reserved.

******************************************************************************/

#include "nuc970.h"

#include "sys.h"

#include "tx_api.h"

#define DEMO_STACK_SIZE (1024 * 32)

#define DEMO_BYTE_POOL_SIZE (1024 * 1024)

TX_THREAD thread_0;

TX_THREAD thread_1;

TX_THREAD thread_2;

TX_BYTE_POOL byte_pool_0;

TX_EVENT_FLAGS_GROUP event_flags_0;

UINT thread_0_counter = 0;

/* Define what the initial system looks like. */

void thread_0_entry(ULONG thread_input)

{

UINT status;

/* This thread simply sits in while-forever-sleep loop. */

while (1) {

/* Increment the thread counter. */

thread_0_counter++;

/* Sleep for 10 ticks. */

if (thread_0_counter & 1)

tx_thread_sleep(TX_TIMER_TICKS_PER_SECOND / 10);

else

tx_thread_sleep(TX_TIMER_TICKS_PER_SECOND);

/* Set event flag 0 to wakeup thread 5. */

status = tx_event_flags_set(&event_flags_0, 0x1, TX_OR);

/* Check status. */

if (status != TX_SUCCESS)

break;

}

}

void thread_1_entry(ULONG thread_input)

{

UINT status;

ULONG actual_flags;

/* This thread simply waits for an event in a forever loop. */

while (1) {

/* Wait for event flag 0. */

status = tx_event_flags_get(&event_flags_0, 0x1, TX_OR_CLEAR,

&actual_flags, TX_WAIT_FOREVER);

/* Check status. */

if ((status != TX_SUCCESS) || (actual_flags != 0x1))

break;

sysprintf("%s\r\n", __func__);

}

}

void thread_2_entry(ULONG thread_input)

{

/* This thread simply sits in while-forever-sleep loop. */

while (1) {

tx_thread_sleep(TX_TIMER_TICKS_PER_SECOND);

sysprintf("%d\r\n", thread_0_counter);

}

}

/*-----------------------------------------------------------------------------*/

int main(void)

{

sysDisableCache();

sysFlushCache(I_D_CACHE);

sysEnableCache(CACHE_WRITE_BACK);

sysInitializeUART();

sysprintf("\n\n Hello NUC970 !!!\n");

sysprintf("APLL clock %d MHz\n", sysGetClock(SYS_APLL));

sysprintf("UPLL clock %d MHz\n", sysGetClock(SYS_UPLL));

sysprintf("CPU clock %d MHz\n", sysGetClock(SYS_CPU));

sysprintf("System clock %d MHz\n", sysGetClock(SYS_SYSTEM));

sysprintf("HCLK1 clock %d MHz\n", sysGetClock(SYS_HCLK1));

sysprintf("HCLK234 clock %d MHz\n", sysGetClock(SYS_HCLK234));

sysprintf("PCLK clock %d MHz\n", sysGetClock(SYS_PCLK));

tx_kernel_enter();

return 0;

}

void tx_application_define(void *first_unused_memory)

{

CHAR *pointer = TX_NULL;

/* Create a byte memory pool from which to allocate the thread stacks. */

tx_byte_pool_create(&byte_pool_0, "byte pool 0", first_unused_memory, DEMO_BYTE_POOL_SIZE);

/* Put system definition stuff in here, e.g. thread creates and other assorted

create information. */

/* Allocate the stack for thread 0. */

tx_byte_allocate(&byte_pool_0, (VOID **) &pointer, DEMO_STACK_SIZE, TX_NO_WAIT);

/* Create the main thread. */

tx_thread_create(&thread_0, "thread 0", thread_0_entry, 0,

pointer, DEMO_STACK_SIZE,

1, 1, TX_NO_TIME_SLICE, TX_AUTO_START);

/* Allocate the stack for thread 1. */

tx_byte_allocate(&byte_pool_0, (VOID **) &pointer, DEMO_STACK_SIZE, TX_NO_WAIT);

/* Create thread 1. This thread simply pends on an event flag which will be set

by thread_0. */

tx_thread_create(&thread_1, "thread 1", thread_1_entry, 0,

pointer, DEMO_STACK_SIZE,

4, 4, TX_NO_TIME_SLICE, TX_AUTO_START);

/* Allocate the stack for thread 2. */

tx_byte_allocate(&byte_pool_0, (VOID **) &pointer, DEMO_STACK_SIZE, TX_NO_WAIT);

tx_thread_create(&thread_2, "thread 2", thread_2_entry, 0,

pointer, DEMO_STACK_SIZE,

5, 5, TX_NO_TIME_SLICE, TX_AUTO_START);

tx_event_flags_create(&event_flags_0, "event flags 0");

}创建三个任务,和一个事件任务0和任务2通过事件通知,任务1打印任务0中的记数

设置项目引用,包含tx的common/inc和port/arm9/ac5/inc

编译项目,下载测试

这里注意sysprintf并没有做可重入处理,项目中建议需要处理一下

此项目只做移植说明,并没有在目标板实测运行,另外实测的项目相对复杂,不便于讲解.

后记:

filex基于sdnand早前移植过,前后台模式下使用,没有支持os的,后面需要打开一下os再测试一下,下一步需要移植netxduo了,这个还是第一次用.

不足之处还请多多指教

#10 Re: 全志 SOC » 自制了一个F1C100S的板子 » 2023-10-24 12:52:16

#11 全志 SOC » 自制了一个F1C100S的板子 » 2023-10-24 12:49:06

#12 Re: 全志 SOC » SPI NOR FLASH上运行,USB HUB芯片无法识别 » 2023-10-11 23:26:23

#13 Re: 全志 SOC » SPI NOR FLASH上运行,USB HUB芯片无法识别 » 2023-10-08 22:51:49

#14 Re: 全志 SOC » SPI NOR FLASH上运行,USB HUB芯片无法识别 » 2023-10-08 22:51:02

[20231008_22:48:02.948]U-Boot SPL 2020.07 (Oct 08 2023 - 21:45:53 +0800)

[20231008_22:48:02.948]DRAM: 32 MiB

[20231008_22:48:02.948]Trying to boot from MMC1

[20231008_22:48:02.973]Card did not respond to voltage select!

[20231008_22:48:02.973]spl: mmc init failed with error: -95

[20231008_22:48:02.973]Trying to boot from MMC2

[20231008_22:48:02.994]Card did not respond to voltage select!

[20231008_22:48:02.995]spl: mmc init failed with error: -95

[20231008_22:48:02.995]Trying to boot from sunxi SPI

[20231008_22:48:03.690]

[20231008_22:48:03.690]

[20231008_22:48:03.690]U-Boot 2020.07 (Oct 08 2023 - 21:45:53 +0800) Allwinner Technology

[20231008_22:48:03.690]

[20231008_22:48:03.690]CPU: Allwinner F Series (SUNIV)

[20231008_22:48:03.710]Model: Allwinner F1C100s Generic Device

[20231008_22:48:03.711]DRAM: 32 MiB

[20231008_22:48:04.279]MMC: mmc@1c0f000: 0, mmc@1c10000: 1

[20231008_22:48:04.279]Setting up a 480x272 lcd console (overscan 0x0)

[20231008_22:48:04.357]In: serial

[20231008_22:48:04.357]Out: serial

[20231008_22:48:04.357]Err: serial

[20231008_22:48:04.394]Allwinner mUSB OTG (Peripheral)

[20231008_22:48:04.394]Hit any key to stop autoboot: 0

[20231008_22:48:04.394]Card did not respond to voltage select!

[20231008_22:48:04.403]Card did not respond to voltage select!

[20231008_22:48:04.412]SF: Detected w25q128 with page size 256 Bytes, erase size 4 KiB, total 16 MiB

[20231008_22:48:04.412]=========================

[20231008_22:48:04.412]Boot Device: spi

[20231008_22:48:04.423]Boot Slot 0: empty

[20231008_22:48:04.424]Boot Slot 1: spi-nor

[20231008_22:48:04.424]=========================

[20231008_22:48:04.449]SF: Detected w25q128 with page size 256 Bytes, erase size 4 KiB, total 16 MiB

[20231008_22:48:04.449]device 0 offset 0x80000, size 0x80000

[20231008_22:48:05.079]SF: 524288 bytes @ 0x80000 Read: OK

[20231008_22:48:05.094]gpio: pin 134 (gpio 134) value is 1

[20231008_22:48:05.094]DFU waiting on SPI-NOR...

[20231008_22:48:08.096]Booting from SPI-NOR...

[20231008_22:48:08.096]SF: Detected w25q128 with page size 256 Bytes, erase size 4 KiB, total 16 MiB

[20231008_22:48:08.111]device 0 offset 0x100000, size 0x500000

[20231008_22:48:14.516]SF: 5242880 bytes @ 0x100000 Read: OK

[20231008_22:48:14.516]## Loading kernel from FIT Image at 81000000 ...

[20231008_22:48:14.516] Using 'conf@0' configuration

[20231008_22:48:14.528] Trying 'kernel@0' kernel subimage

[20231008_22:48:14.528] Description: Linux kernel

[20231008_22:48:14.528] Type: Kernel Image

[20231008_22:48:14.538] Compression: uncompressed

[20231008_22:48:14.538] Data Start: 0x810000cc

[20231008_22:48:14.538] Data Size: 4889960 Bytes = 4.7 MiB

[20231008_22:48:14.538] Architecture: ARM

[20231008_22:48:14.538] OS: Linux

[20231008_22:48:14.549] Load Address: 0x80000000

[20231008_22:48:14.549] Entry Point: 0x80000000

[20231008_22:48:14.549] Hash algo: crc32

[20231008_22:48:14.549] Hash value: 16e86f7f

[20231008_22:48:14.697] Verifying Hash Integrity ... crc32+ OK

[20231008_22:48:14.697]## Loading fdt from FIT Image at 81000000 ...

[20231008_22:48:14.697] Using 'conf@0' configuration

[20231008_22:48:14.697] Trying 'fdt@0' fdt subimage

[20231008_22:48:14.708] Description: Flattened Device Tree blob

[20231008_22:48:14.708] Type: Flat Device Tree

[20231008_22:48:14.708] Compression: uncompressed

[20231008_22:48:14.719] Data Start: 0x814a9f18

[20231008_22:48:14.719] Data Size: 14403 Bytes = 14.1 KiB

[20231008_22:48:14.719] Architecture: ARM

[20231008_22:48:14.719] Hash algo: crc32

[20231008_22:48:14.749] Hash value: 922387f9

[20231008_22:48:14.749] Verifying Hash Integrity ... crc32+ OK

[20231008_22:48:14.749] Booting using the fdt blob at 0x814a9f18

[20231008_22:48:14.749] Loading Kernel Image

[20231008_22:48:14.827] Loading Device Tree to 817f9000, end 817ff842 ... OK

[20231008_22:48:14.827]

[20231008_22:48:14.827]Starting kernel ...

[20231008_22:48:14.828]

[20231008_22:48:16.211][ 0.000000] Booting Linux on physical CPU 0x0

[20231008_22:48:16.222][ 0.000000] Linux version 5.4.238 (flyaqiao@flyaqiao-laptop) (gcc version 11.4.0 (Buildroot V0.2-26-ga9dc63bf80)) #10 Sat Oct 7 19:48:18 CST 2023

[20231008_22:48:16.233][ 0.000000] CPU: ARM926EJ-S [41069265] revision 5 (ARMv5TEJ), cr=0005317f

[20231008_22:48:16.233][ 0.000000] CPU: VIVT data cache, VIVT instruction cache

[20231008_22:48:16.244][ 0.000000] OF: fdt: Machine model: Sipeed Lichee Nano

[20231008_22:48:16.244][ 0.000000] Memory policy: Data cache writeback

[20231008_22:48:16.245][ 0.000000] cma: Failed to reserve 16 MiB

[20231008_22:48:16.255][ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 8001

[20231008_22:48:16.267][ 0.000000] Kernel command line: console=ttyS0,115200 earlyprintk rootwait init=/preinit root=/dev/mtdblock2 rootfstype=squashfs overlayfsdev=/dev/mtdblock3 net.ifnames=0 vt.global_cursor_default=0

[20231008_22:48:16.277][ 0.000000] Dentry cache hash table entries: 4096 (order: 2, 16384 bytes, linear)

[20231008_22:48:16.289][ 0.000000] Inode-cache hash table entries: 2048 (order: 1, 8192 bytes, linear)

[20231008_22:48:16.289][ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off

[20231008_22:48:16.312][ 0.000000] Memory: 20036K/32256K available (7168K kernel code, 307K rwdata, 1908K rodata, 1024K init, 234K bss, 12220K reserved, 0K cma-reserved)

[20231008_22:48:16.312][ 0.000000] SLUB: HWalign=32, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[20231008_22:48:16.322][ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

[20231008_22:48:16.322][ 0.000049] sched_clock: 32 bits at 24MHz, resolution 41ns, wraps every 89478484971ns

[20231008_22:48:16.333][ 0.000124] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns

[20231008_22:48:16.344][ 0.000945] Console: colour dummy device 80x30

[20231008_22:48:16.344][ 0.001048] Calibrating delay loop... 203.16 BogoMIPS (lpj=1015808)

[20231008_22:48:16.355][ 0.070243] pid_max: default: 32768 minimum: 301

[20231008_22:48:16.355][ 0.070711] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes, linear)

[20231008_22:48:16.366][ 0.070750] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes, linear)

[20231008_22:48:16.366][ 0.072486] CPU: Testing write buffer coherency: ok

[20231008_22:48:16.377][ 0.074981] Setting up static identity map for 0x80100000 - 0x80100058

[20231008_22:48:16.377][ 0.076423] devtmpfs: initialized

[20231008_22:48:16.388][ 0.086794] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[20231008_22:48:16.399][ 0.086859] futex hash table entries: 256 (order: -1, 3072 bytes, linear)

[20231008_22:48:16.399][ 0.087142] pinctrl core: initialized pinctrl subsystem

[20231008_22:48:16.410][ 0.090778] NET: Registered protocol family 16

[20231008_22:48:16.411][ 0.092297] DMA: preallocated 256 KiB pool for atomic coherent allocations

[20231008_22:48:16.421][ 0.094460] cpuidle: using governor menu

[20231008_22:48:16.421][ 0.137669] SCSI subsystem initialized

[20231008_22:48:16.422][ 0.138425] usbcore: registered new interface driver usbfs

[20231008_22:48:16.433][ 0.138589] usbcore: registered new interface driver hub

[20231008_22:48:16.433][ 0.138748] usbcore: registered new device driver usb

[20231008_22:48:16.444][ 0.139292] mc: Linux media interface: v0.10

[20231008_22:48:16.444][ 0.139405] videodev: Linux video capture interface: v2.00

[20231008_22:48:16.455][ 0.139531] pps_core: LinuxPPS API ver. 1 registered

[20231008_22:48:16.455][ 0.139551] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[20231008_22:48:16.466][ 0.139609] PTP clock support registered

[20231008_22:48:16.466][ 0.140365] Advanced Linux Sound Architecture Driver Initialized.

[20231008_22:48:16.478][ 0.143219] clocksource: Switched to clocksource timer

[20231008_22:48:16.488][ 0.144872] simple-framebuffer 81f80000.framebuffer: framebuffer at 0x81f80000, 0x7f800 bytes, mapped to 0x(ptrval)

[20231008_22:48:16.500][ 0.144927] simple-framebuffer 81f80000.framebuffer: format=x8r8g8b8, mode=480x272x32, linelength=1920

[20231008_22:48:16.500][ 0.154326] Console: switching to colour frame buffer device 60x34

[20231008_22:48:16.511][ 0.162567] simple-framebuffer 81f80000.framebuffer: fb0: simplefb registered!

[20231008_22:48:16.511][ 0.190275] thermal_sys: Registered thermal governor 'step_wise'

[20231008_22:48:16.522][ 0.191014] NET: Registered protocol family 2

[20231008_22:48:16.522][ 0.191623] IP idents hash table entries: 2048 (order: 2, 16384 bytes, linear)

[20231008_22:48:16.533][ 0.192938] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 4096 bytes, linear)

[20231008_22:48:16.544][ 0.193060] TCP established hash table entries: 1024 (order: 0, 4096 bytes, linear)

[20231008_22:48:16.544][ 0.193114] TCP bind hash table entries: 1024 (order: 0, 4096 bytes, linear)

[20231008_22:48:16.555][ 0.193159] TCP: Hash tables configured (established 1024 bind 1024)

[20231008_22:48:16.567][ 0.193565] UDP hash table entries: 256 (order: 0, 4096 bytes, linear)

[20231008_22:48:16.567][ 0.193633] UDP-Lite hash table entries: 256 (order: 0, 4096 bytes, linear)

[20231008_22:48:16.578][ 0.194218] NET: Registered protocol family 1

[20231008_22:48:16.578][ 0.196027] RPC: Registered named UNIX socket transport module.

[20231008_22:48:16.589][ 0.196070] RPC: Registered udp transport module.

[20231008_22:48:16.589][ 0.196086] RPC: Registered tcp transport module.

[20231008_22:48:16.600][ 0.196102] RPC: Registered tcp NFSv4.1 backchannel transport module.

[20231008_22:48:16.600][ 0.198418] NetWinder Floating Point Emulator V0.97 (double precision)

[20231008_22:48:16.612][ 0.200218] Initialise system trusted keyrings

[20231008_22:48:16.612][ 0.201167] workingset: timestamp_bits=30 max_order=13 bucket_order=0

[20231008_22:48:16.622][ 0.222525] squashfs: version 4.0 (2009/01/31) Phillip Lougher

[20231008_22:48:16.622][ 0.225319] jffs2: version 2.2. (NAND) (SUMMARY) 漏 2001-2006 Red Hat, Inc.

[20231008_22:48:16.633][ 0.334112] Key type asymmetric registered

[20231008_22:48:16.634][ 0.334156] Asymmetric key parser 'x509' registered

[20231008_22:48:16.645][ 0.334355] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 248)

[20231008_22:48:16.645][ 0.334386] io scheduler mq-deadline registered

[20231008_22:48:16.655][ 0.334406] io scheduler kyber registered

[20231008_22:48:16.655][ 0.336423] sun4i-usb-phy 1c13400.phy: Couldn't request ID GPIO

[20231008_22:48:16.667][ 0.347203] suniv-f1c100s-pinctrl 1c20800.pinctrl: initialized sunXi PIO driver

[20231008_22:48:16.678][ 0.348099] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pa not found, using dummy regulator

[20231008_22:48:16.689][ 0.348459] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pe not found, using dummy regulator

[20231008_22:48:16.689][ 0.370194] Serial: 8250/16550 driver, 8 ports, IRQ sharing disabled

[20231008_22:48:16.700][ 0.376953] printk: console [ttyS0] disabled

[20231008_22:48:16.700][ 0.397272] 1c25000.serial: ttyS0 at MMIO 0x1c25000 (irq = 24, base_baud = 6250000) is a 16550A

[20231008_22:48:16.723][ 0.895964] printk: console [ttyS0] enabled

[20231008_22:48:16.723][ 0.909335] SCSI Media Changer driver v0.25

[20231008_22:48:16.740][ 0.915325] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pc not found, using dummy regulator

[20231008_22:48:16.740][ 0.928397] spi-nor spi0.0: w25q128 (16384 Kbytes)

[20231008_22:48:16.752][ 0.934717] 4 fixed-partitions partitions found on MTD device spi0.0

[20231008_22:48:16.752][ 0.941074] Creating 4 MTD partitions on "spi0.0":

[20231008_22:48:16.769][ 0.945986] 0x000000000000-0x000000070000 : "u-boot"

[20231008_22:48:16.769][ 0.954851] 0x000000100000-0x000000600000 : "kernel"

[20231008_22:48:16.791][ 0.963685] 0x000000600000-0x000000e00000 : "rom"

[20231008_22:48:16.791][ 0.972104] 0x000000e00000-0x000001000000 : "overlay"

[20231008_22:48:16.802][ 0.982232] usbcore: registered new interface driver mt7601u

[20231008_22:48:16.802][ 0.988239] usbcore: registered new interface driver rtl8192cu

[20231008_22:48:16.815][ 0.994305] usbcore: registered new interface driver rtl8xxxu

[20231008_22:48:16.815][ 1.000186] usbcore: registered new interface driver rndis_wlan

[20231008_22:48:16.826][ 1.006332] usbcore: registered new interface driver asix

[20231008_22:48:16.826][ 1.011886] usbcore: registered new interface driver ax88179_178a

[20231008_22:48:16.837][ 1.018188] usbcore: registered new interface driver cdc_ether

[20231008_22:48:16.837][ 1.024248] usbcore: registered new interface driver net1080

[20231008_22:48:16.847][ 1.030017] usbcore: registered new interface driver rndis_host

[20231008_22:48:16.847][ 1.036135] usbcore: registered new interface driver cdc_subset

[20231008_22:48:16.859][ 1.042161] usbcore: registered new interface driver zaurus

[20231008_22:48:16.859][ 1.048079] usbcore: registered new interface driver cdc_ncm

[20231008_22:48:16.870][ 1.053828] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[20231008_22:48:16.871][ 1.060344] ehci-platform: EHCI generic platform driver

[20231008_22:48:16.882][ 1.065935] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

[20231008_22:48:16.882][ 1.072194] ohci-platform: OHCI generic platform driver

[20231008_22:48:16.894][ 1.077947] usbcore: registered new interface driver usb-storage

[20231008_22:48:16.913][ 1.084338] usbcore: registered new interface driver option

[20231008_22:48:16.913][ 1.089985] usbserial: USB Serial support registered for GSM modem (1-port)

[20231008_22:48:16.913][ 1.100326] i2c /dev entries driver

[20231008_22:48:16.925][ 1.107507] at24 0-0050: 65536 byte 24c512 EEPROM, writable, 1 bytes/write

[20231008_22:48:16.941][ 1.117390] rtc-pcf8563 0-0051: low voltage detected, date/time is not reliable.

[20231008_22:48:16.941][ 1.125467] rtc-pcf8563 0-0051: registered as rtc0

[20231008_22:48:16.953][ 1.133147] sunxi-wdt 1c20ca0.watchdog: Watchdog enabled (timeout=16 sec, nowayout=0)

[20231008_22:48:16.967][ 1.142988] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pf not found, using dummy regulator

[20231008_22:48:16.998][ 1.181065] sunxi-mmc 1c0f000.mmc: initialized, max. request size: 16384 KB

[20231008_22:48:17.015][ 1.190462] usbcore: registered new interface driver usbhid

[20231008_22:48:17.016][ 1.196168] usbhid: USB HID core driver

[20231008_22:48:17.016][ 1.204936] NET: Registered protocol family 17

[20231008_22:48:17.026][ 1.209437] lib80211: common routines for IEEE802.11 drivers

[20231008_22:48:17.026][ 1.215419] Key type dns_resolver registered

[20231008_22:48:17.054][ 1.220975] Loading compiled-in X.509 certificates

[20231008_22:48:17.066][ 1.241090] usb_phy_generic usb_phy_generic.0.auto: usb_phy_generic.0.auto supply vcc not found, using dummy regulator

[20231008_22:48:17.066][ 1.252992] musb-hdrc musb-hdrc.1.auto: MUSB HDRC host driver

[20231008_22:48:17.081][ 1.258968] musb-hdrc musb-hdrc.1.auto: new USB bus registered, assigned bus number 1

[20231008_22:48:17.081][ 1.270008] hub 1-0:1.0: USB hub found

[20231008_22:48:17.094][ 1.274088] hub 1-0:1.0: 1 port detected

[20231008_22:48:17.094][ 1.281136] rtc-pcf8563 0-0051: low voltage detected, date/time is not reliable.

[20231008_22:48:17.107][ 1.288667] rtc-pcf8563 0-0051: hctosys: unable to read the hardware clock

[20231008_22:48:17.128][ 1.296281] cfg80211: Loading compiled-in X.509 certificates for regulatory database

[20231008_22:48:17.128][ 1.314309] cfg80211: Loaded X.509 cert 'sforshee: 00b28ddf47aef9cea7'

[20231008_22:48:17.139][ 1.321505] platform regulatory.0: Direct firmware load for regulatory.db failed with error -2

[20231008_22:48:17.139][ 1.330240] cfg80211: failed to load regulatory.db

[20231008_22:48:17.158][ 1.335294] ALSA device list:

[20231008_22:48:17.158][ 1.338275] No soundcards found.

[20231008_22:48:17.181][ 1.348462] VFS: Mounted root (squashfs filesystem) readonly on device 31:2.

[20231008_22:48:17.181][ 1.363560] devtmpfs: mounted

[20231008_22:48:17.181][ 1.371165] Freeing unused kernel memory: 1024K

[20231008_22:48:17.203][ 1.375901] Run /preinit as init process

[20231008_22:48:17.595][ 1.773398] random: crng init done

[20231008_22:48:18.212][ 2.399460] overlayfs: upper fs does not support tmpfile.

[20231008_22:48:18.224][ 2.405007] overlayfs: upper fs does not support xattr, falling back to index=off and metacopy=off.

[20231008_22:48:18.717]Starting syslogd: OK

[20231008_22:48:18.778]Starting klogd: OK

[20231008_22:48:19.042]Running sysctl: OK

[20231008_22:48:19.327]Populating /dev using udev: [ 3.498121] udevd[97]: starting version 3.2.11

[20231008_22:48:19.467][ 3.650272] udevd[98]: starting eudev-3.2.11

[20231008_22:48:22.561]done

[20231008_22:48:22.670]Seeding 256 bits and crediting

[20231008_22:48:22.670]Saving 256 bits of creditable seed for next boot

[20231008_22:48:22.813]Starting haveged: haveged: command socket is listening at fd 3

[20231008_22:48:22.813]OK

[20231008_22:48:23.530]Starting network: ip: SIOCGIFFLAGS: No such device

[20231008_22:48:23.799]ip: SIOCGIFFLAGS: No such device

[20231008_22:48:23.799]FAIL

[20231008_22:48:24.003]Starting uMTPrd: [ 8.178377] file system registered

[20231008_22:48:24.316][ 8.497163] read descriptors

[20231008_22:48:24.316][ 8.500110] read strings

[20231008_22:48:25.307]OK

[20231008_22:48:25.385]Starting kitedtu: OK

[20231008_22:48:25.543]

[20231008_22:48:25.544]Welcome to Sipeed Lichee Nano

[20231008_22:48:27.844]lichee-nano login: [ 12.020873] suniv-f1c100s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pd not found, using dummy regulator这是启动的输出

#15 Re: 全志 SOC » SPI NOR FLASH上运行,USB HUB芯片无法识别 » 2023-10-08 22:50:29

$ ls output/images/ -la

总计 302M

drwxr-xr-x 2 flyaqiao flyaqiao 1M 10月 8 22:33 .

drwxrwxr-x 6 flyaqiao flyaqiao 1M 9月 27 21:42 ..

-rw-r--r-- 1 flyaqiao flyaqiao 8M 10月 8 22:33 bootfs.vfat

-rwxr-xr-x 1 flyaqiao flyaqiao 1M 10月 8 22:32 devicetree.dtb

-rw-r--r-- 1 flyaqiao flyaqiao 5M 10月 8 22:33 kernel.itb

-rw-r--r-- 1 flyaqiao flyaqiao 26M 10月 8 22:33 rootfs.cpio

-rw-r--r-- 1 flyaqiao flyaqiao 7M 10月 8 22:33 rootfs.cpio.gz

-rw-r--r-- 1 flyaqiao flyaqiao 100M 10月 8 22:33 rootfs.ext2

lrwxrwxrwx 1 flyaqiao flyaqiao 1M 10月 8 22:33 rootfs.ext4 -> rootfs.ext2

-rw-r--r-- 1 flyaqiao flyaqiao 9M 9月 27 23:58 rootfs.jffs2

-rw-r--r-- 1 flyaqiao flyaqiao 7M 10月 8 22:33 rootfs.squashfs

-rw-r--r-- 1 flyaqiao flyaqiao 29M 10月 8 22:33 rootfs.tar

-rw-r--r-- 1 flyaqiao flyaqiao 7M 9月 27 23:59 rootfs.tar.gz

-rw-r--r-- 1 flyaqiao flyaqiao 1M 10月 8 22:33 splash.bmp

-rw-r--r-- 1 flyaqiao flyaqiao 128M 10月 8 22:33 sysimage-nand.img

-rw-r--r-- 1 flyaqiao flyaqiao 16M 10月 8 22:33 sysimage-nor.img

-rw-r--r-- 1 flyaqiao flyaqiao 109M 10月 8 22:33 sysimage-sdcard.img

-rw-r--r-- 1 flyaqiao flyaqiao 1M 10月 8 22:31 u-boot.bin

-rw-r--r-- 1 flyaqiao flyaqiao 1M 10月 8 22:33 u-boot-sunxi-with-nand-spl.bin

-rw-r--r-- 1 flyaqiao flyaqiao 1M 10月 8 22:31 u-boot-sunxi-with-spl.bin

-rw-r--r-- 1 flyaqiao flyaqiao 5M 10月 8 22:32 zImage我看了,TF卡上和NOR FLASH上都是加载kernel.itb文件.

#16 全志 SOC » SPI NOR FLASH上运行,USB HUB芯片无法识别 » 2023-10-08 15:06:44

- flyaqiao

- 回复: 6

使用基于buildroot-tiny200-master编译,生成sysimage-nor.img和sysimage-sdcard.img

系统都能正常启动,TF卡运行时,外接接的USB HUB+4G+WIFI都能正常工作.

但在SPI运行sysimage-nor.img时,USB设备就无法识别.lsusb也只有一个usb设备.

一直搞不定,求大神指导...

SPI的启动脚本:

$ cat rootfs/preinit

#!/bin/sh

mount proc /proc -t proc

set -- $(cat /proc/cmdline)

umount /proc

for x in "$@"; do

case "$x" in

overlayfsdev=*)

OVERLAYFSDEV="${x#overlayfsdev=}"

mount -n -t jffs2 ${OVERLAYFSDEV} -o rw,noatime /overlay

mkdir -p /overlay/rom/lower /overlay/rom/upper /overlay/rom/work

mount --rbind / /overlay/rom/lower

mount -n -t overlay overlayfs:/overlay/rom -o rw,noatime,lowerdir=/overlay/rom/lower,upperdir=/overlay/rom/upper,workdir=/overlay/rom/work /tmp

mount --rbind /dev /tmp/dev/

mount --rbind /overlay /tmp/overlay/

exec chroot /tmp /sbin/init

;;

esac

done

exec /sbin/init打包配置:

$ cat genimage-nor.cfg

flash nor-16M {

pebsize = 64K

numpebs = 256

minimum-io-unit-size = 256

}

image sysimage-nor.img {

flash {}

flashtype = "nor-16M"

partition u-boot {

image = "u-boot-sunxi-with-spl.bin"

size = 512K

}

partition splash {

offset = 0x80000

image = "splash.bmp"

size = 512K

}

partition kernel {

offset = 0x100000

image = "kernel.itb"

size = 5M

}

partition rom {

offset = 0x600000

image = "rootfs.squashfs"

}

}页次: 1

- 首页

- » 搜索

- » flyaqiao 发表的帖子