- 首页

- » 搜索

- » fogwizard 发表的帖子

页次: 1

#2 Re: SigmaStar/SSD201/SSD202/SSD212 » 请教SSD20x如何使用jpeg硬件解码? » 2023-12-06 01:09:37

SSD222/222D/222Q是SigmaStar推出的带屏显示和摄像头功能的单芯片嵌入式CPU,采用ARM Cortex A7双核,主频1GHz,内置高性能ISP内核,分别内置64MB DDR2/128MB DDR3/256MB DDR3。内置2D图形引擎和以太网驱动,支持TTL屏显示驱动接口,同时集成了丰富的外围接口,如SAR ADC、音频ADC/DAC、UART、PWM、GPIO和SPI等。支持嵌入式Linux系统,支持Flythings,LittleVGL,AWTK,TD-UI,QT,mini-GUI等多种GUI图形开发界面工具,还可以支持Free RTOS系统,配合LittleVGL图形界面开发产品。

芯片规格

内置高性能ISP内核,最大分辨率1920*1080@30帧;

支持双路MIPI接口摄像头,支持双目活体识别;

支持TTL显示驱动接口,最大分辨率1280*800@60帧;

支持JPEG编码,支持最大分辨率FHD(1920x1080)@30帧;

内置CODEC芯片:3路ADC,支持3路AMIC同时输入,采集,实现2路AMIC+1路AMIC回采;

内置以太网mac+PHY,集成度高,可扩展多网口,实现网关功能;

启动方式支持SPI Nor Flash、SPI Nand Flash、SD card;

嵌入式Linux系统,启动速度快,功耗低。

#4 SigmaStar/SSD201/SSD202/SSD212 » 请教SSD20x如何使用jpeg硬件解码? » 2023-11-14 08:56:01

- fogwizard

- 回复: 4

集成了第三方UI,发现jpeg解码很慢,480*800的jpeg解码耗时高达100毫秒,查询文档,发现有如下描述:

目前 bootlogo 只支持 jpg 图片格式,因为是软件解码,所以图片太大解码速度会很慢,导致出图慢。公版默

认分配的 bootlogo buffer 为 1M,图片的分辨率需要满足 width*height*1.5 < 1M;图片大小需要小于 logo 分区的

大小 128KB

软解性能堪忧,请教能否支持硬解? 谢谢

#8 Re: SigmaStar/SSD201/SSD202/SSD212 » 请教SSD20x的屏接口如何正确设置极性呢 » 2023-10-26 23:32:49

更新状态:

Sstar System Tool运行之前,先在shell运行11111,然后关掉终端,可以读取到稳定的寄存器值,另外也可以在机器上运行riu_r读取,但是极性还是无法调整。

通过寄存器修改展频寄存器,然后打印看到mi_panel0显示的值并不跟着变化,修改H_Total寄存器,mi_panel0的值也不会跟之变化,说明这个驱动并不是实施从寄存器当中读取的,而是drvier里面保存的值:

/config # cat /proc/mi_modules/mi_panel/mi_panel0

PanelName:FPGA_800x480_60

--------------------------------------- PANEL Dev0 Info -------------------------------------

LVDS_POL LVDS_CH LINK_TYPE TI_MODE

0 0 TTL 1

SW_ODD SW_EVEN SW_ODD_RB SW_EVEN_RB

0 0 0 0

H_Total V_Total Width Height H_Start V_Start

512 832 480 800 6 6

hbp hspw hfp vbp vspw vfp

2 4 26 2 4 26

DClk FrameRate INV_DCLK INV_DE InvHSync InvVSync

21 0 0 0 0 0

SSC_Enable SSC_Step SSC_Span TI_BIT Format chnswap

enable 25 192 8BIT 8BIT (0,1,2,3,4)

#9 Re: SigmaStar/SSD201/SSD202/SSD212 » 请教SSD20x的屏接口如何正确设置极性呢 » 2023-10-25 23:07:46

另外根据资料,可以通过读取bank 1129/ 1130的寄存器来确认,但是没有找到读取的方法,帮忙指点一下,谢谢

屏配置的文件如链接:

FPGA_800x480_60.zip

sstardisp.zip

更新状态,在群友的提示下,使用Sstar System Tool读取寄存器,然而发现多次读取的值一直在变化,整个bank都在变化,是工具的使用方法问题吗?谢谢

#10 SigmaStar/SSD201/SSD202/SSD212 » 请教SSD20x的屏接口如何正确设置极性呢 » 2023-10-25 22:54:28

- fogwizard

- 回复: 6

使用SSD201连接RGB的屏,检查发现VS/HS信号反向了,屏幕要求HS/VS是低有效,然后抓上来的波形如下图:

修改配置配置文件的如下内容:

///////////////////////////////////////////////

// For TTL Only

///////////////////////////////////////////////

0, //MS_U8 m_ucPanelDCLKDelay; ///< PANEL_DCLK_DELAY

0, //MS_U8 m_bPanelInvDCLK :1; ///< MOD_4A[4], PANEL_INV_DCLK

0, //MS_U8 m_bPanelInvDE :1; ///< MOD_4A[2], PANEL_INV_DE

1, //MS_U8 m_bPanelInvHSync :1; ///< MOD_4A[12], PANEL_INV_HSYNC

1, //MS_U8 m_bPanelInvVSync :1; ///< MOD_4A[3], PANEL_INV_VSYNC

修改后,通过cat mi_panel0节点可以看到打印的InvHSync/InvVSync指有变化,然而实际测量信号还是高有效

设置成1:1:

PanelName:FPGA_800x480_60

--------------------------------------- PANEL Dev0 Info -------------------------------------

LVDS_POL LVDS_CH LINK_TYPE TI_MODE

0 0 TTL 1

SW_ODD SW_EVEN SW_ODD_RB SW_EVEN_RB

0 0 0 0

H_Total V_Total Width Height H_Start V_Start

512 832 480 800 6 6

hbp hspw hfp vbp vspw vfp

2 4 26 2 4 26

DClk FrameRate INV_DCLK INV_DE InvHSync InvVSync

21 0 0 0 1 1

SSC_Enable SSC_Step SSC_Span TI_BIT Format chnswap

enable 25 192 8BIT 8BIT (0,1,2,3,4)

设置成0:0:

PanelName:FPGA_800x480_60

--------------------------------------- PANEL Dev0 Info -------------------------------------

LVDS_POL LVDS_CH LINK_TYPE TI_MODE

0 0 TTL 1

SW_ODD SW_EVEN SW_ODD_RB SW_EVEN_RB

0 0 0 0

H_Total V_Total Width Height H_Start V_Start

512 832 480 800 6 6

hbp hspw hfp vbp vspw vfp

2 4 26 2 4 26

DClk FrameRate INV_DCLK INV_DE InvHSync InvVSync

21 0 0 0 0 0

SSC_Enable SSC_Step SSC_Span TI_BIT Format chnswap

enable 25 192 8BIT 8BIT (0,1,2,3,4)

#13 Re: 8051/STC8/AT89C51/N76E003 » 开源一个USB切换器 » 2022-01-05 08:20:53

#14 Re: 8051/STC8/AT89C51/N76E003 » 开源一个USB切换器 » 2022-01-05 08:14:36

#15 Re: 8051/STC8/AT89C51/N76E003 » 开源一个USB切换器 » 2022-01-05 08:13:45

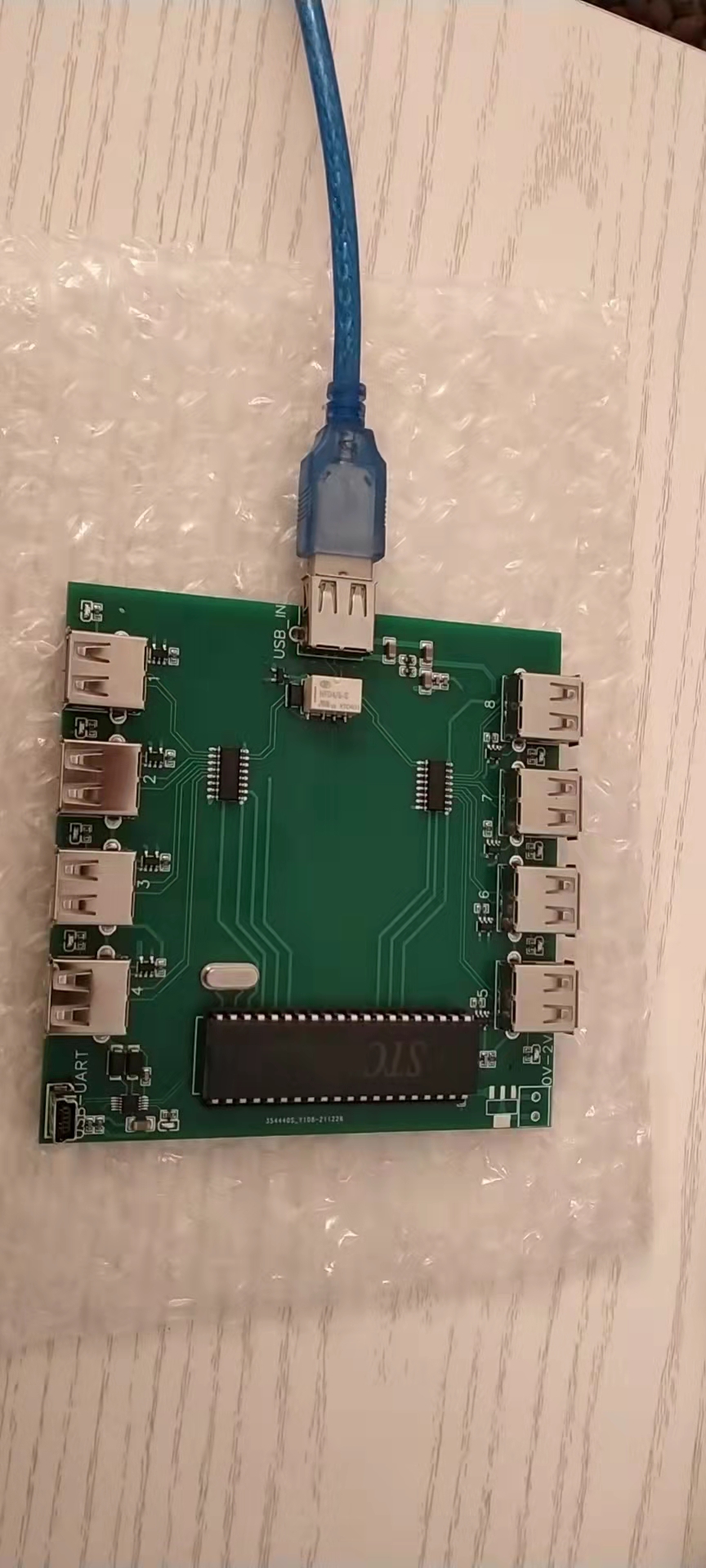

#16 8051/STC8/AT89C51/N76E003 » 开源一个USB切换器 » 2021-12-26 11:17:14

- fogwizard

- 回复: 8

在实际的工作生活中,经常有类似需求:

(1)只有一个USB设备,但是需要连接多台电脑。

(2)一台嵌入式设备,需要连接多个USB设备做测试

常规解决方法是人工拔插USB接口,一直都是这么做的

直到最近忍无可忍无需在忍,做了一个USB的切换开关,

期望彻底解决问题。

原理图PCB如附件,目前已经制版贴片,程序还没开始调试,

待验证okay再上传,谢谢

PCB_usb-host-switch-v1_2021-12-25.zip

Schematic_usb-host-switch_2021-12-26.pdf

#18 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » LVGL的linux_frame_buffer项目加入FB双缓 » 2021-02-22 09:31:29

#19 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » LVGL的linux_frame_buffer项目加入FB双缓 » 2021-02-19 22:10:42

#20 Re: SigmaStar/SSD201/SSD202/SSD212 » 启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃 » 2021-02-19 15:26:10

#21 Re: SigmaStar/SSD201/SSD202/SSD212 » 有一个对标F1C800的芯片SigmaStar SSD201有谁了解吗 双核A7 » 2021-02-19 13:48:09

#22 Re: SigmaStar/SSD201/SSD202/SSD212 » 启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃 » 2021-02-19 13:45:59

#23 Re: 全志 SOC » F1C200S PDA手持机调试 » 2020-06-17 09:25:37

#24 Re: 全志 SOC » F1C200S PDA手持机调试 » 2020-06-16 11:33:47

#25 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 总想搞个什么东西出来,靓绝五台山的那种,大伙有没有这种感觉? » 2020-04-09 10:20:34

#30 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 感谢@weiyongwill 赠送的某银行淘汰终端机,AM3354 CPU,运行Android【开车了, 凑满50台就发车, 60元+运费】 » 2019-12-13 15:56:37

#31 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 感谢@weiyongwill 赠送的某银行淘汰终端机,AM3354 CPU,运行Android【开车了, 凑满50台就发车, 60元+运费】 » 2019-12-13 15:53:09

#32 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 感谢@weiyongwill 赠送的某银行淘汰终端机,AM3354 CPU,运行Android【开车了, 凑满50台就发车, 60元+运费】 » 2019-12-09 14:15:50

#34 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 感谢@weiyongwill 赠送的某银行淘汰终端机,AM3354 CPU,运行Android【开车了, 凑满50台就发车, 60元+运费】 » 2019-12-02 15:10:16

#35 Re: 全志 SOC » F1C100S linux-4.15 无法软件重启的问题原因 » 2019-11-26 09:45:08

#37 Re: 全志 SOC » miyoo游戏机横版拆机 » 2019-11-25 16:51:30

#38 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 下单买了一个 汇顶 GT911/GT9xx 电容触摸屏产测工具 » 2019-04-20 15:41:26

#40 Re: 全志 SOC » 请教F1C100S lradc 不产生中断问题 » 2019-03-23 18:19:37

https://whycan.cn/t_1728.html

链接分享的是音频口作adc,我这边只是想把f1c100s的keyadc用起来而已,还没到用音频adc这个层次,谢谢。

#41 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » 要是linux的外设驱动可以做到用户层就好了 » 2019-03-23 15:25:08

#42 Re: 全志 SOC » 请教F1C100S lradc 不产生中断问题 » 2019-03-23 12:09:13

#43 Re: 全志 SOC » 请教F1C100S lradc 不产生中断问题 » 2019-03-23 12:04:48

#44 Re: 全志 SOC » 设计一片 SD NAND + JTAG(全志soc) 转接板 [切记切记0.8mm厚度] » 2019-03-23 10:23:43

重新上电,不会再报error了,这回坑有点小 :-)

Connecting to target via JTAG

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x07926F0F, IRLen: 04, ARM926EJ-S Core

CP15.0.0: 0x41069265: ARM, Architecure 5TEJ

CP15.0.1: 0x1D152192: ICache: 32kB (4*256*32), DCache: 16kB (4*128*32)

Cache type: Separate, Write-back, Format C (WT supported)

ARM9 identified.

J-Link>

#45 Re: 全志 SOC » 设计一片 SD NAND + JTAG(全志soc) 转接板 [切记切记0.8mm厚度] » 2019-03-23 10:19:49

reply@20

仔细对硬件发现硬件铜箔连接跟晕哥的一致(仅是无上拉无sdnand芯片,上拉nano板子应该是有的),猜想会不会是

因为系统已经跑起来了,jtag无法使用了呢? 进入下载模式,再连jtag, 这回可以发现926EJ-S了,但是后面还是有

报错,继续填坑...

J-Link>connect

Device "ARM9" selected.

Connecting to target via JTAG

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x07926F0F, IRLen: 04, ARM926EJ-S Core

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x07926F0F, IRLen: 04, ARM926EJ-S Core

****** Error: CPU-TAP not found in JTAG chain

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x07926F0F, IRLen: 04, ARM926EJ-S Core

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x07926F0F, IRLen: 04, ARM926EJ-S Core

****** Error: CPU-TAP not found in JTAG chain

Cannot connect to target.

#46 Re: 全志 SOC » 请教F1C100S lradc 不产生中断问题 » 2019-03-23 08:52:48

根据 https://whycan.cn/t_1916.html 的信息,中断号改成30/34,表现均一致。

#47 全志 SOC » 请教F1C100S lradc 不产生中断问题 » 2019-03-22 20:56:08

- fogwizard

- 回复: 22

根据Document下的文档,文件suniv-f1c100s-licheepi-nano.dts增加:

/dts-v1/;

#include "suniv-f1c100s.dtsi"

+#include "suniv-lradc.dtsi"

#include <dt-bindings/gpio/gpio.h>

@@ -46,6 +47,12 @@

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

};

+ reg_vcc3v0: vcc3v0 {

+ compatible = "regulator-fixed";

+ regulator-name = "vcc3v0";

+ regulator-min-microvolt = <3000000>;

+ regulator-max-microvolt = <3000000>;

+ };

新增 suniv-lradc.dtsi,内容如下:

#include <dt-bindings/input/input.h>

/ {

lradc:

lradc@1c22800 {

compatible = "allwinner,sun4i-a10-lradc-keys";

reg = <0x01c22800 0x100>;

interrupts = <31>;

vref-supply = <®_vcc3v0>;

button@191 {

label = "Volume Up";

linux,code =

<KEY_VOLUMEUP>;

channel = <0>;

voltage = <191274>;

};

button@392 {

label = "Volume Down";

linux,code =

<KEY_VOLUMEDOWN>;

channel = <0>;

voltage = <392644>;

};

button@601 {

label = "Menu";

linux,code = <KEY_MENU>;

channel = <0>;

voltage = <601151>;

};

button@795 {

label = "Enter";

linux,code =

<KEY_ENTER>;

channel = <0>;

voltage = <795090>;

};

button@987 {

label = "Home";

linux,code =

<KEY_HOMEPAGE>;

channel = <0>;

voltage = <987387>;

};

};

};

(内核使用git clone https://github.com/Icenowy/linux.git)

现象为:系统起来之后会生成event0, 然而改变lradc引脚的电压,并没有按键事件

产生,查看adc的中断数,一直是0,是否还有其他地方需要设置? 谢谢

#48 Re: 全志 SOC » 网友 @chong 大神提供的f1c100s mainline linux usb 补丁包,支持usb otg(host & device) » 2019-03-19 11:34:41

感谢网友开源,参照文档 https://whycan.cn/files/members/1304/USB.pdf,

ubuntu可以出一张usb0网卡也可以配置ip地址,但是在板子上ifconfig,没有任何信息,有遇到一样

问题的吗? 谢谢

#49 Re: 全志 SOC » F1c100s 开始进入主线内核了 » 2019-03-19 11:19:39

页次: 1

- 首页

- » 搜索

- » fogwizard 发表的帖子