- 首页

- » 搜索

- » msr06rr 发表的帖子

页次: 1

#2 ESP32/ESP8266 » ESP32 硬件驱动 DShot 数字电机 » 2022-05-19 15:29:45

- msr06rr

- 回复: 0

官方最近推送了若干新的example,其中有一个很有意思的example: https://github.com/espressif/esp-idf/tree/master/examples/peripherals/rmt/dshot_esc

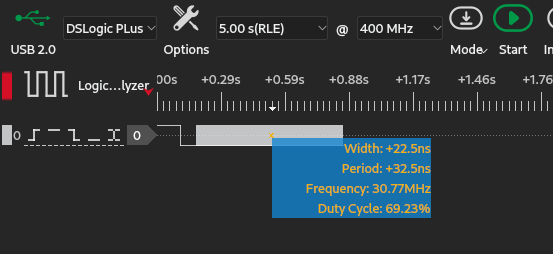

使用RMT驱动数字电机,走的DShot协议。这个协议要求的时间精度挺严格的,发送的帧间间隔是几十个微妙,如果在定时器中断中发送命令帧,对CPU来说太浪费了。这个example别出心裁采用了RMT外设的无限循环发送模式,CPU基本上处于乘凉模式了。

#4 Re: 全志 SOC » 【全开源/D1s】芒果派麻雀 MangoPi-MQ1 基于D1s 的 RISC-V Linux小板 【最新消息:淘宝开卖了,链接在一楼】 » 2021-12-06 10:21:06

#6 Re: ESP32/ESP8266 » ESP-IDF 有了自己的包管理器 » 2021-09-24 13:57:46

使用demo在这里: https://github.com/espressif/esp-idf/tree/master/examples/peripherals/lcd/lvgl

也是移植的最新版本LVGL

#8 ESP32/ESP8266 » ESP-IDF 有了自己的包管理器 » 2021-09-10 15:43:08

- msr06rr

- 回复: 1

最近在玩 LVGL v8,发现IDF已经把它做成了一个package: https://components.espressif.com/component/lvgl/lvgl

查了一下用法,非常简单,只需要在项目的main目录下加一个 idf_component.yml,在里面指定依赖的库文件

dependencies:

idf: ">=4.4"

lvgl/lvgl: "==8.0.2"然后在你第一次运行 idf.py 的时候,会自动给你从registry 上把他下载下来,有亿点点好用.

虽然esp32不是第一个做嵌入式包管理器的,但是总算是开始有了,希望生态圈壮大起来.

PS:官方文档在这里: https://docs.espressif.com/projects/esp-idf/en/latest/esp32/api-guides/tools/idf-component-manager.html

#9 Re: ESP32/ESP8266 » 乐鑫 ESP32-C3 功能介绍 » 2021-08-23 10:55:01

#12 Re: ESP32/ESP8266 » ESP32-C3片子好像出来了 » 2021-04-13 12:43:05

数据手册/参考手册已经出来了,目前还不全,但是CPU章节已经有了 https://www.espressif.com/sites/default/files/documentation/esp32-c3_technical_reference_manual_en.pdf

C3中的USB device只能用来做调试串口和USB-JTAG使用,手册中的名字叫“USB Serial/JTAG controller”

#13 Re: ESP32/ESP8266 » ESP32-C3片子好像出来了 » 2021-04-09 10:55:55

#14 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » esp32-s3发布 » 2021-01-04 13:42:33

#15 Re: ESP32/ESP8266 » esp32s2移植VSF,顺便跑起USB主机协议栈 » 2020-12-20 16:38:36

楼主牛逼,建议给官方提PR...

SDK暂时没有host驱动,但是从这里发布的进度来看似乎是有这个计划的:https://esp32.com/viewtopic.php?f=10&t=14532

#17 Re: ESP32/ESP8266 » 求解esp-wrover-kit无法烧写 » 2020-06-22 10:44:10

#19 Re: ESP32/ESP8266 » 测试了一下 ESP32-S2 的专用 GPIO 最高翻转速度有 60MHz » 2020-06-04 13:22:48

看大佬的代码,用上汇编会快很多 https://gist.github.com/igrr/1515d369310479bbaf9239afeed4aac5

#20 Re: ESP32/ESP8266 » esp32有解压zip文件的库吗??? » 2020-06-02 19:00:48

我记得ESP32的ROM中自带miniz库,你可以试试 https://github.com/espressif/esp-idf/blob/master/components/esp_rom/include/esp32/rom/miniz.h

#21 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » 乐鑫ESP32 提供的 littlevgl demo » 2020-05-28 13:41:41

再来一个esp32上的移植

https://github.com/lvgl/lv_port_esp32

#23 Re: ESP32/ESP8266 » 乐鑫的esp32-s2模组和开发板上市了 » 2020-05-07 10:54:10

#24 Re: 全志 SOC » 大家的从github是怎么下载代码的?【求助】 » 2020-03-27 11:28:22

#25 Re: 全志 SOC » 大家的从github是怎么下载代码的?【求助】 » 2020-03-26 16:34:10

#27 Re: ESP32/ESP8266 » 乐鑫的esp32-s2模组和开发板上市了 » 2020-03-13 18:01:11

USB 已经有了(我没去试,因为没有板子),用的tinyusb开源代码:https://github.com/espressif/esp-idf/tree/master/components/tinyusb

开发文档确实不多, 看了一下这个文档,感觉和ESP32的开发方式差不多吧:https://github.com/espressif/esp-idf/blob/master/docs/en/get-started/index.rst

一整套工具链一个命令就给你全部安装好了。麻烦的是,构建系统改成CMake了,不过我个人挺喜欢CMake的。

另外数据手册,参考手册已经在官网有的下载了,喜欢徒手撸寄存器的已经可以开始了。

#28 Re: 全志 SOC » 发个自编的适用f1c100S和荔枝派nano的GCC6.5 » 2020-01-15 13:18:26

#32 Re: NXP i.MX6UL/6ULL » whycan 免费借用未拆封的正点原子i.MX6UL开发板, 本站积分300网友私信QQ 516333132 » 2019-11-08 14:22:10

#33 Re: 全志 SOC » 尝试从零构建F1C100s开发环境 » 2019-11-07 13:20:03

#34 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 一年一度双十一又来到,大家的购物车里面有什么值得推荐的性价比商品? » 2019-11-06 15:04:18

#38 Re: RISC-V » 好消息,现在可以将 Longan Nano 变成 RISC-V 仿真器,用来调试 GD32VF103(将来会支持更多 RISC-V MCU) » 2019-09-29 11:35:40

#39 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 野火开始预售imx6ull开发板了,价格还不错。 » 2019-09-26 17:11:46

#41 Re: ESP32/ESP8266 » 使用ESP32的RMT驱动WS2812 » 2019-08-07 17:38:28

#42 Re: ESP32/ESP8266 » 使用ESP32的RMT驱动WS2812 » 2019-08-07 17:37:16

#44 Re: ESP32/ESP8266 » esp32s2板子开箱贴 » 2019-08-06 21:23:31

#45 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 立创商城 100万现金券 10000张100元现金券,6月6日-21日每天10:00、16:00准点开抢! » 2019-06-14 11:15:34

#46 Re: 全志 SOC » 全志又发马甲了 » 2019-06-04 17:11:12

#47 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » ZLG开源 GUI 引擎 AWTK 1.1 发布 » 2019-05-30 16:21:43

#48 Re: ESP32/ESP8266 » 比ESP8266性价比更优的wifi芯片来了 ----- W600 » 2019-05-28 17:49:28

来玩ESP32S2吧,感觉可玩性很大,相比esp32,少了蓝牙,多了OTG,DVP,LCD

https://www.espressif.com/en/news/espressif-announces-%E2%80%A8esp32-s2-secure-wi-fi-mcu

#51 Re: 全志 SOC » 感谢华嵌HQEmbed赠送的 漂亮高颜值S3 开发板 (底板 + 核心板) » 2019-04-18 18:50:15

这个也是开源低成本的,嗯,还有更低的GK7102,64M内存的,挺适合做产品的

是这个吗 https://item.taobao.com/item.htm?spm=a1z10.5-c.w4002-18648826825.11.63d034f2EBI05C&id=583903053607

#54 Re: ESP32/ESP8266 » ESP32+mDNS+HTTP Server的方案验证 » 2019-04-11 12:10:16

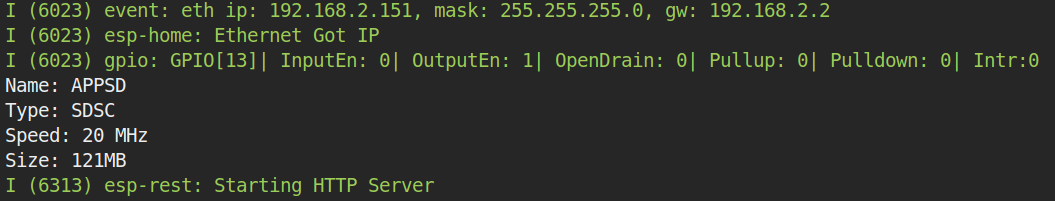

发现编译后的website不是很大,2M不到,塞到SPI Flash 中刚刚好啊,实测下来速度还不如SD卡。

IDF中有一个好用的制作spiffs bin 文件的工具,目前已经集成到编译系统当中,只需要在Makefile中指定好文件目录,就能在编译阶段自动制作bin,烧写阶段自动烧写到SPI Flash中的指定分区中,超级无敌爽,无需额外的命令行操作。教程:https://docs.espressif.com/projects/esp-idf/en/latest/api-reference/storage/spiffs.html

#55 Re: ESP32/ESP8266 » ESP32+mDNS+HTTP Server的方案验证 » 2019-04-08 13:57:49

msr06rr 说:这个是用 spi 还是 sdio 访问 sd nand 芯片?

SDIO接口

#57 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-04 14:52:32

#64 Re: ESP32/ESP8266 » ESP32+mDNS+HTTP Server的方案验证 » 2019-03-28 15:48:04

https://github.com/espressif/esp-idf/tree/master/examples/storage/semihost_vfs

确切的说是ESP32控制JTAG,通过JTAG来做IO操作。IDF还将这种semihost封装在了VFS上,所以在esp32上用open,read,write等方式操作PC上的文件。

#65 Re: ESP32/ESP8266 » ESP32+mDNS+HTTP Server的方案验证 » 2019-03-28 15:31:21

更新...

小型嵌入式Web开发(不跑Linux)有一个痛点是如何在开发阶段快速迭代,不可能每次修改html代码就要重新烧写程序,哪怕是放在SD卡上,每次插拔也很蛋疼,可能修改html只要几秒,但是部署一次就要花1分钟。

所以就想到了semihost方式的开发,相当于是热部署吧。只要后端程序不改变,就不需要重新烧固件,不需要插拔SD卡,连着JTAG就完事了。

过程如下:

浏览器向esp32发送GET请求,esp32根据请求地址,从host主机端检索文件,然后发送响应数据包给浏览器。网页文件都在host端,基本可以实现开发阶段的热更新,“实时”预览。只是这个实时性能还要看JTAG速度有多快了。

实际测试,VUE编译后大约550K的网站,每次刷新需要5秒左右的时间。

#66 ESP32/ESP8266 » ESP32+mDNS+HTTP Server的方案验证 » 2019-03-22 12:32:10

- msr06rr

- 回复: 29

一直觉得ESP32+液晶屏不是物联网GUI最佳方案(当然也有必须要液晶屏的场合),好的液晶屏成本高,想要做酷炫的界面还依赖GUI引擎(很多还是收费的)。但是Web就不同了,做个酷炫的显示界面,有一堆开源前端框架,比如Vue。

最近有空尝试用Vue写个前端,编译后部署在SD卡上。后端的程序不用很复杂,基于IDF现有的组件,实现几条简单的REST API还是没问题的吧。

主要网页中的URL这个有点蛋疼,因为DHCP分到的IP地址是会发生变化

好在局域网中可以使用mDNS,IDF中也已经包含了这个组件,开箱即用

这种方案有个弊端,就是操作系统要支持mDNS才行,Ubuntu自带avahi,mac自带bonjour,但是windows和Android我就不知道了,还没试过。

#67 Re: 全志 SOC » 30元 双层板 S3 发去打样了,就看今天能不能过复审了 » 2019-03-22 10:50:12

#68 Re: 全志 SOC » 晒晒3D打印的小智极客 S3 BOX外壳 » 2019-03-14 10:19:04

#69 Re: 全志 SOC » BITC200(F1c200s/100s)手工焊接简直焊瞎了眼 » 2019-02-27 11:09:51

#70 Re: ST/STM8/STM8S/STM8L » ST要出A7+M4的多核处理器了。 » 2019-02-22 12:49:42

#71 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » QQ这种炫酷效果是怎么实现的? » 2019-02-21 19:51:09

怎么实现的不知道,但是碰巧最近刚看到一个类似的效果,有一款基于electron的UI库,可以参考

https://segmentfault.com/a/1190000016894422?utm_source=tag-newest

#72 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 想学习一下CMake,这份资料不错,但是我没有积分下载,有谁能帮忙吗? » 2019-02-20 17:12:04

晕哥,挺你!

#73 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 想学习一下CMake,这份资料不错,但是我没有积分下载,有谁能帮忙吗? » 2019-02-20 15:55:21

- msr06rr

- 回复: 4

找了好久,只有CSDN上有下载资源(这奇怪,为什么都喜欢放在CSDN上呢?)

链接地址:https://download.csdn.net/download/lnjzwzh/10749587

哪位好心人可以帮忙下载一下吗,感谢~

#74 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-02-19 21:19:24

#75 Re: 全志 SOC » Linux-Box,3D外壳收到了,晒晒 » 2019-02-19 18:35:48

屏幕方便给个连接吗

#77 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » littlevgl 绑定 python (micropython) 脚本项目 ---- lv_mpy » 2019-01-08 13:47:09

#78 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 好消息, github.com 免费账户也可以创建私有仓库了 » 2019-01-08 10:13:09

#80 Re: ESP32/ESP8266 » ESP32+SIM800L实现MQTT功能 » 2018-12-26 15:56:12

#82 ESP32/ESP8266 » ESP32+SIM800L实现MQTT功能 » 2018-12-26 15:14:34

- msr06rr

- 回复: 5

断断续续搞了好一阵子终于可以在SIM800L上跑MQTT了。

SIM800L本身是不支持MQTT的,但是模块本身很小巧很便宜,也很稳定。我就不喜欢什么功能都封装成AT指令,明明这些可以自己用软件来实现的,平白无故还增加了成本。

说说具体做法,其实在ESP32上已经很容易做到了,IDF本身有MQTT协议栈(基于lwip写的),并且lwip又支持PPP接口,所以我们只要让Modem正确进入PPP模式,然后调用mqtt的api即可。

话说回来,进入PPP模式还是要发AT指令的,好在也就那几条通用的指令。

I (1275) pppos_demo: Module: SIMCOM_SIM800L

I (1275) pppos_demo: Operator: "CHINA MOBILE"

I (1275) pppos_demo: IMEI: 865992039850864

I (1275) pppos_demo: IMSI: 460007454185220

I (1475) pppos_demo: rssi: 21, ber: 0

I (1675) pppos_demo: Battery voltage: 4652 mV

I (1875) pppos_demo: Modem PPP Started

I (2685) pppos_demo: Modem Connect to PPP Server

I (2685) pppos_demo: ~~~~~~~~~~~~~~

I (2685) pppos_demo: IP : 10.64.167.151

I (2685) pppos_demo: Netmask : 255.255.255.255

I (2695) pppos_demo: Gateway : 192.168.254.254

I (2695) pppos_demo: Name Server1: 211.136.112.50

I (2705) pppos_demo: Name Server2: 211.136.150.66

I (2705) pppos_demo: ~~~~~~~~~~~~~~

I (2715) system_api: Base MAC address is not set, read default base MAC address from BLK0 of EFUSE

I (3815) MQTT_CLIENT: Sending MQTT CONNECT message, type: 1, id: 0000

I (4585) pppos_demo: MQTT_EVENT_CONNECTED

I (4595) pppos_demo: sent subscribe successful, msg_id=25635

I (8785) pppos_demo: MQTT_EVENT_SUBSCRIBED, msg_id=25635

I (8785) pppos_demo: sent publish successful, msg_id=0

I (10105) MQTT_CLIENT: deliver_publish, message_length_read=26, message_length=26

I (10105) pppos_demo: MQTT_EVENT_DATA

TOPIC=/topic/qos0

DATA=esp32-pppos

I (10155) pppos_demo: Modem PPP Stopped

I (13155) pppos_demo: Power down#84 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-25 14:44:14

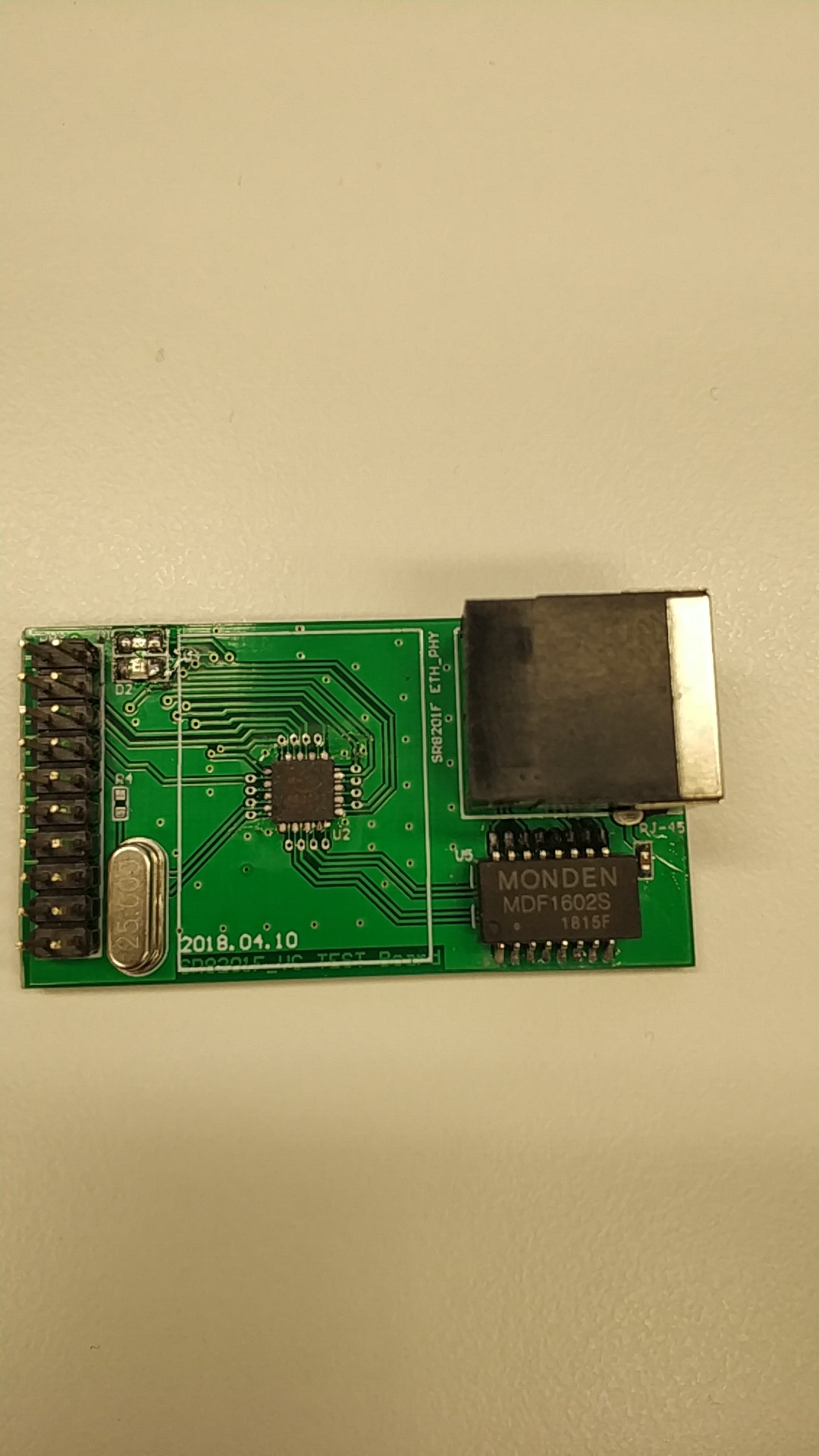

再上传一个参考设计吧,不敢独享

https://whycan.cn/files/members/421/sr8201f_rmii_v11.pdf

#85 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-25 14:39:13

官方给的数据手册

https://whycan.cn/files/members/421/CoreChips-SR8201F-datasheet.pdf

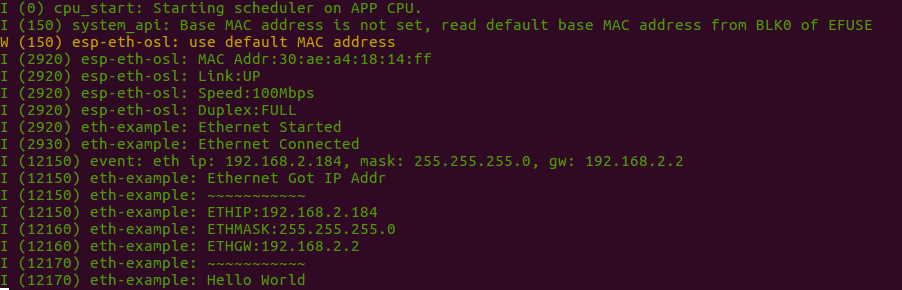

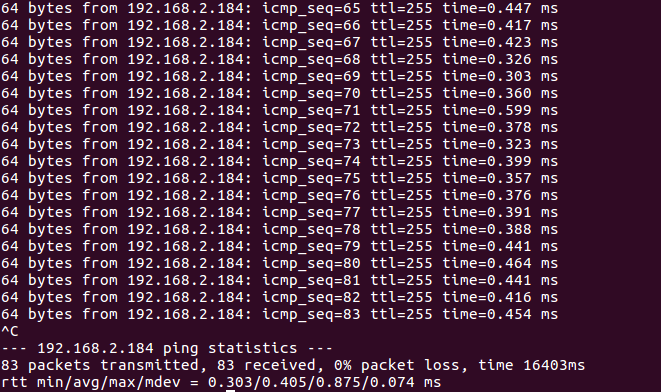

目前已经用ESP32驱动起来了,直接使用ESP32的GPIO17输出50MHz时钟给SR8201F,省了一颗晶振。想用ESP32以太网的真心建议这么搞,性价比很高的。

#86 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-24 11:11:56

#87 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-24 11:01:03

#88 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-20 11:07:57

#89 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-20 10:31:36

#90 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-19 17:23:05

#91 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-19 17:06:05

https://item.szlcsc.com/46225.htmll

lan8720 未税价格 1.5 - 2.0元

LAN8720是不错,稳妥!仅支持RMII模式,可以说十分精简,发热控制也很好。

#92 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-19 16:49:42

#93 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-19 16:48:20

— SR8201F是公司100M以太网PHY SR8201G的升级版SR8201G是和芯润德2013年自主研发推出第一颗100M以太网PHY,管脚自定义,公司代理和客户更希望我们的管脚可以做到跟RTL或IC+的做兼容,方便替换使用;于是我们推出了SR8201F,一颗和RTL8201F的管脚兼容的产品,针对原使用RTL8201F的客户,工程师不需要做硬件改版的动作就可以使用到我们性价比更高的SR8201F。

— SR8201F是一颗MII/RMII接口(简化介质无关接口)的单芯片、单端口10/100M以太网物理层收发器电路。SR8201F实现了10/100M以太网物理层所有功能,包括:物理编码子层(PCS),物理媒介适配层(PMA),双绞线物理介质关联层(PMD),10Base-TX编码/解码器,和双绞线媒体接入单元(TPMAU)。

— SR8201F采用高级CMOS工艺设计以满足低电压低功耗要求。通过内部集成的DSP技术,芯片在各种条件下都能获得极佳的性能。

#94 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-19 16:44:05

#95 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-19 16:42:17

#96 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现一款性价比很高的以太网PHY---SR8201F,只要1.5元! » 2018-12-19 16:40:29

- msr06rr

- 回复: 27

淘宝链接:https://item.taobao.com/item.htm?spm=a230r.1.14.42.6b4e4a78XrpNDr&id=571509034428&ns=1&abbucket=16#detail

淘宝上目前只有卖芯片的,没有看到模块,还想试试来着的

#97 Re: 全志 SOC » flash 1,4 pin » 2018-12-11 15:51:12

#98 Re: ESP32/ESP8266 » 比ESP8266性价比更优的wifi芯片来了 ----- W600 » 2018-12-08 16:35:36

msr06rr 说:这个没引出SWD,不能?Link。

另外这芯片的wifi驱动(仅提供库,无源码)有问题,收不到多播报文。

没玩过这款芯片,wifi驱动不开源也是常态了。不支持多播多半是mac filter那块配置的问题,查一下是否提供了相应的api

#101 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » GTI SPR2801芯片是何方神圣? » 2018-11-23 10:14:00

- msr06rr

- 回复: 2

来自硅谷的新公司https://www.gyrfalcontech.ai/,第一代产品就非常惊艳SPR2801S

他们做的神经网络计算棒NCS要比英特尔的那款强90倍,英特尔的那款只能做预测,GTI的这款不同了,还能训练,功耗还很低。GTI这款产品的设计理念比较超前,已经做到了在内存中原位计算,并且是可以不用CPU参与训练的(不知道自己的理解对不对)。按照GTI创始人的意思,机器学习是个自由的学习过程,不需要指令集那一套东西。

国内现在使用这款芯片做模块或者USB Dongle的已经有三家了(从淘宝上找得到的)

1. 若派Ropal:https://item.taobao.com/item.htm?spm=a1z0d.6639537.1997196601.4.a05f7484jx2O1T&id=579240843508

2. 萤火虫开源:https://item.taobao.com/item.htm?spm=a1z0d.6639537.1997196601.15.a05f7484jx2O1T&id=582266224782

3. orange pi:https://item.taobao.com/item.htm?spm=a1z0d.6639537.1997196601.35.a05f7484jx2O1T&id=581922028481

这个香橙派真的是太吊了,我购物车还有一堆它们的板子。。。

重点来了:

哪位论坛大神能够带我们上车,带我们飞,这玩意比较新,不太会玩啊

#102 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 围观本站网友 @演技担当黄晓明 拆解 FE-5680A 原子钟 » 2018-11-23 10:01:01

#103 Re: 全志 SOC » f1c100s使用usb wifi上网 » 2018-11-19 21:33:41

#104 全志 SOC » f1c100s使用usb wifi上网 » 2018-11-18 14:31:05

- msr06rr

- 回复: 10

双十一买了个便宜的USB WiFi网卡,正好用在nano上,可以工作。

https://detail.tmall.com/item.htm?id=557545076086&spm=a1z09.2.0.0.78c62e8dECmDSF&_u=i98jou47790

查了一下是MT7601u的芯片,linux4.2版本开始就已经支持了,驱动都不用做任何改动,开启就能用。

# ping www.baidu.com

PING www.baidu.com (112.80.248.75): 56 data bytes

64 bytes from 112.80.248.75: seq=0 ttl=57 time=10.495 ms

64 bytes from 112.80.248.75: seq=1 ttl=57 time=11.228 ms

64 bytes from 112.80.248.75: seq=2 ttl=57 time=10.667 ms

64 bytes from 112.80.248.75: seq=3 ttl=57 time=12.842 ms

64 bytes from 112.80.248.75: seq=4 ttl=57 time=11.435 ms

64 bytes from 112.80.248.75: seq=5 ttl=57 time=10.144 ms

64 bytes from 112.80.248.75: seq=6 ttl=57 time=10.455 ms

^C

--- www.baidu.com ping statistics ---

7 packets transmitted, 7 packets received, 0% packet loss

round-trip min/avg/max = 10.144/11.038/12.842 ms

# uname -a

Linux f1c100s 4.19.1-suda-morris #15 Sat Nov 17 22:48:04 CST 2018 armv5tejl GNU/Linux #105 Re: ESP32/ESP8266 » ESP32可以使用GPIO0输出时钟给RMII了!又帮老板省了一个晶振钱 » 2018-11-16 16:58:44

事实上,我懒得去单独买一个反相器,所以就ti上申请了个样片。我觉得市面上大部分的反相器都应该支持吧,不会比晶振贵的,哈哈哈哈

这个芯片售价如何?看了一下立创商城没有卖,淘宝卖得价格和有源晶振差不多.

msr06rr 说:我觉得过高低温问题不大,反相器用的TI的 http://www.ti.com/product/SN74AUP1T14/

dbskcnc 说:能过高低温度吗, 如果真能稳定,那倒是很不错

#106 Re: ESP32/ESP8266 » ESP32可以使用GPIO0输出时钟给RMII了!又帮老板省了一个晶振钱 » 2018-11-16 15:31:43

我觉得过高低温问题不大,反相器用的TI的 http://www.ti.com/product/SN74AUP1T14/

能过高低温度吗, 如果真能稳定,那倒是很不错

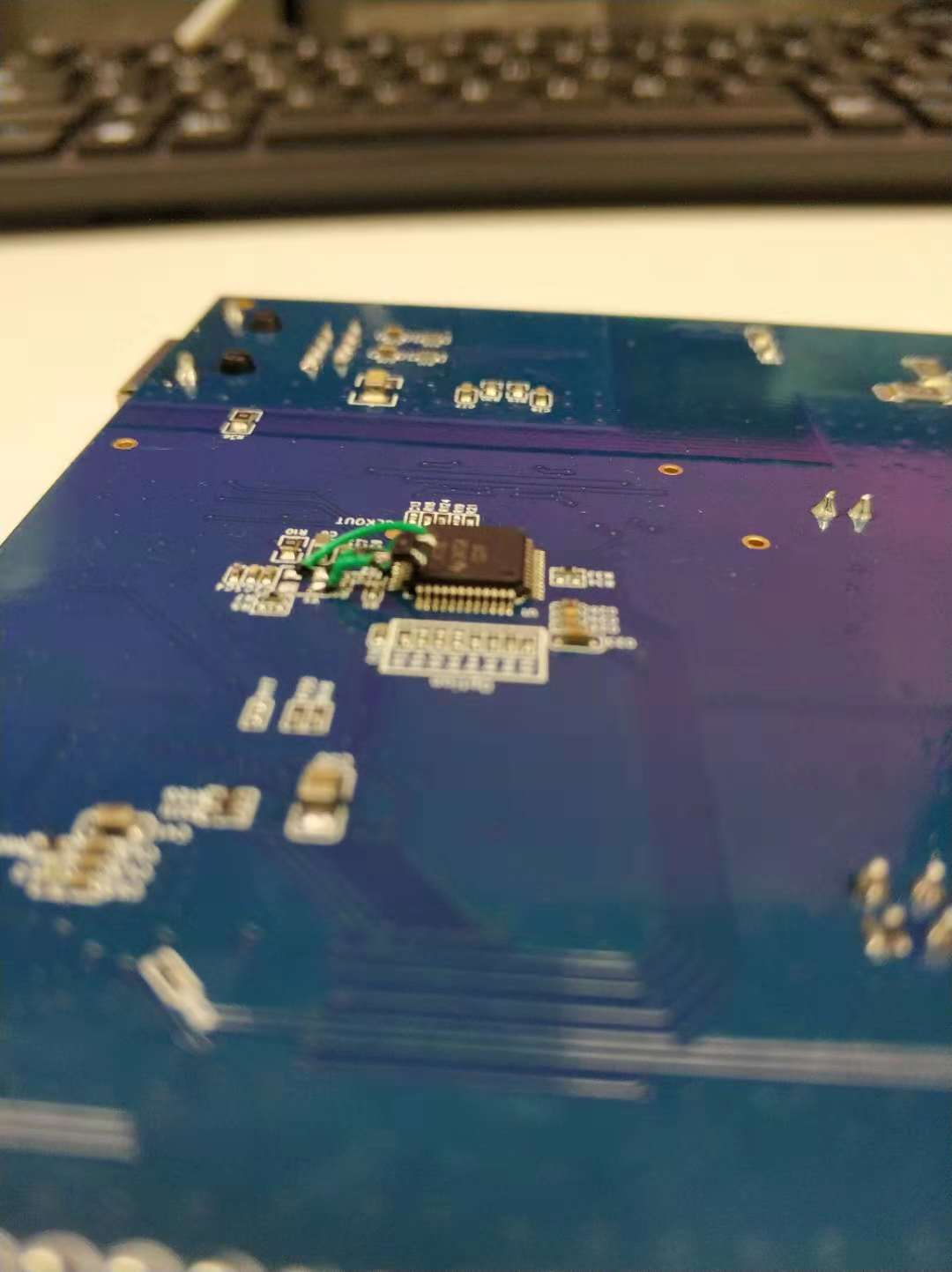

#109 ESP32/ESP8266 » ESP32可以使用GPIO0输出时钟给RMII了!又帮老板省了一个晶振钱 » 2018-11-16 15:03:02

- msr06rr

- 回复: 13

ESP32使用以太网其实挺尴尬的,以太网RMII需要的50MHz参考时钟要么外部晶振给,要么从GPIO16和17输出,但是偏偏PSRAM把这两个引脚占用了。。。在ESP32上玩以太网的都是搞大应用的,没有大内存怎么行。

好在有老外发现GPIO0也可以输出一路50MHz时钟,就是不太稳。

https://github.com/espressif/esp-idf/pull/1127#issuecomment-340727923

通过实验发现,GPIO0输出的50MHz时钟很有可能相位偏差太大,导致和内部时钟的采样沿对不上。所以我在GPIO0外面加了一个反相器,成了,正常工作,同时PSRAM也能用,完美!

#110 Re: ESP32/ESP8266 » ESP32通过I2S控制WM8960播放WAV音频,只能听到噪音, » 2018-11-15 10:44:38

可以去官方的中文论坛提交问题呀,他们有专门的audio团队维护这个板块的,在这里: https://esp32.com/viewforum.php?f=28&sid=0f8864f405a9c55c7af9e2634d9c4869

ESP32 I2S控制WM8960播放WAV音频,只能听到噪音,所以想咨询一下大侠们

1. wav的数据通过DMA写入到FIFO时,按照数据的原始格式直接输出吗?WAV是16bit 双声道数据,I2S 模式是标准I2S模式。

2. DMA写入FIFO的时候是已32bits的宽度一次写入的吧?需要在将数据挂到DMA之前,将每次的采样转成16bit大端格式吗?谢谢~~~

#111 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 找到了一款9.9的MCU » 2018-11-14 20:41:51

- msr06rr

- 回复: 4

https://item.taobao.com/item.htm?id=582170887555#detail

合宙出了一款卖9.9的MCU,支持LCD,摄像头,内核是RDA8955

#112 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 合宙推出66块钱的 4G 模组, 有没有大神用过? » 2018-11-14 20:00:28

是的,貌似初始化阶段还是需要发AT指令的,然后就不知怎么的进入了PPP模式了,就可以使用本地的协议栈(比如lwip就支持pppos)。所以我想买一个支持ppp,但是又不需要别的复杂功能(比如https,mqtt,coap啥的)的GSM模块,晕哥有啥推荐的吗?

msr06rr 说:@晕哥, 最近想搞PPPoS(PPP over Serial),不太懂和AT的关系,能否给我们萌新小白科普一下?是不是支持的AT的GSM模块都支持PPP?

没有了解 但是我觉得PPPoS的设置、拨号仍然需要AT指令吧。

PPPoS应该是与自带协议栈可以使用AT指令与服务器发生TCP/HTTP指令比较才对,比如SIM800C就内置HTTP指令

#113 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 合宙推出66块钱的 4G 模组, 有没有大神用过? » 2018-11-14 19:07:50

#114 Re: 全志 SOC » 在线配置F1C100S工具求测试 » 2018-11-13 20:38:49

#115 Re: 全志 SOC » 网友 @chong 大神提供的f1c100s mainline linux usb 补丁包,支持usb otg(host & device) » 2018-11-12 22:48:16

#116 Re: 全志 SOC » f1c100s使用linux4.19可以正常reboot,但是otg该怎么配置才正确啊? » 2018-11-11 01:19:18

该死的reboot

# reboot

# Stopping network: OK

Saving random seed... done.

Stopping logging: OK

umount: devtmpfs busy - remounted read-only

[ 317.181833] EXT4-fs (mmcblk0p2): re-mounted. Opts: (null)

The system is going down NOW!

Sent SIGTERM to all processes

Sent SIGKILL to all processes

Requesting system reboot

[ 319.197161] reboot: Restarting system

[ 320.196866] Reboot failed -- System halted#117 Re: 全志 SOC » f1c100s使用linux4.19可以正常reboot,但是otg该怎么配置才正确啊? » 2018-11-11 01:17:40

貌似reboot还是会失败。。。

这该怎么整?没经验,求指教?

BTW,U盘可以工作了

[ 222.924928] usb 1-1: new high-speed USB device number 4 using musb-hdrc

[ 223.114261] usb-storage 1-1:1.0: USB Mass Storage device detected

[ 223.121517] scsi host0: usb-storage 1-1:1.0

[ 224.167779] scsi 0:0:0:0: Direct-Access Generic Flash Disk 8.07 PQ: 0 ANSI: 4

[ 224.179307] sd 0:0:0:0: Attached scsi generic sg0 type 0

[ 224.186829] sd 0:0:0:0: [sda] 15974400 512-byte logical blocks: (8.18 GB/7.62 GiB)

[ 224.196136] sd 0:0:0:0: [sda] Write Protect is off

[ 224.202626] sd 0:0:0:0: [sda] Write cache: disabled, read cache: enabled, doesn't support DPO or FUA

[ 224.225297] sda: sda1

[ 224.233192] sd 0:0:0:0: [sda] Attached SCSI removable disk#118 Re: ESP32/ESP8266 » esp32新出了中文社区 » 2018-11-10 11:29:37

#119 ESP32/ESP8266 » esp32新出了中文社区 » 2018-11-10 11:21:05

- msr06rr

- 回复: 2

ESP32之前只有英文版社区,现在改版后又加入了中文社区

https://esp32.com/index.php

#122 Re: 全志 SOC » 网友 @chong 大神提供的f1c100s mainline linux usb 补丁包,支持usb otg(host & device) » 2018-11-02 12:52:00

#123 Re: RISC-V » SiFive提供core design和chip design了 » 2018-10-31 13:27:42

#124 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 买了几块 SIM800C 开发板与模块 » 2018-10-29 12:35:24

#125 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 买了几块 SIM800C 开发板与模块 » 2018-10-29 11:03:12

#126 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 买了几块 SIM800C 开发板与模块 » 2018-10-29 09:55:53

#128 全志 SOC » f1c100s使用linux4.19可以正常reboot,但是otg该怎么配置才正确啊? » 2018-10-28 18:32:57

- msr06rr

- 回复: 9

f1c100s 的otg该怎么配置啊?

这是我的log输出:

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 4.19.0 suda-morris (wendy@wendy-PC) (gcc version 8.2.0 (morris)) #7 Sun Oct 28 18:14:55 CST 2018

[ 0.000000] CPU: ARM926EJ-S [41069265] revision 5 (ARMv5TEJ), cr=0005317f

[ 0.000000] CPU: VIVT data cache, VIVT instruction cache

[ 0.000000] OF: fdt: Machine model: Lichee Pi Nano

[ 0.000000] Memory policy: Data cache writeback

[ 0.000000] cma: Reserved 16 MiB at 0x81000000

[ 0.000000] random: get_random_bytes called from start_kernel+0x84/0x398 with crng_init=0

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 8128

[ 0.000000] Kernel command line: console=tty0 console=ttyS0,115200 panic=5 rootwait root=/dev/mtdblock3 rw rootfstype=jffs2

[ 0.000000] Dentry cache hash table entries: 4096 (order: 2, 16384 bytes)

[ 0.000000] Inode-cache hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.000000] Memory: 7352K/32768K available (5120K kernel code, 200K rwdata, 1248K rodata, 1024K init, 215K bss, 9032K reserved, 16384K cma-reserved, 0K highmem)

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] vector : 0xffff0000 - 0xffff1000 ( 4 kB)

[ 0.000000] fixmap : 0xffc00000 - 0xfff00000 (3072 kB)

[ 0.000000] vmalloc : 0xc2800000 - 0xff800000 ( 976 MB)

[ 0.000000] lowmem : 0xc0000000 - 0xc2000000 ( 32 MB)

[ 0.000000] pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)

[ 0.000000] modules : 0xbf000000 - 0xbfe00000 ( 14 MB)

[ 0.000000] .text : 0x(ptrval) - 0x(ptrval) (6112 kB)

[ 0.000000] .init : 0x(ptrval) - 0x(ptrval) (1024 kB)

[ 0.000000] .data : 0x(ptrval) - 0x(ptrval) ( 201 kB)

[ 0.000000] .bss : 0x(ptrval) - 0x(ptrval) ( 216 kB)

[ 0.000000] SLUB: HWalign=32, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

[ 0.000050] sched_clock: 32 bits at 24MHz, resolution 41ns, wraps every 89478484971ns

[ 0.000137] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns

[ 0.000666] Console: colour dummy device 80x30

[ 0.001684] console [tty0] enabled

[ 0.001811] Calibrating delay loop... 203.16 BogoMIPS (lpj=1015808)

[ 0.070312] pid_max: default: 32768 minimum: 301

[ 0.070849] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.070957] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.072750] CPU: Testing write buffer coherency: ok

[ 0.074948] Setting up static identity map for 0x80100000 - 0x80100058

[ 0.077697] devtmpfs: initialized

[ 0.084447] VFP support v0.3: not present

[ 0.085040] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.085193] futex hash table entries: 256 (order: -1, 3072 bytes)

[ 0.089662] pinctrl core: initialized pinctrl subsystem

[ 0.092071] NET: Registered protocol family 16

[ 0.095550] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.119424] usbcore: registered new interface driver usbfs

[ 0.119694] usbcore: registered new interface driver hub

[ 0.119982] usbcore: registered new device driver usb

[ 0.120641] pps_core: LinuxPPS API ver. 1 registered

[ 0.120735] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.121508] Advanced Linux Sound Architecture Driver Initialized.

[ 0.123630] clocksource: Switched to clocksource timer

[ 0.154835] NET: Registered protocol family 2

[ 0.156495] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 4096 bytes)

[ 0.156681] TCP established hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.156787] TCP bind hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.156875] TCP: Hash tables configured (established 1024 bind 1024)

[ 0.157210] UDP hash table entries: 256 (order: 0, 4096 bytes)

[ 0.157327] UDP-Lite hash table entries: 256 (order: 0, 4096 bytes)

[ 0.157952] NET: Registered protocol family 1

[ 0.161372] workingset: timestamp_bits=30 max_order=13 bucket_order=0

[ 0.181229] jffs2: version 2.2. (NAND) © 2001-2006 Red Hat, Inc.

[ 0.187030] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 249)

[ 0.187170] io scheduler noop registered

[ 0.187225] io scheduler deadline registered

[ 0.187849] io scheduler cfq registered (default)

[ 0.187948] io scheduler mq-deadline registered

[ 0.188003] io scheduler kyber registered

[ 0.188900] sun4i-usb-phy 1c13400.phy: Couldn't request ID GPIO

[ 0.200619] suniv-pinctrl 1c20800.pinctrl: initialized sunXi PIO driver

[ 0.389261] Serial: 8250/16550 driver, 8 ports, IRQ sharing disabled

[ 0.396777] console [ttyS0] disabled

[ 0.417118] 1c25000.serial: ttyS0 at MMIO 0x1c25000 (irq = 23, base_baud = 6250000) is a 16550A

[ 0.847290] console [ttyS0] enabled

[ 0.873450] 1c25400.serial: ttyS1 at MMIO 0x1c25400 (irq = 24, base_baud = 6250000) is a 16550A

[ 0.891992] m25p80 spi0.0: w25q128 (16384 Kbytes)

[ 0.897985] 4 fixed-partitions partitions found on MTD device spi0.0

[ 0.904541] Creating 4 MTD partitions on "spi0.0":

[ 0.909403] 0x000000000000-0x000000100000 : "u-boot"

[ 0.917413] 0x000000100000-0x000000110000 : "dtb"

[ 0.925036] 0x000000110000-0x000000510000 : "kernel"

[ 0.932813] 0x000000510000-0x000001000000 : "rootfs"

[ 0.941097] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 0.947845] ehci-platform: EHCI generic platform driver

[ 0.953454] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

[ 0.959890] ohci-platform: OHCI generic platform driver

[ 0.966004] musb-sunxi 1c13000.usb: Invalid or missing 'dr_mode' property

[ 0.972919] musb-sunxi: probe of 1c13000.usb failed with error -22

[ 0.980201] i2c /dev entries driver

[ 0.986300] sunxi-wdt 1c20ca0.watchdog: Watchdog enabled (timeout=16 sec, nowayout=0)

[ 0.996461] sunxi-mmc 1c0f000.mmc: Linked as a consumer to regulator.1

[ 1.030407] sunxi-mmc 1c0f000.mmc: initialized, max. request size: 16384 KB

[ 1.039981] usbcore: registered new interface driver usbhid

[ 1.045769] usbhid: USB HID core driver

[ 1.053554] NET: Registered protocol family 17

[ 1.058329] Key type dns_resolver registered

[ 1.075720] hctosys: unable to open rtc device (rtc0)

[ 1.081606] ALSA device list:

[ 1.084772] No soundcards found.

[ 1.091808] random: fast init done

[ 1.193590] random: crng init done

[ 1.920846] VFS: Mounted root (jffs2 filesystem) on device 31:3.

[ 1.930040] devtmpfs: mounted

[ 1.937759] Freeing unused kernel memory: 1024K

[ 1.942460] Run /sbin/init as init process

Starting logging: OK

Initializing random number generator... done.

Starting network: OK

Welcome to Buildroot其中的

[ 0.966004] musb-sunxi 1c13000.usb: Invalid or missing 'dr_mode' property

[ 0.972919] musb-sunxi: probe of 1c13000.usb failed with error -22

是什么原因造成的?要怎么填坑?

#129 Re: 全志 SOC » 网友 @chong 大神提供的f1c100s mainline linux usb 补丁包,支持usb otg(host & device) » 2018-10-23 15:37:29

git clone https://github.com/torvalds/linux.git

cd linux

git reset --hard 5e335542de83558e46d28de1008a1c37d5d6679a ###恢复到指定版本

patch -p1 < lichee_pi_nano_usbok_patch_5e335542de83558e46d.patch ###打补丁ARCH=arm CROSS_COMPILE=arm-linux-gnueabi- make sunxi_defconfig ###使用默认配置

ARCH=arm CROSS_COMPILE=arm-linux-gnueabi- make -j4 ###四进程编译

晕哥,这版4.19的内核,除了@chong 大神适配的USB驱动外,还有哪些驱动是可以用的哈?是不是要比荔枝派nano的全?

#130 Re: 全志 SOC » 网友 @chong 大神提供的f1c100s mainline linux usb 补丁包,支持usb otg(host & device) » 2018-10-22 12:27:59

#132 全志 SOC » reboot不起作用 » 2018-10-06 01:27:12

- msr06rr

- 回复: 2

登录到licheepi的终端,输入reboot后系统是停止了,但是并没有重新启动,需要怎么操作?

# reboot

# Stopping network: OK

Saving random seed... done.

Stopping logging: OK

umount: devtmpfs busy - remounted read-only

The system is going down NOW!

Sent SIGTERM to all processes

Sent SIGKILL to[ 61.846497] reboot: Restarting system

[ 62.846139] Reboot failed -- System halted#133 Re: 全志 SOC » linux内核启动过程中没有看到分区标信息 » 2018-10-06 01:10:35

#134 Re: 全志 SOC » linux内核启动过程中没有看到分区标信息 » 2018-10-05 15:08:21

Symbol: MTD_M25P80 [=y] │

│ Type : tristate │

│ Prompt: Support most SPI Flash chips (AT26DF, M25P, W25X, ...) │

│ Location: │

│ -> Device Drivers │

│ -> Memory Technology Device (MTD) support (MTD [=y]) │

│ (1) -> Self-contained MTD device drivers │

│ Defined at drivers/mtd/devices/Kconfig:81 │

│ Depends on: MTD [=y] && HAS_IOMEM [=y] && SPI_MASTER [=y] && MTD_SPI_NOR [=y] 勾了的,真奇怪

#135 Re: 全志 SOC » linux内核启动过程中没有看到分区标信息 » 2018-10-05 15:01:01

dts/dtsi 两个文件都贴上来看下

这是dtsi文件

// SPDX-License-Identifier: (GPL-2.0+ OR X11)

/*

* Copyright 2018 Icenowy Zheng <icenowy@aosc.io>

*/

#include <dt-bindings/clock/suniv-ccu.h>

#include <dt-bindings/reset/suniv-ccu.h>

/ {

#address-cells = <1>;

#size-cells = <1>;

interrupt-parent = <&intc>;

clocks {

#address-cells = <1>;

#size-cells = <1>;

ranges;

osc24M: clk-24M {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <24000000>;

clock-output-names = "osc24M";

};

osc32k: clk-32k {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <32768>;

clock-output-names = "osc32k";

};

};

cpus {

#address-cells = <0>;

#size-cells = <0>;

cpu {

compatible = "arm,arm926ej-s";

device_type = "cpu";

};

};

de: display-engine {

compatible = "allwinner,suniv-f1c100s-display-engine";

allwinner,pipelines = <&fe0>;

status = "disabled";

};

soc {

compatible = "simple-bus";

#address-cells = <1>;

#size-cells = <1>;

ranges;

sram-controller@1c00000 {

compatible = "allwinner,sun4i-a10-sram-controller";

reg = <0x01c00000 0x30>;

#address-cells = <1>;

#size-cells = <1>;

ranges;

sram_d: sram@10000 {

compatible = "mmio-sram";

reg = <0x00010000 0x1000>;

#address-cells = <1>;

#size-cells = <1>;

ranges = <0 0x00010000 0x1000>;

otg_sram: sram-section@0 {

compatible = "allwinner,sun4i-a10-sram-d";

reg = <0x0000 0x1000>;

status = "disabled";

};

};

};

spi0: spi@1c05000 {

compatible = "allwinner,suniv-f1c100s-spi",

"allwinner,sun8i-h3-spi";

reg = <0x01c05000 0x1000>;

interrupts = <10>;

clocks = <&ccu CLK_BUS_SPI0>, <&ccu CLK_BUS_SPI0>;

clock-names = "ahb", "mod";

resets = <&ccu RST_BUS_SPI0>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

spi1: spi@1c06000 {

compatible = "allwinner,suniv-f1c100s-spi",

"allwinner,sun8i-h3-spi";

reg = <0x01c06000 0x1000>;

interrupts = <11>;

clocks = <&ccu CLK_BUS_SPI1>, <&ccu CLK_BUS_SPI1>;

clock-names = "ahb", "mod";

resets = <&ccu RST_BUS_SPI1>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

tcon0: lcd-controller@1c0c000 {

compatible = "allwinner,suniv-f1c100s-tcon";

reg = <0x01c0c000 0x1000>;

interrupts = <29>;

clocks = <&ccu CLK_BUS_LCD>,

<&ccu CLK_TCON>;

clock-names = "ahb",

"tcon-ch0";

clock-output-names = "tcon-pixel-clock";

resets = <&ccu RST_BUS_LCD>;

reset-names = "lcd";

status = "disabled";

ports {

#address-cells = <1>;

#size-cells = <0>;

tcon0_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

tcon0_in_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_out_tcon0>;

};

};

tcon0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

};

};

mmc0: mmc@1c0f000 {

compatible = "allwinner,suniv-f1c100s-mmc",

"allwinner,sun7i-a20-mmc";

reg = <0x01c0f000 0x1000>;

clocks = <&ccu CLK_BUS_MMC0>,

<&ccu CLK_MMC0>,

<&ccu CLK_MMC0_OUTPUT>,

<&ccu CLK_MMC0_SAMPLE>;

clock-names = "ahb",

"mmc",

"output",

"sample";

resets = <&ccu RST_BUS_MMC0>;

reset-names = "ahb";

interrupts = <23>;

pinctrl-names = "default";

pinctrl-0 = <&mmc0_pins>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

mmc1: mmc@1c10000 {

compatible = "allwinner,suniv-f1c100s-mmc",

"allwinner,sun7i-a20-mmc";

reg = <0x01c10000 0x1000>;

clocks = <&ccu CLK_BUS_MMC1>,

<&ccu CLK_MMC1>,

<&ccu CLK_MMC1_OUTPUT>,

<&ccu CLK_MMC1_SAMPLE>;

clock-names = "ahb",

"mmc",

"output",

"sample";

resets = <&ccu RST_BUS_MMC1>;

reset-names = "ahb";

interrupts = <24>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

ccu: clock@1c20000 {

compatible = "allwinner,suniv-f1c100s-ccu";

reg = <0x01c20000 0x400>;

clocks = <&osc24M>, <&osc32k>;

clock-names = "hosc", "losc";

#clock-cells = <1>;

#reset-cells = <1>;

};

intc: interrupt-controller@1c20400 {

compatible = "allwinner,suniv-f1c100s-ic";

reg = <0x01c20400 0x400>;

interrupt-controller;

#interrupt-cells = <1>;

};

pio: pinctrl@1c20800 {

compatible = "allwinner,suniv-f1c100s-pinctrl";

reg = <0x01c20800 0x400>;

interrupts = <38>, <39>, <40>;

clocks = <&ccu CLK_BUS_PIO>, <&osc24M>, <&osc32k>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

interrupt-controller;

#interrupt-cells = <3>;

#gpio-cells = <3>;

spi0_pins_a: spi0-pins-pc {

pins = "PC0", "PC1", "PC2", "PC3";

function = "spi0";

};

lcd_rgb666_pins: lcd-rgb666-pins {

pins = "PD0", "PD1", "PD2", "PD3", "PD4",

"PD5", "PD6", "PD7", "PD8", "PD9",

"PD10", "PD11", "PD12", "PD13", "PD14",

"PD15", "PD16", "PD17", "PD18", "PD19",

"PD20", "PD21";

function = "lcd";

};

uart0_pins_a: uart-pins-pe {

pins = "PE0", "PE1";

function = "uart0";

};

mmc0_pins: mmc0-pins {

pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

function = "mmc0";

};

};

timer@1c20c00 {

compatible = "allwinner,suniv-f1c100s-timer";

reg = <0x01c20c00 0x90>;

interrupts = <13>;

clocks = <&osc24M>;

};

wdt: watchdog@1c20ca0 {

compatible = "allwinner,sun6i-a31-wdt";

reg = <0x01c20ca0 0x20>;

};

uart0: serial@1c25000 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25000 0x400>;

interrupts = <1>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART0>;

resets = <&ccu RST_BUS_UART0>;

status = "disabled";

};

uart1: serial@1c25400 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25400 0x400>;

interrupts = <2>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART1>;

resets = <&ccu RST_BUS_UART1>;

status = "disabled";

};

uart2: serial@1c25800 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25800 0x400>;

interrupts = <3>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART2>;

resets = <&ccu RST_BUS_UART2>;

status = "disabled";

};

usb_otg: usb@1c13000 {

compatible = "allwinner,suniv-f1c100s-musb";

reg = <0x01c13000 0x0400>;

clocks = <&ccu CLK_BUS_OTG>;

resets = <&ccu RST_BUS_OTG>;

interrupts = <26>;

interrupt-names = "mc";

phys = <&usbphy 0>;

phy-names = "usb";

extcon = <&usbphy 0>;

allwinner,sram = <&otg_sram 1>;

status = "disabled";

};

usbphy: phy@1c13400 {

compatible = "allwinner,suniv-f1c100s-usb-phy";

reg = <0x01c13400 0x10>;

reg-names = "phy_ctrl";

clocks = <&ccu CLK_USB_PHY0>;

clock-names = "usb0_phy";

resets = <&ccu RST_USB_PHY0>;

reset-names = "usb0_reset";

#phy-cells = <1>;

status = "disabled";

};

fe0: display-frontend@1e00000 {

compatible = "allwinner,suniv-f1c100s-display-frontend";

reg = <0x01e00000 0x20000>;

interrupts = <30>;

clocks = <&ccu CLK_BUS_DE_FE>, <&ccu CLK_DE_FE>,

<&ccu CLK_DRAM_DE_FE>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_BUS_DE_FE>;

status = "disabled";

ports {

#address-cells = <1>;

#size-cells = <0>;

fe0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

fe0_out_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_in_fe0>;

};

};

};

};

be0: display-backend@1e60000 {

compatible = "allwinner,suniv-f1c100s-display-backend";

reg = <0x01e60000 0x10000>;

reg-names = "be";

interrupts = <31>;

clocks = <&ccu CLK_BUS_DE_BE>, <&ccu CLK_DE_BE>,

<&ccu CLK_DRAM_DE_BE>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_BUS_DE_BE>;

reset-names = "be";

assigned-clocks = <&ccu CLK_DE_BE>;

assigned-clock-rates = <300000000>;

ports {

#address-cells = <1>;

#size-cells = <0>;

be0_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

be0_in_fe0: endpoint@0 {

reg = <0>;

remote-endpoint = <&fe0_out_be0>;

};

};

be0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

be0_out_tcon0: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_in_be0>;

};

};

};

};

};

};这是dts文件

// SPDX-License-Identifier: (GPL-2.0+ OR X11)

/*

* Copyright 2018 Icenowy Zheng <icenowy@aosc.io>

*/

/dts-v1/;

#include "suniv-f1c100s.dtsi"

#include <dt-bindings/gpio/gpio.h>

/ {

model = "Lichee Pi Nano";

compatible = "licheepi,licheepi-nano", "allwinner,suniv-f1c100s",

"allwinner,suniv";

aliases {

serial0 = &uart0;

spi0 = &spi0;

};

chosen {

stdout-path = "serial0:115200n8";

};

reg_vcc3v3: vcc3v3 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

};

};

&mmc0 {

vmmc-supply = <®_vcc3v3>;

bus-width = <4>;

broken-cd;

status = "okay";

};

&otg_sram {

status = "okay";

};

&spi0 {

pinctrl-names = "default";

pinctrl-0 = <&spi0_pins_a>;

status = "okay";

spi-max-frequency = <50000000>;

flash: w25q128@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "winbond,w25q128", "jedec,spi-nor";

reg = <0>;

spi-max-frequency = <50000000>;

partitions {

compatible = "fixed-partitions";

#address-cells = <1>;

#size-cells = <1>;

partition@0 {

label = "u-boot";

reg = <0x000000 0x100000>;

read-only;

};

partition@100000 {

label = "dtb";

reg = <0x100000 0x10000>;

read-only;

};

partition@110000 {

label = "kernel";

reg = <0x110000 0x400000>;

read-only;

};

partition@510000 {

label = "rootfs";

reg = <0x510000 0xAF0000>;

};

};

};

};

&uart0 {

pinctrl-names = "default";

pinctrl-0 = <&uart0_pins_a>;

status = "okay";

};

&usb_otg {

dr_mode = "otg";

status = "okay";

};

&usbphy {

usb0_id_det-gpio = <&pio 4 2 GPIO_ACTIVE_HIGH>; /* PE2 */

status = "okay";

};#136 全志 SOC » linux内核启动过程中没有看到分区标信息 » 2018-10-05 14:51:24

- msr06rr

- 回复: 14

U-Boot 2018.01suda-05679-g013ca457fd-dirty (Oct 04 2018 - 14:10:48 +0800)

CPU: Allwinner F Series (SUNIV)

Model: Lichee Pi Nano

DRAM: 32 MiB

MMC: SUNXI SD/MMC: 0

SF: Detected w25q128bv with page size 256 Bytes, erase size 4 KiB, total 16 MiB

*** Warning - bad CRC, using default environment

Setting up a 480x272 lcd console (overscan 0x0)

In: serial@1c25000

Out: serial@1c25000

Err: serial@1c25000

Net: No ethernet found.

starting USB...

No controllers found

Hit any key to stop autoboot: 0

SF: Detected w25q128bv with page size 256 Bytes, erase size 4 KiB, total 16 MiB

device 0 offset 0x100000, size 0x10000

SF: 65536 bytes @ 0x100000 Read: OK

device 0 offset 0x110000, size 0x400000

SF: 4194304 bytes @ 0x110000 Read: OK

## Flattened Device Tree blob at 80c00000

Booting using the fdt blob at 0x80c00000

Loading Device Tree to 80e41000, end 80e4605b ... OK

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 4.14.0-suda-morris+ (wendy@wendy-PC) (gcc version 8.2.0 (morris)) #5 Fri Oct 5 14:25:26 CST 2018

[ 0.000000] CPU: ARM926EJ-S [41069265] revision 5 (ARMv5TEJ), cr=0005317f

[ 0.000000] CPU: VIVT data cache, VIVT instruction cache

[ 0.000000] OF: fdt: Machine model: Lichee Pi Nano

[ 0.000000] Memory policy: Data cache writeback

[ 0.000000] random: fast init done

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 8128

[ 0.000000] Kernel command line: console=ttyS0,115200 console=tty0 panic=5 rootwait root=/dev/mtdblock3 rw rootfstype=jffs2

[ 0.000000] PID hash table entries: 128 (order: -3, 512 bytes)

[ 0.000000] Dentry cache hash table entries: 4096 (order: 2, 16384 bytes)

[ 0.000000] Inode-cache hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.000000] Memory: 22668K/32768K available (6144K kernel code, 212K rwdata, 1392K rodata, 1024K init, 250K bss, 10100K reserved, 0K cma-reserved, 0K highmem)

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] vector : 0xffff0000 - 0xffff1000 ( 4 kB)

[ 0.000000] fixmap : 0xffc00000 - 0xfff00000 (3072 kB)

[ 0.000000] vmalloc : 0xc2800000 - 0xff800000 ( 976 MB)

[ 0.000000] lowmem : 0xc0000000 - 0xc2000000 ( 32 MB)

[ 0.000000] pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)

[ 0.000000] modules : 0xbf000000 - 0xbfe00000 ( 14 MB)

[ 0.000000] .text : 0xc0008000 - 0xc0700000 (7136 kB)

[ 0.000000] .init : 0xc0900000 - 0xc0a00000 (1024 kB)

[ 0.000000] .data : 0xc0a00000 - 0xc0a35080 ( 213 kB)

[ 0.000000] .bss : 0xc0a3a444 - 0xc0a78e14 ( 251 kB)

[ 0.000000] SLUB: HWalign=32, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

[ 0.000045] sched_clock: 32 bits at 24MHz, resolution 41ns, wraps every 89478484971ns

[ 0.000110] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns

[ 0.000647] Console: colour dummy device 80x30

[ 0.001616] console [tty0] enabled

[ 0.001719] Calibrating delay loop... 203.16 BogoMIPS (lpj=1015808)

[ 0.070283] pid_max: default: 32768 minimum: 301

[ 0.070660] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.070760] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.072247] CPU: Testing write buffer coherency: ok

[ 0.073966] Setting up static identity map for 0x80100000 - 0x80100058

[ 0.076512] devtmpfs: initialized

[ 0.083520] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.083688] futex hash table entries: 256 (order: -1, 3072 bytes)

[ 0.084002] pinctrl core: initialized pinctrl subsystem

[ 0.086086] NET: Registered protocol family 16

[ 0.087707] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.089590] cpuidle: using governor menu

[ 0.115011] SCSI subsystem initialized

[ 0.115421] usbcore: registered new interface driver usbfs

[ 0.115640] usbcore: registered new interface driver hub

[ 0.115906] usbcore: registered new device driver usb

[ 0.116405] pps_core: LinuxPPS API ver. 1 registered

[ 0.116494] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.116641] PTP clock support registered

[ 0.117182] Advanced Linux Sound Architecture Driver Initialized.

[ 0.120400] clocksource: Switched to clocksource timer

[ 0.146603] NET: Registered protocol family 2

[ 0.148148] TCP established hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.148303] TCP bind hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.148397] TCP: Hash tables configured (established 1024 bind 1024)

[ 0.148722] UDP hash table entries: 256 (order: 0, 4096 bytes)

[ 0.148830] UDP-Lite hash table entries: 256 (order: 0, 4096 bytes)

[ 0.149347] NET: Registered protocol family 1

[ 0.150530] RPC: Registered named UNIX socket transport module.

[ 0.150647] RPC: Registered udp transport module.

[ 0.150699] RPC: Registered tcp transport module.

[ 0.150744] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.151959] NetWinder Floating Point Emulator V0.97 (double precision)

[ 0.153781] Initialise system trusted keyrings

[ 0.154429] workingset: timestamp_bits=30 max_order=13 bucket_order=0

[ 0.171477] NFS: Registering the id_resolver key type

[ 0.171656] Key type id_resolver registered

[ 0.171719] Key type id_legacy registered

[ 0.171884] jffs2: version 2.2. (NAND) © 2001-2006 Red Hat, Inc.

[ 0.185688] Key type asymmetric registered

[ 0.185801] Asymmetric key parser 'x509' registered

[ 0.186055] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 251)

[ 0.186158] io scheduler noop registered

[ 0.186207] io scheduler deadline registered

[ 0.187017] io scheduler cfq registered (default)

[ 0.187117] io scheduler mq-deadline registered

[ 0.187174] io scheduler kyber registered

[ 0.188366] sun4i-usb-phy 1c13400.phy: Couldn't request ID GPIO

[ 0.198104] suniv-pinctrl 1c20800.pinctrl: initialized sunXi PIO driver

[ 0.366899] Serial: 8250/16550 driver, 8 ports, IRQ sharing disabled

[ 0.373874] console [ttyS0] disabled

[ 0.394212] 1c25000.serial: ttyS0 at MMIO 0x1c25000 (irq = 23, base_baud = 6250000) is a 16550A

[ 0.875798] console [ttyS0] enabled

[ 0.886320] panel-simple panel: panel supply power not found, using dummy regulator

[ 0.895641] SCSI Media Changer driver v0.25

[ 0.901430] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 0.908043] ehci-platform: EHCI generic platform driver

[ 0.913695] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

[ 0.919979] ohci-platform: OHCI generic platform driver

[ 0.925737] usbcore: registered new interface driver usb-storage

[ 0.932826] udc-core: couldn't find an available UDC - added [g_cdc] to list of pending drivers

[ 0.942013] i2c /dev entries driver

[ 1.000538] sunxi-mmc 1c0f000.mmc: base:0xc28a4000 irq:19

[ 1.008061] usbcore: registered new interface driver usbhid

[ 1.013834] usbhid: USB HID core driver

[ 1.035740] NET: Registered protocol family 17

[ 1.040675] Key type dns_resolver registered

[ 1.047301] Loading compiled-in X.509 certificates

[ 1.061799] [drm] Supports vblank timestamp caching Rev 2 (21.10.2013).

[ 1.068503] [drm] No driver support for vblank timestamp query.

[ 1.075502] sun4i-drm display-engine: bound 1e60000.display-backend (ops 0xc0739508)

[ 1.084470] sun4i-drm display-engine: bound 1c0c000.lcd-controller (ops 0xc07388bc)

[ 1.224972] Console: switching to colour frame buffer device 100x30

[ 1.272773] sun4i-drm display-engine: fb0: frame buffer device

[ 1.289137] [drm] Initialized sun4i-drm 1.0.0 20150629 for display-engine on minor 0

[ 1.307923] usb_phy_generic usb_phy_generic.0.auto: usb_phy_generic.0.auto supply vcc not found, using dummy regulator

[ 1.338673] ------------[ cut here ]------------

[ 1.353156] WARNING: CPU: 0 PID: 3 at drivers/usb/musb/sunxi.c:411 sunxi_musb_ep_offset+0x3c/0x54

[ 1.372120] sunxi_musb_ep_offset called with non 0 offset

[ 1.387636] Modules linked in:

[ 1.400642] CPU: 0 PID: 3 Comm: kworker/0:0 Not tainted 4.14.0-suda-morris+ #5

[ 1.418208] Hardware name: Allwinner suniv Family

[ 1.433215] Workqueue: events deferred_probe_work_func

[ 1.448873] [<c010e7f0>] (unwind_backtrace) from [<c010b6d8>] (show_stack+0x10/0x14)

[ 1.467562] [<c010b6d8>] (show_stack) from [<c01168f0>] (__warn+0xcc/0xfc)

[ 1.485453] [<c01168f0>] (__warn) from [<c0116574>] (warn_slowpath_fmt+0x38/0x48)

[ 1.504006] [<c0116574>] (warn_slowpath_fmt) from [<c0479a34>] (sunxi_musb_ep_offset+0x3c/0x54)

[ 1.524096] [<c0479a34>] (sunxi_musb_ep_offset) from [<c046d43c>] (ep_config_from_hw+0x74/0x140)

[ 1.544324] [<c046d43c>] (ep_config_from_hw) from [<c046f040>] (musb_probe+0x8fc/0xbec)

[ 1.563579] [<c046f040>] (musb_probe) from [<c03f6fe8>] (platform_drv_probe+0x50/0xac)

[ 1.582762] [<c03f6fe8>] (platform_drv_probe) from [<c03f5774>] (driver_probe_device+0x218/0x2ec)

[ 1.603061] [<c03f5774>] (driver_probe_device) from [<c03f3dd8>] (bus_for_each_drv+0x70/0xa0)

[ 1.623037] [<c03f3dd8>] (bus_for_each_drv) from [<c03f5478>] (__device_attach+0xac/0x114)

[ 1.642819] [<c03f5478>] (__device_attach) from [<c03f4a84>] (bus_probe_device+0x84/0x8c)

[ 1.662449] [<c03f4a84>] (bus_probe_device) from [<c03f2f10>] (device_add+0x388/0x594)

[ 1.681757] [<c03f2f10>] (device_add) from [<c03f6e0c>] (platform_device_add+0x100/0x20c)

[ 1.701119] [<c03f6e0c>] (platform_device_add) from [<c03f7738>] (platform_device_register_full+0xc0/0x108)

[ 1.732855] [<c03f7738>] (platform_device_register_full) from [<c0479778>] (sunxi_musb_probe+0x340/0x41c)

[ 1.764796] [<c0479778>] (sunxi_musb_probe) from [<c03f6fe8>] (platform_drv_probe+0x50/0xac)

[ 1.785261] [<c03f6fe8>] (platform_drv_probe) from [<c03f5774>] (driver_probe_device+0x218/0x2ec)

[ 1.806269] [<c03f5774>] (driver_probe_device) from [<c03f3dd8>] (bus_for_each_drv+0x70/0xa0)

[ 1.827127] [<c03f3dd8>] (bus_for_each_drv) from [<c03f5478>] (__device_attach+0xac/0x114)

[ 1.847541] [<c03f5478>] (__device_attach) from [<c03f4a84>] (bus_probe_device+0x84/0x8c)

[ 1.867935] [<c03f4a84>] (bus_probe_device) from [<c03f51b8>] (deferred_probe_work_func+0x8c/0x140)

[ 1.900826] [<c03f51b8>] (deferred_probe_work_func) from [<c01299d4>] (process_one_work+0x1d8/0x3e8)

[ 1.934330] [<c01299d4>] (process_one_work) from [<c0129e80>] (worker_thread+0x29c/0x5b8)

[ 1.955335] [<c0129e80>] (worker_thread) from [<c012ef38>] (kthread+0x120/0x138)

[ 1.975432] [<c012ef38>] (kthread) from [<c0108028>] (ret_from_fork+0x14/0x2c)

[ 1.995139] ---[ end trace 7c194ff9660c6f5c ]---

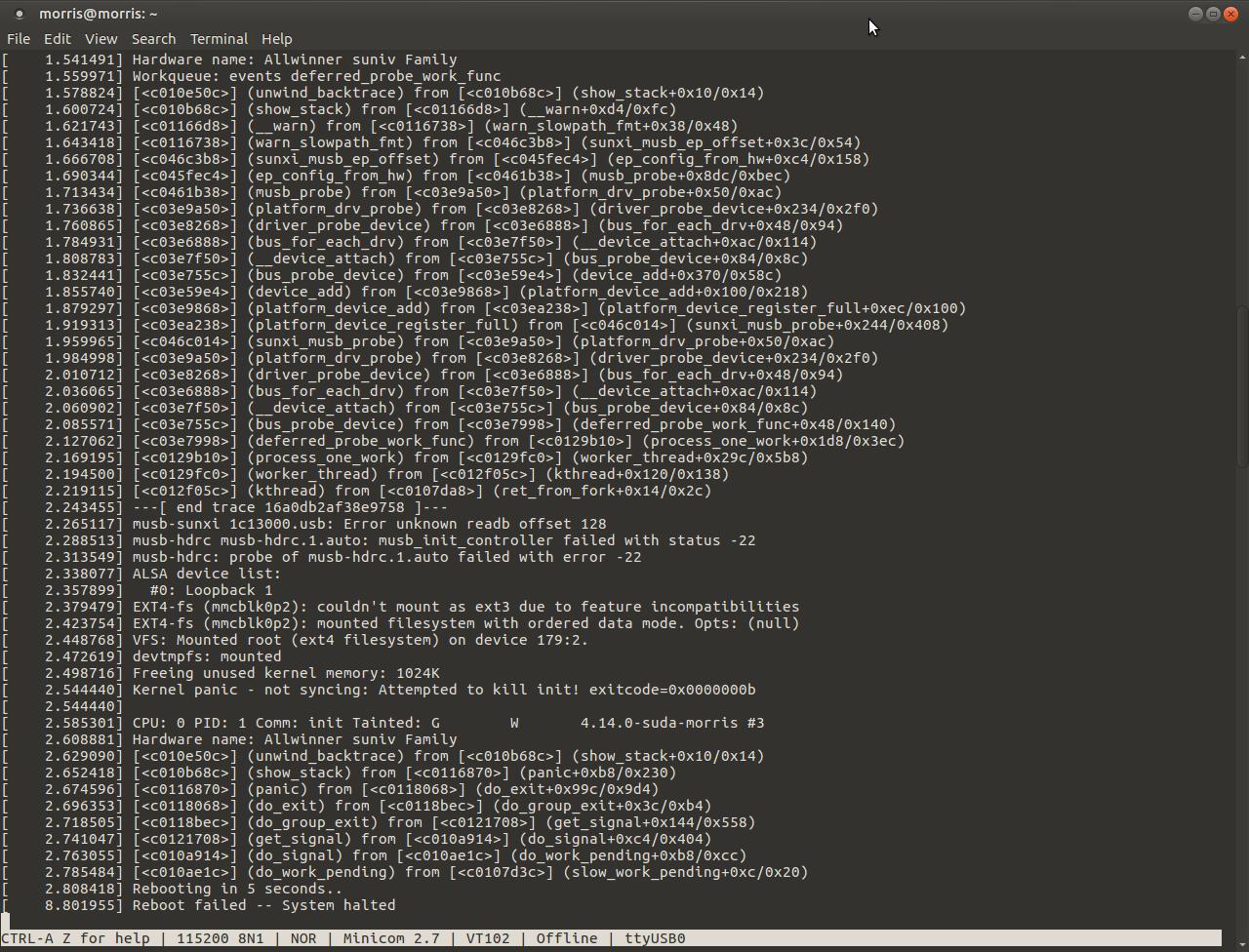

[ 2.012021] musb-sunxi 1c13000.usb: Error unknown readb offset 128

[ 2.030654] musb-hdrc musb-hdrc.1.auto: musb_init_controller failed with status -22

[ 2.050934] musb-hdrc: probe of musb-hdrc.1.auto failed with error -22

[ 2.070994] vcc3v3: disabling

[ 2.085977] ALSA device list:

[ 2.100339] #0: Loopback 1

[ 2.114778] Waiting for root device /dev/mtdblock3...我参考的是http://nano.lichee.pro/build_sys/build_flash.html教程,使用dts来传递分区信息

之前好像看到过有人也遇到过这个问题,不知道是如何解决的?

#142 Re: RISC-V » 围观国产【嘉楠耘智】出品 双RISC-V核 AI 处理器 K210 » 2018-09-16 15:46:47

#144 Re: RISC-V » 围观国产【嘉楠耘智】出品 双RISC-V核 AI 处理器 K210 » 2018-09-15 23:30:54

#147 Re: 全志 SOC » 荔枝派nano f1c100s 开发板入坑记录 » 2018-09-10 17:41:39

#149 Re: RISC-V » 荔枝派 $9 RISC-V开发板 (开放购买) » 2018-08-08 11:45:31

#150 Re: ESP32/ESP8266 » 移植LittlevGL到ESP32 » 2018-07-10 13:12:38

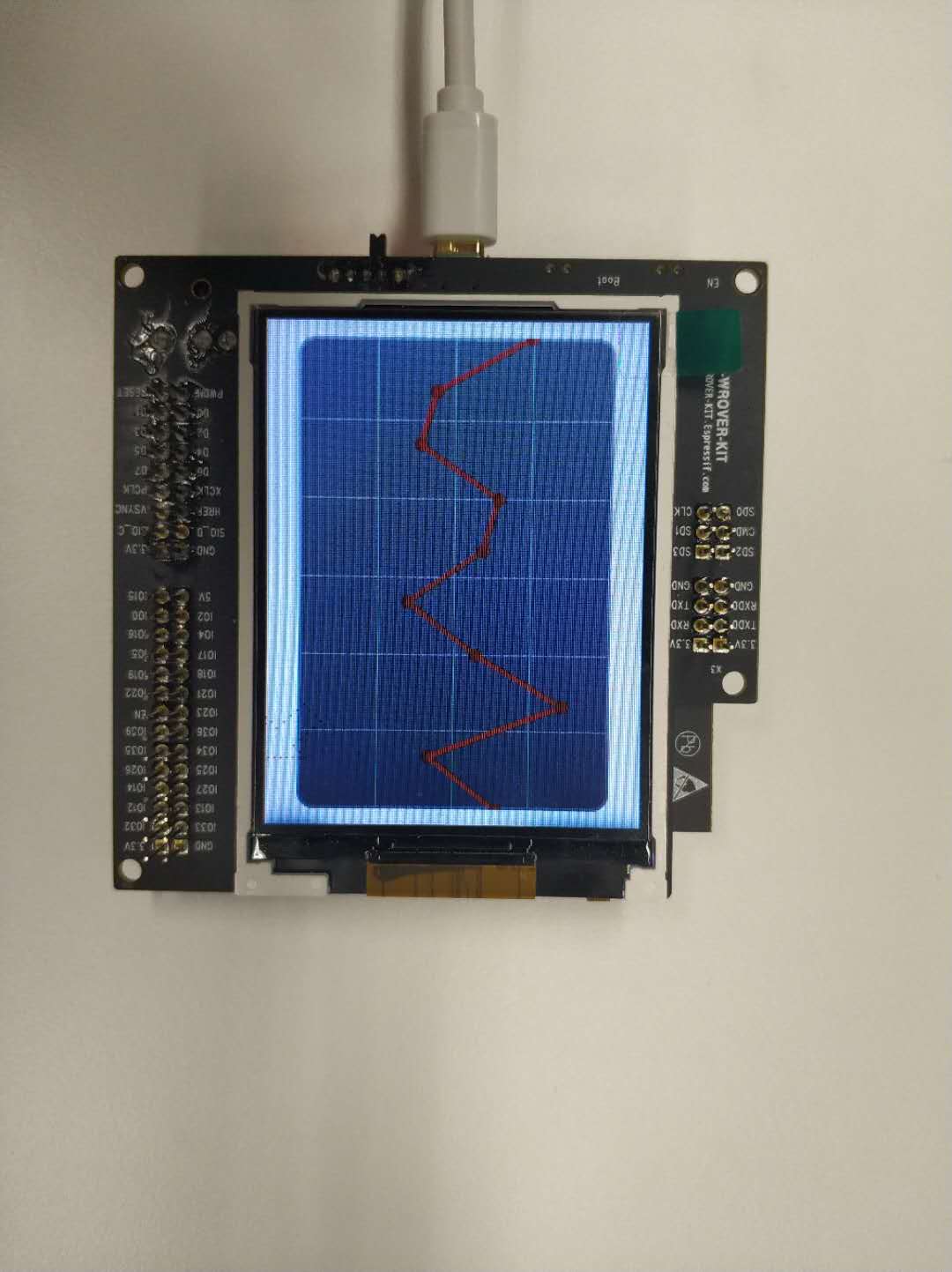

#151 ESP32/ESP8266 » 移植LittlevGL到ESP32 » 2018-07-06 17:08:00

- msr06rr

- 回复: 14

乐鑫的IDF软件写的真的是单片机领域的linux级别,手上正好有一块ESP-WROVER-KIT开发板,自带一块320*240分辨率的TFT液晶屏,虽然ESP32不是为这类显示屏而生,但是人家主频性能好啊,DMA加速一下,跑个简单的界面no problem的,我又不用它来播放视频。

LittlevGL的官方其实已经移植了一个版本,但是在写法上没有充分利用好dma的优势,这里仿照着乐鑫的example写了一个chart demo

上图

上代码

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include "driver/spi_master.h"

#include "driver/gpio.h"

#include "freertos/FreeRTOS.h"

#include "freertos/task.h"

#include "esp_freertos_hooks.h"

#include "lvgl.h"

#define PIN_NUM_MISO 25

#define PIN_NUM_MOSI 23

#define PIN_NUM_CLK 19

#define PIN_NUM_CS 22

#define PIN_NUM_DC 21

#define PIN_NUM_RST 18

#define PIN_NUM_BCKL 5

typedef struct

{

uint8_t cmd;

uint8_t data[16];

uint8_t databytes; //No of data in data; bit 7 = delay after set; 0xFF = end of cmds.

} lcd_init_cmd_t;

typedef enum

{

LCD_TYPE_ILI = 1,

LCD_TYPE_ST,

LCD_TYPE_MAX,

} type_lcd_t;

static spi_device_handle_t spi;

DRAM_ATTR static const lcd_init_cmd_t st_init_cmds[] = {

/* Memory Data Access Control, MX=MV=1, MY=ML=MH=0, RGB=0 */

{0x36, {(1 << 5) | (1 << 6)}, 1},

/* Interface Pixel Format, 16bits/pixel for RGB/MCU interface */

{0x3A, {0x55}, 1},

/* Porch Setting */

{0xB2, {0x0c, 0x0c, 0x00, 0x33, 0x33}, 5},

/* Gate Control, Vgh=13.65V, Vgl=-10.43V */

{0xB7, {0x45}, 1},

/* VCOM Setting, VCOM=1.175V */

{0xBB, {0x2B}, 1},

/* LCM Control, XOR: BGR, MX, MH */

{0xC0, {0x2C}, 1},

/* VDV and VRH Command Enable, enable=1 */

{0xC2, {0x01, 0xff}, 2},

/* VRH Set, Vap=4.4+... */

{0xC3, {0x11}, 1},

/* VDV Set, VDV=0 */

{0xC4, {0x20}, 1},

/* Frame Rate Control, 60Hz, inversion=0 */

{0xC6, {0x0f}, 1},

/* Power Control 1, AVDD=6.8V, AVCL=-4.8V, VDDS=2.3V */

{0xD0, {0xA4, 0xA1}, 1},

/* Positive Voltage Gamma Control */

{0xE0, {0xD0, 0x00, 0x05, 0x0E, 0x15, 0x0D, 0x37, 0x43, 0x47, 0x09, 0x15, 0x12, 0x16, 0x19}, 14},

/* Negative Voltage Gamma Control */

{0xE1, {0xD0, 0x00, 0x05, 0x0D, 0x0C, 0x06, 0x2D, 0x44, 0x40, 0x0E, 0x1C, 0x18, 0x16, 0x19}, 14},

/* Sleep Out */

{0x11, {0}, 0x80},

/* Display On */

{0x29, {0}, 0x80},

{0, {0}, 0xff}};

DRAM_ATTR static const lcd_init_cmd_t ili_init_cmds[] = {

/* Power contorl B, power control = 0, DC_ENA = 1 */

{0xCF, {0x00, 0x83, 0X30}, 3},

/* Power on sequence control,

* cp1 keeps 1 frame, 1st frame enable

* vcl = 0, ddvdh=3, vgh=1, vgl=2

* DDVDH_ENH=1

*/

{0xED, {0x64, 0x03, 0X12, 0X81}, 4},

/* Driver timing control A,

* non-overlap=default +1

* EQ=default - 1, CR=default

* pre-charge=default - 1

*/

{0xE8, {0x85, 0x01, 0x79}, 3},

/* Power control A, Vcore=1.6V, DDVDH=5.6V */

{0xCB, {0x39, 0x2C, 0x00, 0x34, 0x02}, 5},

/* Pump ratio control, DDVDH=2xVCl */

{0xF7, {0x20}, 1},

/* Driver timing control, all=0 unit */

{0xEA, {0x00, 0x00}, 2},

/* Power control 1, GVDD=4.75V */

{0xC0, {0x26}, 1},

/* Power control 2, DDVDH=VCl*2, VGH=VCl*7, VGL=-VCl*3 */

{0xC1, {0x11}, 1},

/* VCOM control 1, VCOMH=4.025V, VCOML=-0.950V */

{0xC5, {0x35, 0x3E}, 2},

/* VCOM control 2, VCOMH=VMH-2, VCOML=VML-2 */

{0xC7, {0xBE}, 1},

/* Memory access contorl, MX=MY=0, MV=1, ML=0, BGR=1, MH=0 */

{0x36, {0x28}, 1},

/* Pixel format, 16bits/pixel for RGB/MCU interface */

{0x3A, {0x55}, 1},

/* Frame rate control, f=fosc, 70Hz fps */

{0xB1, {0x00, 0x1B}, 2},

/* Enable 3G, disabled */

{0xF2, {0x08}, 1},

/* Gamma set, curve 1 */

{0x26, {0x01}, 1},

/* Positive gamma correction */

{0xE0, {0x1F, 0x1A, 0x18, 0x0A, 0x0F, 0x06, 0x45, 0X87, 0x32, 0x0A, 0x07, 0x02, 0x07, 0x05, 0x00}, 15},

/* Negative gamma correction */

{0XE1, {0x00, 0x25, 0x27, 0x05, 0x10, 0x09, 0x3A, 0x78, 0x4D, 0x05, 0x18, 0x0D, 0x38, 0x3A, 0x1F}, 15},

/* Column address set, SC=0, EC=0xEF */

{0x2A, {0x00, 0x00, 0x00, 0xEF}, 4},

/* Page address set, SP=0, EP=0x013F */

{0x2B, {0x00, 0x00, 0x01, 0x3f}, 4},

/* Memory write */

{0x2C, {0}, 0},

/* Entry mode set, Low vol detect disabled, normal display */

{0xB7, {0x07}, 1},

/* Display function control */

{0xB6, {0x0A, 0x82, 0x27, 0x00}, 4},

/* Sleep out */

{0x11, {0}, 0x80},

/* Display on */

{0x29, {0}, 0x80},

{0, {0}, 0xff},

};

static void lcd_cmd(spi_device_handle_t spi, const uint8_t cmd)

{

esp_err_t ret;

spi_transaction_t t;

memset(&t, 0, sizeof(t)); //Zero out the transaction

t.length = 8; //Command is 8 bits

t.tx_buffer = &cmd; //The data is the cmd itself

t.user = (void *)0; //D/C needs to be set to 0

ret = spi_device_transmit(spi, &t); //Transmit!

assert(ret == ESP_OK); //Should have had no issues.

}

static void lcd_data(spi_device_handle_t spi, const uint8_t *data, int len)

{

esp_err_t ret;

spi_transaction_t t;

if (len == 0)

return; //no need to send anything

memset(&t, 0, sizeof(t)); //Zero out the transaction

t.length = len * 8; //Len is in bytes, transaction length is in bits.

t.tx_buffer = data; //Data

t.user = (void *)1; //D/C needs to be set to 1

ret = spi_device_transmit(spi, &t); //Transmit!

assert(ret == ESP_OK); //Should have had no issues.

}

static void lcd_spi_pre_transfer_callback(spi_transaction_t *t)

{

int dc = (int)t->user;

gpio_set_level(PIN_NUM_DC, dc);

}

static uint32_t lcd_get_id(spi_device_handle_t spi)

{

//get_id cmd

lcd_cmd(spi, 0x04);

spi_transaction_t t;

memset(&t, 0, sizeof(t));

t.length = 8 * 3;

t.flags = SPI_TRANS_USE_RXDATA;

t.user = (void *)1;

esp_err_t ret = spi_device_transmit(spi, &t);

assert(ret == ESP_OK);

return *(uint32_t *)t.rx_data;

}

static void my_disp_flush(int32_t x1, int32_t y1, int32_t x2, int32_t y2, const lv_color_t *color_map)

{

esp_err_t ret;

spi_transaction_t trans[6];

for (int x = 0; x < 6; x++)

{

memset(&trans[x], 0, sizeof(spi_transaction_t));

if ((x & 1) == 0)

{

//Even transfers are commands

trans[x].length = 8;

trans[x].user = (void *)0;

}

else

{

//Odd transfers are data

trans[x].length = 8 * 4;

trans[x].user = (void *)1;

}

trans[x].flags = SPI_TRANS_USE_TXDATA;

}

uint32_t size = (x2 - x1 + 1) * (y2 - y1 + 1);

uint8_t *color_u8 = (uint8_t *)color_map;

for (uint32_t i = 0; i < size * 2; i += 2)

{

color_u8[i] ^= color_u8[i + 1];

color_u8[i + 1] ^= color_u8[i];

color_u8[i] ^= color_u8[i + 1];

}

trans[0].tx_data[0] = 0x2A; //Column Address Set

trans[1].tx_data[0] = (x1 >> 8) & 0xFF; //Start Col High

trans[1].tx_data[1] = x1 & 0xFF; //Start Col Low

trans[1].tx_data[2] = (x2 >> 8) & 0xFF; //End Col High

trans[1].tx_data[3] = x2 & 0xFF; //End Col Low

trans[2].tx_data[0] = 0x2B; //Page address set

trans[3].tx_data[0] = (y1 >> 8) & 0xFF; //Start page high

trans[3].tx_data[1] = y1 & 0xFF; //start page low

trans[3].tx_data[2] = (y2 >> 8) & 0xFF; //end page high

trans[3].tx_data[3] = y2 & 0xFF; //end page low

trans[4].tx_data[0] = 0x2C; //memory write

trans[5].tx_buffer = color_map;

trans[5].flags = 0;

trans[5].length = size * 2 * 8;

//Queue all transactions.

for (int x = 0; x < 6; x++)

{

ret = spi_device_queue_trans(spi, &trans[x], portMAX_DELAY);

assert(ret == ESP_OK);

}

spi_transaction_t *rtrans;

for (int x = 0; x < 6; x++)

{

ret = spi_device_get_trans_result(spi, &rtrans, portMAX_DELAY);

assert(ret == ESP_OK);

}

lv_flush_ready();

}

static void spi_spec_init()

{

esp_err_t ret;

spi_bus_config_t buscfg = {

.miso_io_num = PIN_NUM_MISO,

.mosi_io_num = PIN_NUM_MOSI,

.sclk_io_num = PIN_NUM_CLK,

.quadwp_io_num = -1,

.quadhd_io_num = -1,

.max_transfer_sz = 12800};

spi_device_interface_config_t devcfg = {

.clock_speed_hz = 26 * 1000 * 1000,

.mode = 0, //SPI mode 0

.spics_io_num = PIN_NUM_CS, //CS pin

.queue_size = 7, //We want to be able to queue 7 transactions at a time

.pre_cb = lcd_spi_pre_transfer_callback, //Specify pre-transfer callback to handle D/C line

};

//Initialize the SPI bus

ret = spi_bus_initialize(HSPI_HOST, &buscfg, 1);

ESP_ERROR_CHECK(ret);

//Attach the LCD to the SPI bus

ret = spi_bus_add_device(HSPI_HOST, &devcfg, &spi);

ESP_ERROR_CHECK(ret);

}

static void lcd_init(spi_device_handle_t spi)

{

int cmd = 0;

const lcd_init_cmd_t *lcd_init_cmds;

//Initialize non-SPI GPIOs

gpio_set_direction(PIN_NUM_DC, GPIO_MODE_OUTPUT);

gpio_set_direction(PIN_NUM_RST, GPIO_MODE_OUTPUT);

gpio_set_direction(PIN_NUM_BCKL, GPIO_MODE_OUTPUT);

//Reset the display

gpio_set_level(PIN_NUM_RST, 0);

vTaskDelay(100 / portTICK_PERIOD_MS);

gpio_set_level(PIN_NUM_RST, 1);

vTaskDelay(100 / portTICK_PERIOD_MS);

//detect LCD type

uint32_t lcd_id = lcd_get_id(spi);

int lcd_detected_type = 0;

int lcd_type;

printf("LCD ID: %08X\n", lcd_id);

if (lcd_id == 0)

{

//zero, ili

lcd_detected_type = LCD_TYPE_ILI;

printf("ILI9341 detected.\n");

}

else

{

// none-zero, ST

lcd_detected_type = LCD_TYPE_ST;

printf("ST7789V detected.\n");

}

lcd_type = lcd_detected_type;

if (lcd_type == LCD_TYPE_ST)

{

printf("LCD ST7789V initialization.\n");

lcd_init_cmds = st_init_cmds;

}

else

{

printf("LCD ILI9341 initialization.\n");

lcd_init_cmds = ili_init_cmds;

}

//Send all the commands

while (lcd_init_cmds[cmd].databytes != 0xff)

{

lcd_cmd(spi, lcd_init_cmds[cmd].cmd);

lcd_data(spi, lcd_init_cmds[cmd].data, lcd_init_cmds[cmd].databytes & 0x1F);

if (lcd_init_cmds[cmd].databytes & 0x80)

{

vTaskDelay(100 / portTICK_PERIOD_MS);

}

cmd++;

}

///Enable backlight

gpio_set_level(PIN_NUM_BCKL, 0);

}

static void lv_tick_task(void)

{

lv_tick_inc(1);

}

static lv_obj_t *chart = NULL;

static lv_chart_series_t *series = NULL;

static void gui_init(void)

{

//Initialize LittlevGL Library

lv_init();

//Register display driver

lv_disp_drv_t disp;

lv_disp_drv_init(&disp);

disp.disp_flush = my_disp_flush;

lv_disp_drv_register(&disp);

//Bind littlevgl tick counter to FreeRTOS

esp_register_freertos_tick_hook(lv_tick_task);

//Create a new Screen

lv_obj_t *scr = lv_obj_create(NULL, NULL);

lv_scr_load(scr);

//Use alien theme

lv_theme_t *th = lv_theme_alien_init(100, NULL);

lv_theme_set_current(th);

chart = lv_chart_create(scr, NULL);

lv_obj_set_size(chart, 300, 200);

lv_obj_align(chart, NULL, LV_ALIGN_CENTER, 0, 0);

lv_chart_set_type(chart, LV_CHART_TYPE_POINT | LV_CHART_TYPE_LINE);

lv_chart_set_series_opa(chart, LV_OPA_70);

lv_chart_set_series_width(chart, 4);

lv_chart_set_range(chart, 0, 100);

series = lv_chart_add_series(chart, LV_COLOR_RED);

}

static void gui_turbo_task(void *pvParameter)

{

while (1)

{

vTaskDelay(100 / portTICK_PERIOD_MS);

lv_task_handler();

}

}

static void user_task(void *pvParameter)

{

uint8_t value = 0;

while (1)

{

value = esp_random() % 100;

lv_chart_set_next(chart, series, value);

vTaskDelay(1000 / portTICK_PERIOD_MS);

}

}

void app_main()

{

spi_spec_init();

lcd_init(spi);

gui_init();

xTaskCreate(

gui_turbo_task, //Task Function

"gui_turbo_task", //Task Name

2048, //Stack Depth

NULL, //Parameters

1, //Priority

NULL); //Task Handler

xTaskCreate(

user_task, //Task Function

"user_task", //Task Name

512, //Stack Depth

NULL, //Parameters

1, //Priority

NULL); //Task Handler

}#152 Re: RISC-V » 荔枝派 $9 RISC-V开发板 (开放购买) » 2018-05-05 22:57:57

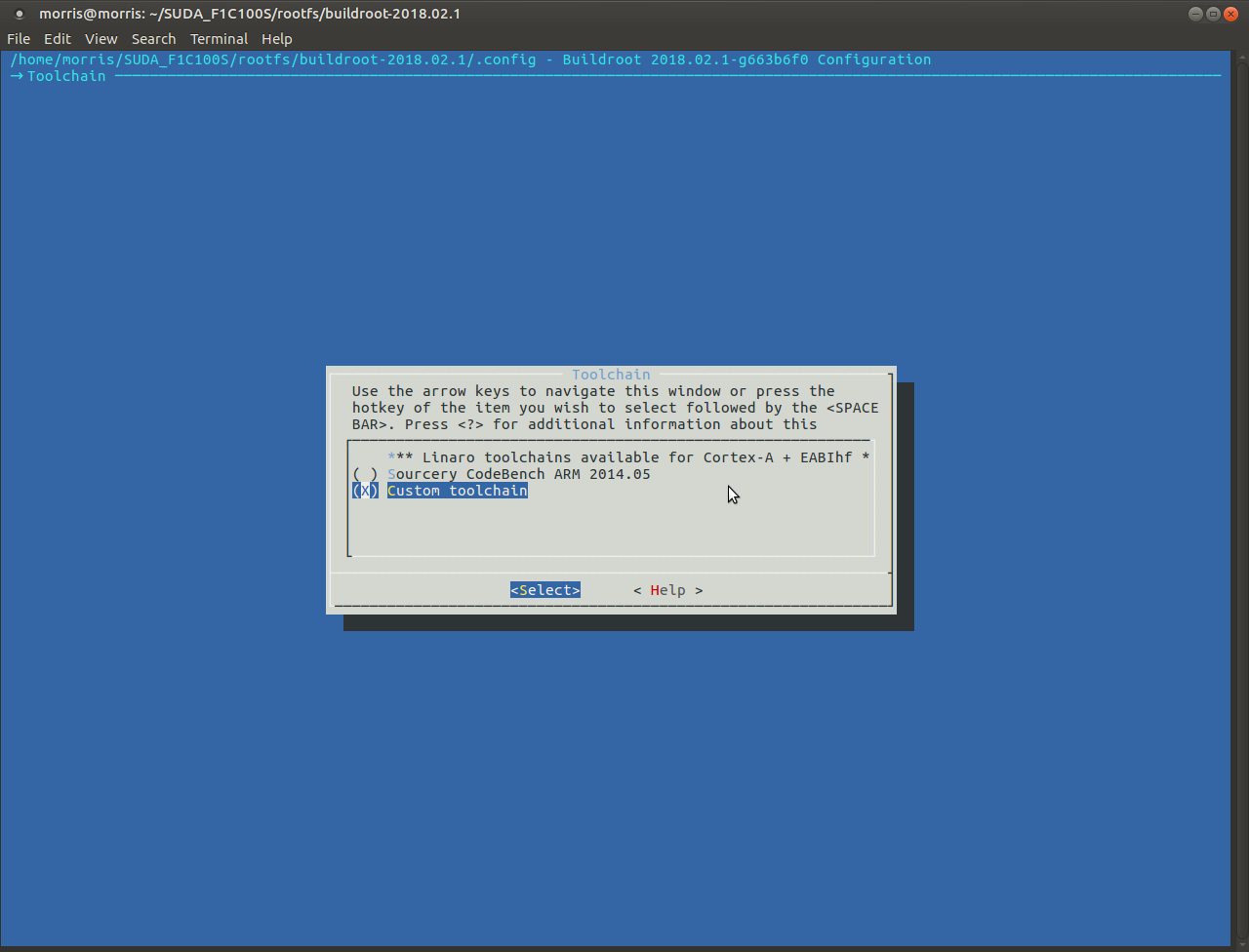

#153 Re: 全志 SOC » buildroot选择外部编译器的时候,貌似警告说linaro工具链只支持Cortex A的处理器。。。是这个意思吗? » 2018-04-30 11:06:04

这个问题也浪费了我几个小时,后来拿云盘上给的那个rootfs来对比,才发现:

1. arm-linux-gnueabi 这个工具链用来编译内核没有问题,编译应用则会出现问题;2. 编译应用的问题,是因为工具链所附加的库,是面向Cortex A7来编译的;因为假如只编译,不链接: arm-linux-gnueabi-gcc -Q -v -c -mcpu=arm926ej-s hello.c ,然后用readelf -A hello.o,会发现:Tag_CPU_name: "ARM926EJ-S";但只要链接了库,就成了:Tag_CPU_name: "7-A"

3. 解决方法,重新编译工具链,使得它附带的库是用于ARM926EJ-S的,方法是:

https://briolidz.wordpress.com/2012/02/07/building-embedded-arm-systems-with-crosstool-ng/

http://unisim-vp.org/site/crosstool-arm-926ejs-linux-gnueabi-how-to.html4. 之后再使用编译出来的external toolchain,也是完全OK的。

分析的很有道理,又学了一招。

我后来也是用crosstool-ng自己编了一套,还把c库换成了uclibc

#154 Re: 全志 SOC » F1C100s入坑记录(linux kernel失败!sunxi-fel, u-boot正常。) » 2018-04-20 17:28:02

晕哥,主线linux中的有电阻触摸驱动了吗?我编译了https://github.com/Lichee-Pi/linux中nano-4.14-exp分支的内核源码后没有发现event设备文件。

#155 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » [随便聊聊]在这个节骨眼上(某兴被禁止使用美帝的芯片),阿里把中天微收购了,是好事还是坏事? » 2018-04-20 13:03:12

#158 全志 SOC » 【貌似解决了】licheepi nano不接串口内核起不来 » 2018-04-19 22:19:39

- msr06rr

- 回复: 8

一开始以为是内核或者boot.scr的问题,后来发现每次插上串口都能一次性成功启动到登录界面

但是一旦拔了串口,就不行了,只停留在uboot的那一步,后面不动了。。

看了这篇博文后https://blog.csdn.net/guet_kite/article/details/78264740,说是串口的引脚受到干扰,以为是有按键输入。。。干扰怎么会有这么大的。。。,将信将疑,我把RX引脚接到地,再上电,有了!

各位坑有有木有谁也遇到过这种问题,你们是怎么解决的?

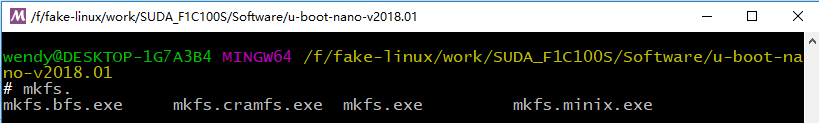

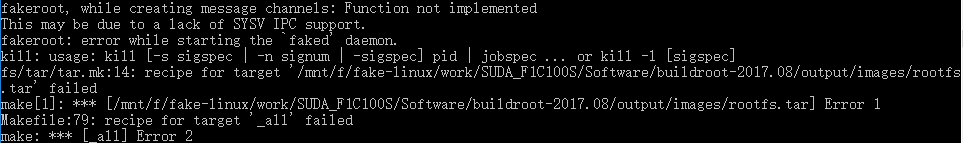

#159 全志 SOC » [解决]Win10 WSL系统下编译buildroot报错不支持SYSV IPC,导致fakeroot无法正常工作 » 2018-04-18 11:00:18

- msr06rr

- 回复: 13

经过实践,Win10的Linux子系统是完全可以直接用来进行嵌入式Linux开发操作的,目前已经非常顺畅地编译通过了U-Boot和内核。

但是编译Builtroot的最后阶段,需要使用fakeroot来fake文件权限的时候,报了个错误,如图所示:

据微软开发人员解释,目前WSL仅仅支持SYSV的信号量,消息队列还没有被实现(fakeroot需要SYSV的消息队列),但已经在规划中了,不知道猴年马月可以解决这个问题。。。

没办法,暂时的办法就是用fakeroot-tcp替换fakeroot-sysv咯

所以,撸起袖子这么干:cp -f /usr/bin/fakeroot-tcp path-to-buildroot/output/host/usr/bin/fakeroot

然后再编译就能通过了:)

#160 Re: 全志 SOC » Windows平台烧写f1c100s 荔枝派nano开发板步奏 » 2018-04-16 21:43:33

#161 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 模拟工程师的食谱了解一下 » 2018-04-09 22:51:15

- msr06rr

- 回复: 1

#162 Re: 全志 SOC » 荔枝派licheepi nano 全志(allwinnner) F1C100s 9.9¥ 开发板记录 (多图,流量党慎入!) » 2018-04-01 10:18:24

#163 Re: 全志 SOC » 荔枝派licheepi nano 全志(allwinnner) F1C100s 9.9¥ 开发板记录 (多图,流量党慎入!) » 2018-03-19 13:58:23

#164 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 创业点子太重要了, 这不,你看下这个【全能车】的app,可以把月卡帐号出租到【全能车】每天赚钱,5元/月可以骑多种共享车,免押金! » 2018-03-17 21:15:40

#167 Re: 全志 SOC » 如何讲uboot和内核的启动过程输出到液晶屏上?具体需要哪些操作? » 2018-01-22 18:53:07

这是哪里买的,什么价格?

淘宝上选的,这家公司号称永不停产,所以买了一个试试看,这是链接:

https://item.taobao.com/item.htm?spm=a1z09.2.0.0.4d5279a9Ck8oaD&id=44817078572&_u=m98jou42793

#168 Re: 全志 SOC » 如何讲uboot和内核的启动过程输出到液晶屏上?具体需要哪些操作? » 2018-01-22 14:52:02

#169 Re: 全志 SOC » 如何讲uboot和内核的启动过程输出到液晶屏上?具体需要哪些操作? » 2018-01-22 12:28:18

#170 Re: 全志 SOC » 如何讲uboot和内核的启动过程输出到液晶屏上?具体需要哪些操作? » 2018-01-21 23:22:39

#171 Re: 全志 SOC » 如何讲uboot和内核的启动过程输出到液晶屏上?具体需要哪些操作? » 2018-01-21 20:22:10

#172 Re: 全志 SOC » 如何讲uboot和内核的启动过程输出到液晶屏上?具体需要哪些操作? » 2018-01-21 20:21:08

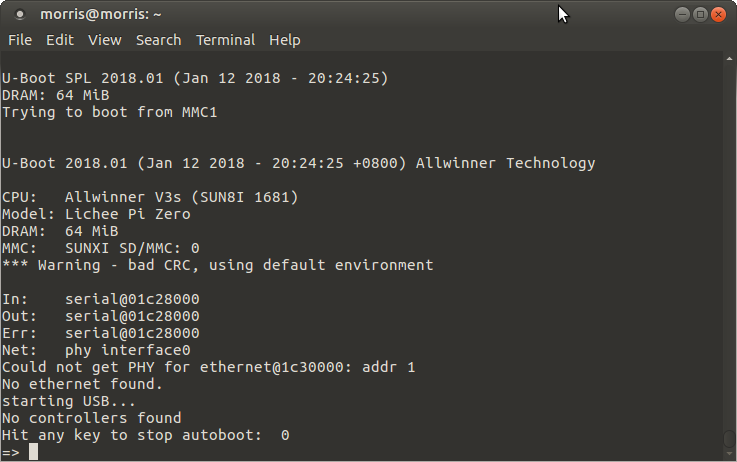

以下是uboot和kernel启动后的输出信息,能看出什么端倪吗?

U-Boot 2017.01-rc2 suda-morris (Jan 21 2018 - 20:17:47 +0800) Allwinner Technology

CPU: Allwinner V3s (SUN8I 1681)

Model: Lichee Pi Zero

DRAM: 64 MiB

MMC: SUNXI SD/MMC: 0

SF: Detected w25q128bv with page size 256 Bytes, erase size 4 KiB, total 16 MiB

*** Warning - bad CRC, using default environment

Setting up a 480x272 lcd console (overscan 0x0)

dotclock: 10000kHz = 10000kHz: (1 * 3MHz * 20) / 6

In: serial@01c28000

Out: serial@01c28000

Err: serial@01c28000

Net: phy interface0

eth0: ethernet@1c30000

starting USB...

No controllers found

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc0 is current device

Scanning mmc 0:1...

Found U-Boot script /boot.scr

reading /boot.scr

305 bytes read in 14 ms (20.5 KiB/s)

## Executing script at 41900000

reading zImage

3948464 bytes read in 220 ms (17.1 MiB/s)

reading sun8i-v3s-suda.dtb

11393 bytes read in 26 ms (427.7 KiB/s)

## Flattened Device Tree blob at 41800000

Booting using the fdt blob at 0x41800000

Loading Device Tree to 42dfa000, end 42dffc80 ... OK

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 4.13.0-licheepi-zero (morris@morris) (gcc version 6.4.1 20171012 (Linaro GCC 6.4-2017.11)) #1 SMP Sat Jan 13 18

[ 0.000000] CPU: ARMv7 Processor [410fc075] revision 5 (ARMv7), cr=10c5387d

[ 0.000000] CPU: div instructions available: patching division code

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] OF: fdt: Machine model: Lichee Pi Zero

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] percpu: Embedded 16 pages/cpu @c3edf000 s33868 r8192 d23476 u65536

[ 0.000000] Built 1 zonelists in Zone order, mobility grouping on. Total pages: 16129

[ 0.000000] Kernel command line: console=ttyS0,115200 panic=5 console=tty0 rootwait root=/dev/mmcblk0p2 earlyprintk rw vt.global_cursor_0

[ 0.000000] PID hash table entries: 256 (order: -2, 1024 bytes)

[ 0.000000] Dentry cache hash table entries: 8192 (order: 3, 32768 bytes)

[ 0.000000] Inode-cache hash table entries: 4096 (order: 2, 16384 bytes)

[ 0.000000] Memory: 54576K/65024K available (6144K kernel code, 217K rwdata, 1436K rodata, 1024K init, 262K bss, 10448K reserved, 0K cma)

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] vector : 0xffff0000 - 0xffff1000 ( 4 kB)

[ 0.000000] fixmap : 0xffc00000 - 0xfff00000 (3072 kB)

[ 0.000000] vmalloc : 0xc4000000 - 0xff800000 ( 952 MB)

[ 0.000000] lowmem : 0xc0000000 - 0xc3f80000 ( 63 MB)

[ 0.000000] pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)

[ 0.000000] modules : 0xbf000000 - 0xbfe00000 ( 14 MB)

[ 0.000000] .text : 0xc0008000 - 0xc0700000 (7136 kB)

[ 0.000000] .init : 0xc0900000 - 0xc0a00000 (1024 kB)

[ 0.000000] .data : 0xc0a00000 - 0xc0a36680 ( 218 kB)

[ 0.000000] .bss : 0xc0a3d868 - 0xc0a7f06c ( 263 kB)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[ 0.000000] Hierarchical RCU implementation.

[ 0.000000] RCU event tracing is enabled.

[ 0.000000] RCU restricting CPUs from NR_CPUS=8 to nr_cpu_ids=1.

[ 0.000000] RCU: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=1

[ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

[ 0.000000] arch_timer: cp15 timer(s) running at 24.00MHz (virt).

[ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x588fe9dc0, max_idle_ns: 440795202592 ns

[ 0.000008] sched_clock: 56 bits at 24MHz, resolution 41ns, wraps every 4398046511097ns

[ 0.000021] Switching to timer-based delay loop, resolution 41ns

[ 0.000183] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns

[ 0.000412] Console: colour dummy device 80x30

[ 0.000836] console [tty0] enabled

[ 0.000875] Calibrating delay loop (skipped), value calculated using timer frequency.. 48.00 BogoMIPS (lpj=240000)

[ 0.000913] pid_max: default: 32768 minimum: 301

[ 0.001054] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.001087] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.001705] CPU: Testing write buffer coherency: ok

[ 0.002094] /cpus/cpu@0 missing clock-frequency property

[ 0.002140] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

[ 0.002609] Setting up static identity map for 0x40100000 - 0x40100060

[ 0.002813] Hierarchical SRCU implementation.

[ 0.003342] smp: Bringing up secondary CPUs ...

[ 0.003375] smp: Brought up 1 node, 1 CPU

[ 0.003395] SMP: Total of 1 processors activated (48.00 BogoMIPS).

[ 0.003416] CPU: All CPU(s) started in SVC mode.

[ 0.004191] devtmpfs: initialized

[ 0.007204] VFP support v0.3: implementor 41 architecture 2 part 30 variant 7 rev 5

[ 0.007498] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.007560] futex hash table entries: 256 (order: 2, 16384 bytes)

[ 0.007742] pinctrl core: initialized pinctrl subsystem

[ 0.008637] random: get_random_u32 called from bucket_table_alloc+0xf4/0x244 with crng_init=0

[ 0.008811] NET: Registered protocol family 16

[ 0.009287] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.010534] hw-breakpoint: found 5 (+1 reserved) breakpoint and 4 watchpoint registers.

[ 0.010585] hw-breakpoint: maximum watchpoint size is 8 bytes.

[ 0.023682] SCSI subsystem initialized

[ 0.024017] usbcore: registered new interface driver usbfs

[ 0.024099] usbcore: registered new interface driver hub

[ 0.024210] usbcore: registered new device driver usb

[ 0.024486] pps_core: LinuxPPS API ver. 1 registered

[ 0.024512] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.024560] PTP clock support registered

[ 0.024800] Advanced Linux Sound Architecture Driver Initialized.

[ 0.026641] clocksource: Switched to clocksource arch_sys_counter

[ 0.037591] NET: Registered protocol family 2

[ 0.038211] TCP established hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.038272] TCP bind hash table entries: 1024 (order: 1, 8192 bytes)

[ 0.038310] TCP: Hash tables configured (established 1024 bind 1024)

[ 0.038453] UDP hash table entries: 256 (order: 1, 8192 bytes)

[ 0.038517] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes)

[ 0.038746] NET: Registered protocol family 1

[ 0.039345] RPC: Registered named UNIX socket transport module.

[ 0.039391] RPC: Registered udp transport module.

[ 0.039409] RPC: Registered tcp transport module.

[ 0.039428] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.041567] workingset: timestamp_bits=30 max_order=14 bucket_order=0

[ 0.050571] NFS: Registering the id_resolver key type

[ 0.050652] Key type id_resolver registered

[ 0.050672] Key type id_legacy registered

[ 0.051705] random: fast init done

[ 0.054690] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 249)

[ 0.054745] io scheduler noop registered

[ 0.054764] io scheduler deadline registered

[ 0.055035] io scheduler cfq registered (default)

[ 0.055062] io scheduler mq-deadline registered

[ 0.055079] io scheduler kyber registered

[ 0.059523] sun8i-v3s-pinctrl 1c20800.pinctrl: initialized sunXi PIO driver

[ 0.128836] Serial: 8250/16550 driver, 8 ports, IRQ sharing disabled

[ 0.132260] console [ttyS0] disabled

[ 0.152567] 1c28000.serial: ttyS0 at MMIO 0x1c28000 (irq = 35, base_baud = 1500000) is a U6_16550A

[ 0.734998] console [ttyS0] enabled

[ 0.741900] libphy: Fixed MDIO Bus: probed

[ 0.746461] dwmac-sun8i 1c30000.ethernet: PTP uses main clock

[ 0.752375] dwmac-sun8i 1c30000.ethernet: No regulator found

[ 0.758137] dwmac-sun8i 1c30000.ethernet: Will use internal PHY

[ 0.764146] dwmac-sun8i 1c30000.ethernet: Current syscon value is not the default 148000 (expect 38000)

[ 0.773750] dwmac-sun8i 1c30000.ethernet: Chain mode enabled

[ 0.779450] dwmac-sun8i 1c30000.ethernet: No HW DMA feature register supported

[ 0.786698] dwmac-sun8i 1c30000.ethernet: Normal descriptors

[ 0.792363] dwmac-sun8i 1c30000.ethernet: RX Checksum Offload Engine supported

[ 0.799607] dwmac-sun8i 1c30000.ethernet: COE Type 2

[ 0.804578] dwmac-sun8i 1c30000.ethernet: TX Checksum insertion supported

[ 0.811571] libphy: stmmac: probed

[ 0.816939] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 0.823502] ehci-platform: EHCI generic platform driver

[ 0.829084] ehci-platform 1c1a000.usb: EHCI Host Controller

[ 0.834722] ehci-platform 1c1a000.usb: new USB bus registered, assigned bus number 1

[ 0.842732] ehci-platform 1c1a000.usb: irq 25, io mem 0x01c1a000

[ 0.876664] ehci-platform 1c1a000.usb: USB 2.0 started, EHCI 1.00

[ 0.883845] hub 1-0:1.0: USB hub found

[ 0.887839] hub 1-0:1.0: 1 port detected

[ 0.892346] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

[ 0.898665] ohci-platform: OHCI generic platform driver

[ 0.904223] ohci-platform 1c1a400.usb: Generic Platform OHCI controller

[ 0.910969] ohci-platform 1c1a400.usb: new USB bus registered, assigned bus number 2

[ 0.918982] ohci-platform 1c1a400.usb: irq 26, io mem 0x01c1a400

[ 0.991737] hub 2-0:1.0: USB hub found

[ 0.995593] hub 2-0:1.0: 1 port detected

[ 1.003220] udc-core: couldn't find an available UDC - added [g_cdc] to list of pending drivers

[ 1.012810] input: 1c22800.lradc as /devices/platform/soc/1c22800.lradc/input/input0

[ 1.021814] sun6i-rtc 1c20400.rtc: rtc core: registered rtc-sun6i as rtc0

[ 1.028745] sun6i-rtc 1c20400.rtc: RTC enabled

[ 1.033306] i2c /dev entries driver

[ 1.038537] sunxi-wdt 1c20ca0.watchdog: Watchdog enabled (timeout=16 sec, nowayout=0)

[ 1.106891] sunxi-mmc 1c0f000.mmc: base:0xc4101000 irq:23

[ 1.114025] usbcore: registered new interface driver usbhid

[ 1.119721] usbhid: USB HID core driver

[ 1.125171] sun4i-codec 1c22c00.codec: ASoC: /soc/codec-analog@01c23000 not registered

[ 1.133252] sun4i-codec 1c22c00.codec: Failed to register our card

[ 1.140822] NET: Registered protocol family 17

[ 1.145420] Key type dns_resolver registered

[ 1.149960] Registering SWP/SWPB emulation handler

[ 1.162501] simple-framebuffer 43f80000.framebuffer: framebuffer at 0x43f80000, 0x7f800 bytes, mapped to 0xc4300000

[ 1.173168] simple-framebuffer 43f80000.framebuffer: format=x8r8g8b8, mode=480x272x32, linelength=1920

[ 1.185424] Console: switching to colour frame buffer device 60x34

[ 1.193969] simple-framebuffer 43f80000.framebuffer: fb0: simplefb registered!

[ 1.202597] usb_phy_generic usb_phy_generic.0.auto: usb_phy_generic.0.auto supply vcc not found, using dummy regulator