- 首页

- » 搜索

- » jiaowoxiaolu 发表的帖子

页次: 1

#1 Re: 全志 SOC » F1C100S的io初始化求助 » 2024-05-08 08:45:46

你确定是0x01c208b4+0xB4而不是0x01c20800+0xB4 吗,一般基地址都是0结尾的

#2 Re: Xilinx/Altera/FPGA/CPLD/Verilog » EBAZ4205可以设计PL端的串口吗? » 2024-04-17 15:17:39

你的是纯逻辑不包含PS功能的话分配引脚后编译出bit下载进去就能用,ps运行起来会有点温度,正常现象

#3 Re: Xilinx/Altera/FPGA/CPLD/Verilog » EBAZ4205可以设计PL端的串口吗? » 2024-04-17 08:30:04

纯逻辑代码的话在vivado内有引脚分配对话框,自己找找看,xilinx本身也提供了串口的IP,可以和cpu配合使用的

#4 Re: Xilinx/Altera/FPGA/CPLD/Verilog » AG RV2K 调试 » 2024-04-03 08:50:17

我是直接修改verilog,然后点编译,再到supra点编译下载,或者修改了VE文件也会在supra编译一次才下载,现象就和我上面说的一样

顺便问一下,这个VE引脚配置,没有上下拉设置和电平类型设置的? 其他家的fpga大多数都有这种设置,就AGM的没有?

#5 Re: Xilinx/Altera/FPGA/CPLD/Verilog » AG RV2K 调试 » 2024-04-01 09:07:33

前两天也试了他们的AGRV2K,发现他们的编译器有点玄学,不懂怎么回事,有时候改一个引脚分配文件把引脚映射到另外一个IO,其他啥都不变,编译下载后结果不符合预期,有时候引脚没变,单纯修改verilog逻辑,改变某个引脚后编译下载,结果又不符合预期,但是偶尔从新按照他们的新建工程步骤,代码不变新建编译下载竟然又符合预期了,搞得我很迷茫。。。。

#6 Re: 全志 SOC » 有偿求助,有一份从spiflash内dump出的(UBI)rootfs,我自己添加了东西后如何从新再打包成原来的UBI文件系统 » 2024-03-14 16:16:32

自己结贴吧,用nandsim,和mtd-util配合搞定了,需要挂载到电脑后修改文件,再打包,不可以用binwalk或者ubi_reader解包后再打包,解包后打包的不能运行,挂载到电脑再打包的就可以正常使用了

#7 Re: 全志 SOC » 有偿求助,有一份从spiflash内dump出的(UBI)rootfs,我自己添加了东西后如何从新再打包成原来的UBI文件系统 » 2024-03-12 13:35:00

我的思路是

pc 用命令mount flash读出来的bin, mtd -> ubi 然后ubiattach

挂载ubi

修改内容后

umount, 把bin重新写入flash

确定可行吗?要不给你试试?

#8 Re: 全志 SOC » 有偿求助,有一份从spiflash内dump出的(UBI)rootfs,我自己添加了东西后如何从新再打包成原来的UBI文件系统 » 2024-03-12 13:34:23

ubi 不是可读写的吗 你把要放的东西放进去,然后再读出来不就行了吗

主机无法登陆,原机关闭了任何外界接口,只能先改rootfs打开tty,结果不懂打包回去,尴尬了

#9 全志 SOC » 有偿求助,有一份从spiflash内dump出的(UBI)rootfs,我自己添加了东西后如何从新再打包成原来的UBI文件系统 » 2024-03-12 10:59:53

- jiaowoxiaolu

- 回复: 8

有个V3s芯片的设备想自己DIY一些东西进去,遂用编程器读出了W25N01的数据,然后解压出了rootfs,修改了自己的东西

但是目前卡在了如何重新打包rootfs这个问题上,有没有大佬能帮忙指导一下,可付费

文件系统是UBI 格式,V3s芯片 W25N01 SPI nand启动

#10 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 【拆机】拆一个收来的光波导的AR眼镜Rokid Glass 2,内附多图 » 2024-01-16 08:50:37

不知道实际效果如何,如果用来做航模FPV飞行眼镜会怎样?

#11 Re: 全志 SOC » t113 udhcpc问题 » 2023-11-27 11:56:49

如果启动完后手动启动udhcp可以正常的话那就是启动顺序的问题,改下init.d,把udhcpc启动脚本放到最后启动(S90)应该就行了

#12 Re: 全志 SOC » t113 udhcpc问题 » 2023-11-27 09:30:39

是不是可以等启动完后手动启动一下udhcpc试试?

#13 Re: 工业芯 匠芯创 » MCU内存小怎么办?ArtInChip RTOS平台XIP技术揭秘 » 2023-11-20 09:15:37

最重要的加密怎么搞

#14 Re: 全志 SOC » 用f1C200S加TF卡做了一个U盘程序,还差一个在电脑中鼠标右键"弹出"功能有问题 » 2023-11-15 09:57:54

弹出应该是电脑端的事情,底下不需要特别处理

#15 Re: 全志 SOC » 【开源】无线J-Link(V831+XR829+AXP2101+STM32F072C8) » 2023-09-25 14:52:37

不错,segger提供的JLinkRemoteServerCLExe是源码?需要自己编译?

#16 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 临时百度帐号? » 2023-09-05 09:36:54

淘宝买个临时会员,几毛到几块不等,卖家会给你账号,用什么自己注册这么麻烦

#17 Re: 华芯微特 » SWM341 » 2023-08-18 13:37:18

用厂家的串口ISP工具全片擦掉

#18 Re: 全志 SOC » V3s SPI Nor Flash Uboot的可以裁剪到多大啊 » 2023-08-02 17:16:17

如果用不着uboot自带那些命令的话有很多东西能裁掉吧,logo很大的话光logo就占用不少体积

#19 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 找一个资深些的外包,做软件无线电相关,使用ZYNQ相关平台开发产品,具体要求请看内容 » 2023-06-28 08:48:00

这个是个大活,一般人搞不定,不过据我了解 接收机都用上ZYNQ了才给3W功率,感觉不太够,我手上的产品也用zynq,运行起来cpu 都60度以上了,电流没实际量,感觉已经不止3W

#20 Re: 华芯微特 » 那位大神看看我的问题,帮忙解答下,非常感谢,卡了好久了。SWM34SVET6的PD15无法STOP唤醒,及如何降低功耗? » 2023-06-20 08:20:17

swm的低功耗本来就不咋地,即使stop模式也比其他低功耗系列大很多,进入stop也要注意把无关引脚设置成固定电平,而且swm的adc供电要另外处理,就像swm181系列的adc供电官方是用外部mos来关闭的

#21 Re: 全志 SOC » 有偿求助。 » 2023-03-03 08:38:22

@bfhou

如果所言为真,那不是自己搞个uboot这么简单,估计程序已经有加密,需要搞点逆向,费用不低

#22 Re: 全志 SOC » 有偿求助。 » 2023-03-02 15:08:14

确定固件没加密?直接换芯片能用?

简易先用一块好的板,拆掉H3,然后换你买的H3,能正常启动使用再说

#23 Re: Cortex M0/M3/M4/M7 » 有认识能破解STM32F103ZET6的吗 ? 介绍成功有重谢, 不要骂我实属无奈请开发公司写的程序量起来了烧写芯片恶意加价好几次 » 2022-12-16 14:09:49

stm32系列还是很好破的,3千多就能拿到bin,有搞过

#24 Re: 司徒开源 » 研究FC3000掌機的開源可行性 » 2022-10-27 08:50:49

@Situ:您正在为向全世界传播知识做出贡献,请继续自由地这样做,这对我们来说是非常宝贵的灵感来源!

#25 Re: 司徒开源 » 开源精神值得敬佩,但是你司徒公开po 解FC3000的加密芯片就是可耻,做技术要有底线 » 2022-10-27 08:48:10

@怀旧堂

说了一堆屁话,仿佛自己站在道德最高点,但是你别忘了你的代码也用到了其他开源软件,抛开ROM不说,先把GPL补一下,这件事确实是可以私下很好解决,非要公开让公众打脸。

#26 Re: 司徒开源 » 开源精神值得敬佩,但是你司徒公开po 解FC3000的加密芯片就是可耻,做技术要有底线 » 2022-10-26 18:04:33

平心而论,司徒的行为没啥不妥,毕竟他没拿成果去牟利,要是我的产品公开被人破解我心里当然也不爽,但是楼主明明拿了那么多有版权的游戏ROM牟利,反而在这里说起了底线,说起了版权,到底底线在哪?,如果你的东西完全是你自己搞出来的,包括其中的游戏,那你所要求的的无可厚非,但是现在这样子,我也支持司徒继续研究

请@Situ,继续您的出色工作!

#27 Re: 感芯科技 » MC3172芯片资料合集 » 2022-07-28 14:28:23

民用场合有这么高实时的需求不多,只有某些工业(你们有工业级温度范围了吗),汽车行业(你们有车规认证没有?),军工(这个就要求更多了吧),可能会用这么实时性的东西了吧

#28 Re: 感芯科技 » MC3172芯片资料合集 » 2022-07-28 13:54:17

初期没量,成本下不来啊,30左右算贵吗

30块的话基本没戏,10块左右估计还有点机会,硬多线程这个需求不太多,很多时候软多线程都能解决问题,都是点个灯,客户不会因为你是硬多线程就会多给你钱啊,现在国产遍地开花的情况下30块基本没啥竞争力

#29 Re: 感芯科技 » MC3172芯片资料合集 » 2022-07-28 08:53:43

不如说下大概价格,要不然申请回去测试很好,想换的时候一听价格xxx,那就很没意思了

#30 Re: 感芯科技 » MC3172用户测评汇总(持续更新) » 2022-07-28 08:51:54

牛逼的芯片,硬调度了,线程之间的通讯是不是只能靠全局变量了?

关系价格和供货情况,可惜ram还是小了点

#31 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】 » 2022-07-12 13:52:14

SN65LVDS049 这个应该正好

http://www.ti.com/cn/lit/gpn/sn65lvds049

#32 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】 » 2022-07-12 13:44:07

cpld不需要吧,直接用max485芯片或者mcp2551这类转一下就行了,专门转差分就用一颗CPLD大材小用了

#33 Re: 全志 SOC » 接触全志两个月, 打板竟然一次点亮,必须开个新贴,从此去他的H7xx... » 2022-07-07 08:50:51

阿黄 说:能裸奔RTL8822的就牛逼上天了,搬凳子观望!

RTL8822很厉害吗?

隔壁早就用上了, 还是在ST的平台上, 秒启动, 应该是裸奔了, 馋s我了.

听说速度能到1200Mbps, 没用过.

你说的隔壁是哪里?RTL8822是蓝牙+双频WIFI,裸奔能搞全很好了,目前我们为了用这个双频+蓝牙只能含泪上linux,有没有连接我去围观看看?

#34 Re: 全志 SOC » 接触全志两个月, 打板竟然一次点亮,必须开个新贴,从此去他的H7xx... » 2022-07-06 16:52:26

能裸奔RTL8822的就牛逼上天了,搬凳子观望!

#35 Re: 全志 SOC » 请问从内核态发一个消息给用户态的进程,一般用什么方法? » 2022-06-24 08:51:38

使用异步通知可以不?

#36 Re: Xilinx/Altera/FPGA/CPLD/Verilog » 最近研究了下Xilinx 的XVC,发现jlink有了个新玩法,可以白嫖一个xilinx高速下载器了 » 2022-05-09 09:00:59

XilinxVirtualCable能做这么高了? 我之前看别人用ESP或者各种派做的速度都特别低 除了能无线调试 没太大用途

速度瓶颈不在xvc协议,是在具体实现jtag移位出去的硬件上,esp做得大概只实现了功能,没往优化速度上下功夫,我用jlink来实现jtag比特流的输出,一是jlink烂大街,方便获得,0动手成本,2是jlink本身的jtag速度还是挺快的,v8老古董版本的jtag就比官方DLC cable下载器快不少了,土豪用jlink pro或者更高版本的话轻松快到超过zynq jtag最高速度

#37 Re: Xilinx/Altera/FPGA/CPLD/Verilog » FT4232H可用的Xilinx FPGA JTAG调试器EEPROM分享 » 2022-04-06 16:34:36

https://whycan.com/t_8054.html

来白嫖这里的,更方便

#38 Re: Xilinx/Altera/FPGA/CPLD/Verilog » 最近研究了下Xilinx 的XVC,发现jlink有了个新玩法,可以白嫖一个xilinx高速下载器了 » 2022-04-06 14:14:08

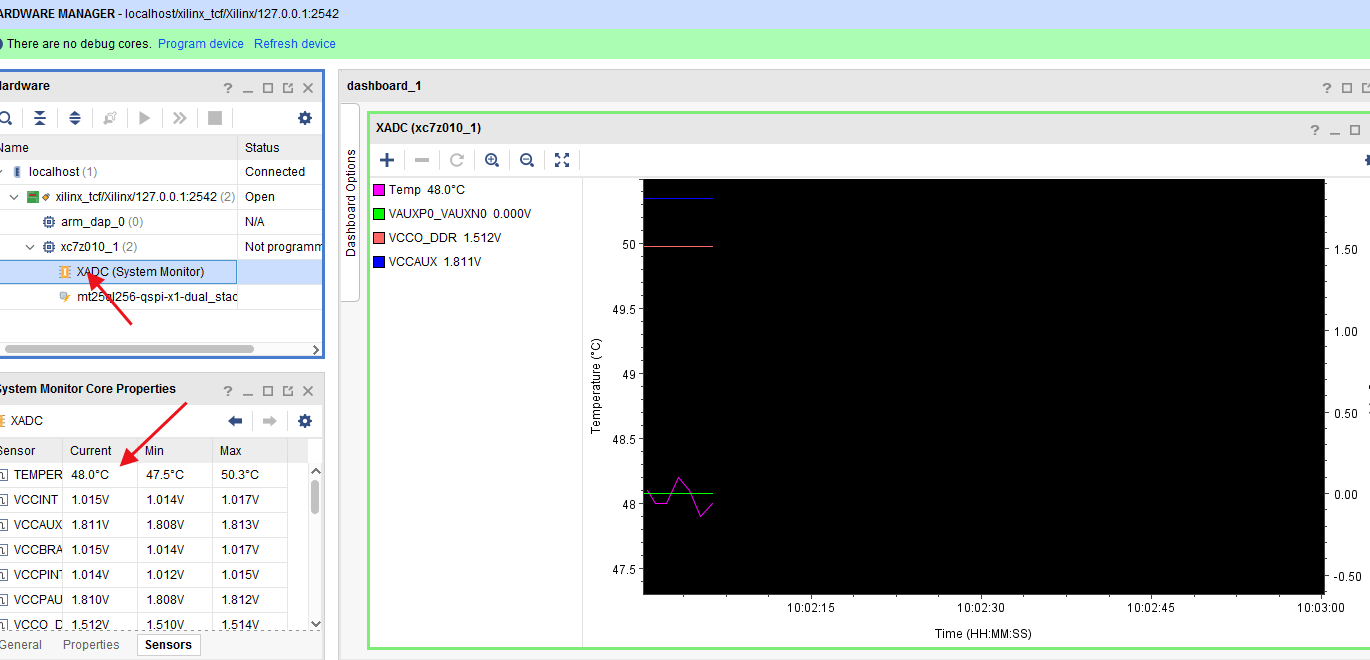

更新一下,下载外部flash是ok的,需要把启动模式设置为JTAG模式即可下载到外部flash

原本使用xilinx usb下载线烧写32M外部flash需要将近15分钟,现在直不到5分钟就搞定了

#39 Xilinx/Altera/FPGA/CPLD/Verilog » 最近研究了下Xilinx 的XVC,发现jlink有了个新玩法,可以白嫖一个xilinx高速下载器了 » 2022-04-06 11:49:49

- jiaowoxiaolu

- 回复: 42

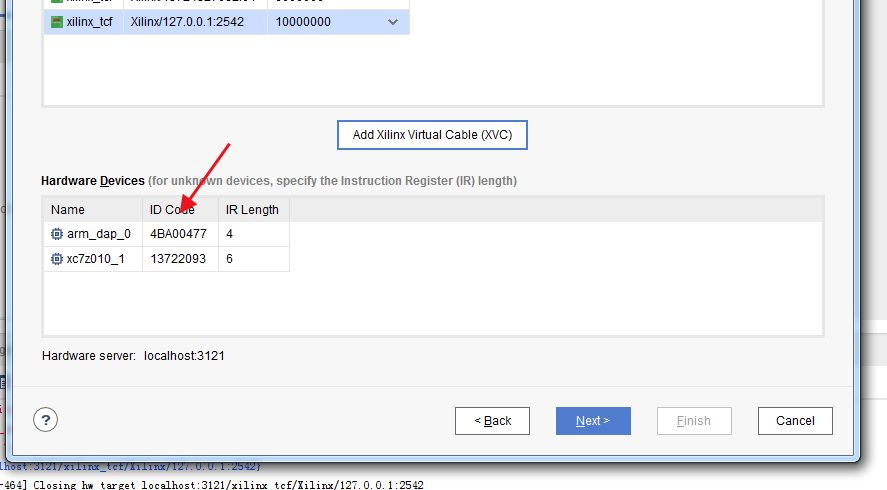

玩zynq板子的,是不是受够了platform usb cable 那乌龟一样的下载速度了?现在好了,使用手上的廉价jlink就可以调试zynq 芯片,速度还飞快。

最近搞zynq开发,实在是无法忍受platform usb cable那个下载调试速度,所以一直在找有没有更好的调试方法,结果发现xilinx官方提供了个XVC虚拟调试电缆这个东西。然后花了点时间研究了一下,发现实现起来还挺简单,所以打算自己搞一个试试,然后突发奇想,能不能省事点,直接用jlink来干这事?灵光一闪,想到了jlink其实有SDK的,可以通过程序自己控制jlink读写芯片,所以觉得这个想法应该是可行的,然后随便bing搜了下,好像没看到有先例,所以这个螃蟹只能我自己先尝尝了。。。

废话就不多说了,直接说关键点就好,感兴趣的可以自己深入研究。首先xilinx提供了xvc的详细文档xapp-1251,里面有xvc的协议说明,还提供了GitHub地址,里面有xvc server的实现代码,由于我使用的是window环境,因此我把xvc server代码下载下来,然后简单修改移植到了window,然后把里面的axi to jtag的操作代码替换为jlink sdk的jtag读写操作函数上,简单搞搞。不到半天就搞定了,

xvc server内主要修改了int handle_data这个函数

int handle_data(int fd)

{

do

{

memset(cmd, 0, 32);

if (sread(fd, cmd, 2) != 1)

return 1;

if (memcmp(cmd, "ge", 2) == 0)

{

if (sread(fd, cmd, 6) != 1)

return 1;

memcpy(TDO, xvcInfo, strlen(xvcInfo));

if (send(fd, (const char*)TDO, strlen(xvcInfo),0) != strlen(xvcInfo))

{

perror("write");

return 1;

}

if (verbose)

{

printf("%u : Received command: 'getinfo'\n", (int)time(NULL));

printf("\t Replied with %s\n", xvcInfo);

}

break;

}

else if (memcmp(cmd, "se", 2) == 0)

{

if (sread(fd, cmd, 9) != 1)

return 1;

memcpy(TDO, cmd + 5, 4);

if (send(fd, (const char*)TDO, 4,0) != 4)

{

perror("write");

return 1;

}

if (verbose)

{

printf("%u : Received command: 'settck'\n", (int)time(NULL));

printf("\t Replied with '%.*s'\n\n", 4, cmd + 5);

}

break;

}

else if (memcmp(cmd, "sh", 2) == 0)

{

if (sread(fd, cmd, 4) != 1)

return 1;

if (verbose)

{

printf("%u : Received command: 'shift'\n", (int)time(NULL));

}

}

else

{

fprintf(stderr, "invalid cmd '%s'\n", cmd);

return 1;

}

int len; //<num bits>

if (sread(fd, &len, 4) != 1)

{

fprintf(stderr, "reading length failed\n");

return 1;

}

int nr_bytes = (len + 7) / 8; //向上取整数字节

if (nr_bytes > sizeof(TDI))

{

fprintf(stderr, "buffer size exceeded\n");

return 1;

}

if (verbose)

{

printf("\tNumber of Bits : %d\n", len);

printf("\tNumber of Bytes : %d \n", nr_bytes);

printf("\n");

}

memset(&TDO, 0, nr_bytes);

if (sread(fd, TMS, nr_bytes ) != 1) //读取tms

{

fprintf(stderr, "reading tms data failed\n");

return 1;

}

if (sread(fd, TDI, nr_bytes) != 1) //读取tdi

{

fprintf(stderr, "reading tdi data failed\n");

return 1;

}

JLINKARM_JTAG_StoreGetRaw((const U8*)&TDI, (U8*)&TDO, (const U8*)&TMS, len);

if (send(fd, (const char*)TDO, nr_bytes,0) != nr_bytes)

{

perror("write");

return 1;

}

break;

} while (1);

return 0;

}

编译好的exe文件,感兴趣的可以试试

https://whycan.com/files/members/7197/XVC.rar

目前有点问题没解决,就是可以下载bit文件但是无法烧写外部flash,目前还搞不清楚原因。

如果需要在vitis内使用xvc,目前我摸索出的方法是在vivado内设置xvc并连接到芯片,然后切换到vitis就可以在debug内找到xvc了,测试vitis内点击debug可以正常下载调试,其他功能未详细测试,目前xvc server速度我设置为30M,对比Platform usb cable真是速度提升明显,吃灰的矿渣zynq板又可以拉出来溜溜了!

由于jlink sdk有版权问题,为避免麻烦,sdk和源码就不上传这里了,sdk在GitHub就可以下载到,自己找找就好

#40 Re: 全志 SOC » 网站需要改革,放开文件下载权限(不需要与积分挂钩) » 2021-12-09 16:44:42

@哇酷小二

其实amobbs早期的崛起,吸引大量注册用户和他前期的免费下载所有资料有不少关系,当然这个各有利弊,各有各的看法

#41 Re: 全志 SOC » 网站需要改革,放开文件下载权限(不需要与积分挂钩) » 2021-12-09 16:22:40

楼主以前也在amobbs吧,我对你的名字有点印象,这里也有不少那边过来的牛人

#42 Re: 全志 SOC » 开源一个6000行的2D矢量图形库libcg,零依赖,API接口类似cairo,在某些场景可以代替cairo,特别适合裸奔场景。 » 2021-12-03 17:33:54

大佬牛逼了

#43 Re: 好钜润半导体(TIKY) » 坛内有没有对TKM32F499非常熟悉的朋友,愿意付费请教 » 2021-11-22 13:50:33

需要要写什么例程?或许可以帮忙

页次: 1

- 首页

- » 搜索

- » jiaowoxiaolu 发表的帖子