- 首页

- » 搜索

- » sunwei 发表的帖子

页次: 1

#1 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 17:10:51

#2 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 17:00:02

#3 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 16:56:08

#4 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 16:47:40

#5 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 16:38:23

#6 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 16:32:36

#7 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 16:29:14

#8 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 16:20:58

提供一个信息。到2035年。深圳会建造100万套的政策房。把商品房的比例从%80减少到%40,

2000万人,平均每月5000开销,就可以年创造1.2万亿的gdp, 想想gdp与人口消费的关系。 (5000块是指平摊。包括各种公司平摊到你声上的费用)

其实有时候产品不重要。而是创造消费增量重要。

想想过去要做少衣服外销,才能有1.2万亿。 那需要多少棉花。 而我们自己确要穿最低档的。

现在你只要撬动了消费。自己用好了穿好了。还能为社会做贡献。

知道为什么吃酒吃肉的,花天酒地的,越来越有了吧。因为他们是社会撬动市场的典范。(不包括很有钱的。那层次又不一样了。)

就像你做公司。流水是今后你的贷款数量的一个指标。

为什么房子能用来贷款。如果人人都卖了房子。又不能贷款。没有几个企业家会卖房子。这里面的点点滴滴值得去思考。

这里面的机制是什么。400万,你出100万。说明你有能力消费,会消费。继续给予资金的支持。你也算投资了。接下来的300万你还是得还。

什么时候你能还完不重要。但你要保持还贷能持续。怎么维持这些债务,一直保持平衡不出问题。都是个综合性的问题。

总归是,你不但要搞完自己的本质工作。你还要完成这些综合的事物。(我们国家综合事物,也包含了吃喝玩乐,至于今后的吃喝玩乐。会升华到一个什么型态就不知道了)

#9 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 15:52:11

#10 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 15:45:23

#11 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2019-01-25 15:43:59

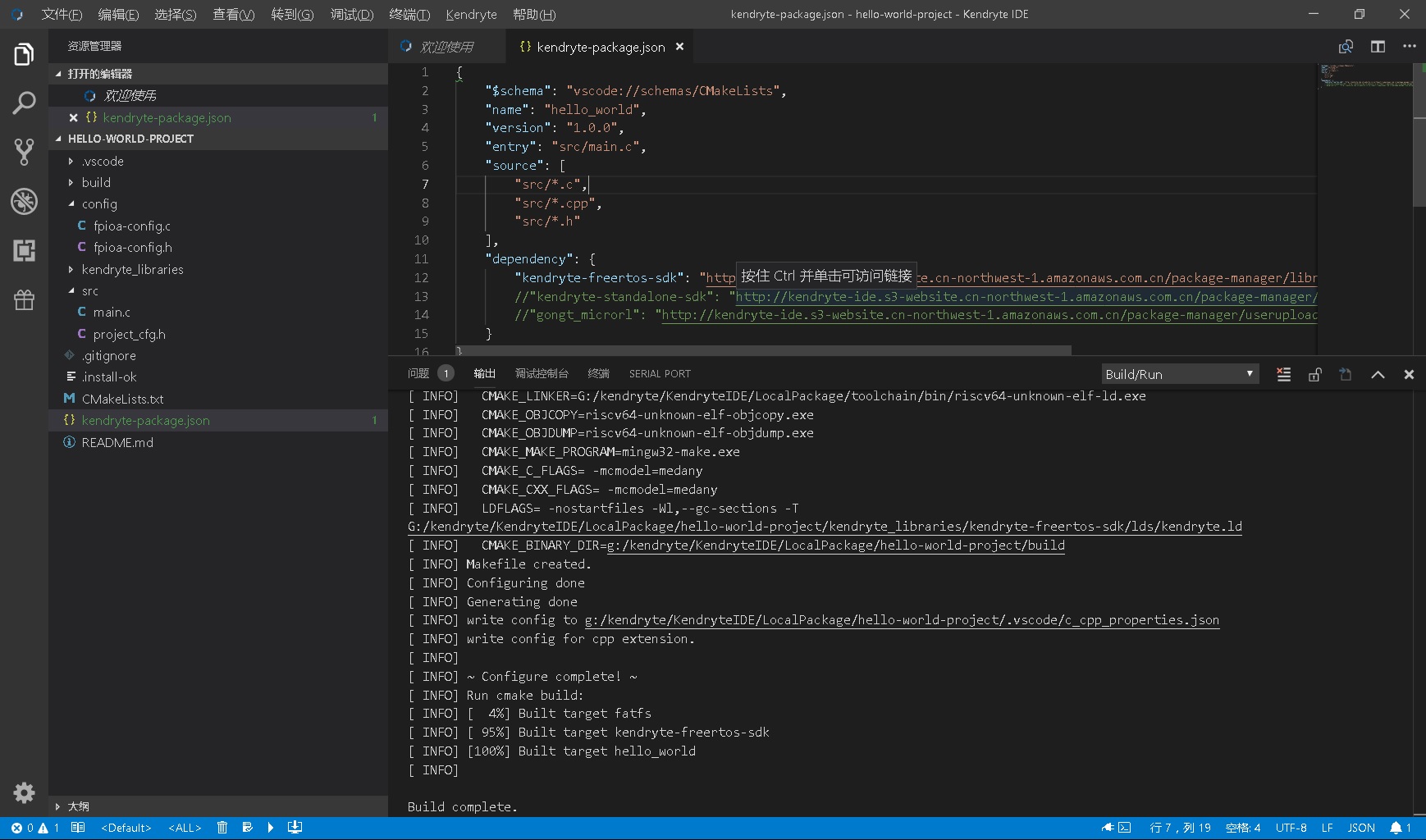

#12 Re: RISC-V » k210 编译成功。可惜没板子试 » 2019-01-25 15:39:01

#14 Re: 全志 SOC » F1c200s芯片也到了,晒晒 » 2019-01-24 01:15:00

#15 Re: 全志 SOC » F1c200s芯片也到了,晒晒 » 2019-01-21 02:31:14

#16 RISC-V » 机器学习软件 » 2018-12-13 19:24:59

#18 Re: RISC-V » 对于芯片的猜想 » 2018-12-09 12:25:27

#19 RISC-V » 对于芯片的猜想 » 2018-12-08 18:11:47

#21 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-18 00:26:25

#22 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-18 00:19:50

#23 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 23:46:16

#24 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 23:44:54

#25 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 23:39:02

#26 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 23:09:50

上传了一个代码。还没做好。希望对你们有帮助。 xboot_sp.rar

#27 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 23:06:10

#28 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 23:02:11

#29 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 22:44:20

#30 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 22:33:49

#31 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 22:32:11

#32 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 22:26:31

#33 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 22:21:11

#34 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 22:10:11

#35 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 21:26:22

#36 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 19:49:11

#37 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 19:39:47

#38 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 19:35:57

#39 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 19:01:37

#40 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 18:56:58

#41 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 18:52:06

#42 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 18:50:38

#43 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 18:37:04

#44 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 18:35:57

#45 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 18:33:34

#46 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 18:08:38

#47 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 17:45:50

#48 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 17:28:11

#49 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 17:01:24

#50 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 16:52:14

-p 选项是显示进度的吗

G:\rtthread\rt-thread-3.0.3\F!C100S资源包\建立新的SOC\新建文件夹\sunxi-tools-win32support_f1c100s>sunxi-fel spiflash-write -p 0 xboot.bin

Invalid option -p

G:\rtthread\rt-thread-3.0.3\F!C100S资源包\建立新的SOC\新建文件夹\sunxi-tools-win32support_f1c100s>sunxi-fel spiflash-write 0 xboot.bin

G:\rtthread\rt-thread-3.0.3\F!C100S资源包\建立新的SOC\新建文件夹\sunxi-tools-win32support_f1c100s>

#51 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 16:48:47

#52 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 16:30:28

#53 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 16:12:26

#54 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 16:02:36

#55 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 15:57:27

刚把spi_lck下拉,还是一样。

看样子。BROM是直接在ROM空间跑的,并且BROM程序只提供了简单的Fel工具的命令支持。

下面是显示的信息 1就是fel ,我改成了1

G:\rtthread\rt-thread-3.0.3\F!C100S资源包\建立新的SOC\新建文件夹>1 sid

Warning: no 'soc_sram_info' data for your SoC (id=1663)

SID registers for your SoC (0x1663) are unknown or inaccessible.'soc_sram_info'

Warning: no 'soc_sram_info' data for your SoC (id=1663)

这行代码估计就是没有读到boot0(spl)的头信息。

#56 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 15:29:40

#57 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 15:23:59

#58 Re: 全志 SOC » fc100s的spi闪存 » 2018-04-17 15:22:24

#59 全志 SOC » fc100s的spi闪存 » 2018-04-17 15:06:41

#60 全志 SOC » 3个坑 » 2018-04-17 14:46:59

- sunwei

- 回复: 2

1 前段时间在win下编译了xboot,因为手头没有fc100的板,于是在全志h2+芯片上测试

编译代码没有问题,并下载到了H2+上测试通过。

这次拿到fc100的板,然后编译fc100出2个错误,都是VFP对齐错误,

并且连编译器库里的库文件也显示链接VFP对齐错误。

没办法。返回去编译h2+,结果h2+也出现同样错误。

没办法。

重新把xboot代码和编译器eclipse-mars-for-arm-windows-x86_64 删掉。

重新按最开始通过的h2+的测试步骤走一遍。结果编译还是出现VFP对齐错误。

没办法。你说我的电脑还真牛逼,是把。

2 不玩xboot了,玩fc100 的教程

短接spi闪存 1-4脚

接入usb装驱动

执行fel ver

//显示版本

G:\xboot\xboot-master\output\tool>fel ver

Warning: no 'soc_sram_info' data for your SoC (id=1663)

AWUSBFEX soc=00001663(unknown) 00000001 ver=0001 44 08 scratchpad=00007e00 00000000 00000000

可以认到设备, 说明usb驱动没问题 ,我可用的时sunxi的官方fel 。

//下载boo0并执行

G:\xboot\xboot-master\output\tool>fel spl f1c100s.bin

Warning: no 'soc_sram_info' data for your SoC (id=1663)

Unexpected SCTLR (00052078)

看到了执行的错误

//读SRAM内存到文件

G:\xboot\xboot-master\output\tool>fel read 0x00010000 0x100 swsw.bin

swsw打开后全是0

//读ROM到文件

G:\xboot\xboot-master\output\tool>fel read 0x00000000 0x7fff sw.bin

sw 打开后全是有ROM的代码。

代码前面 0x0--0x3ff 全是0xff

代码后面 0x3ff -- 0x7fff 有一堆代码

由此可见这个f1c100s 的rom代码与其它全志的芯片有区别

因为在h2+上,不管是ddr,还是sram区域的内存,读取时都有代码在里面。

所以我估计,需要特殊的usb通讯协议。或是特殊的方法。

根据其它芯片的BROM程序判断这里没有头信息

还有个特别重要的事情说下。那个国产实时系统的开发环境。有个问题。

就是通过它的evn来做事的话要注意了。(其实完全可以不用那个evn)

只要打开evn,网络流量就有几M,不知道背景在跑什么东西。

所以你对安全有要求。就不要用。

最后啰嗦一句。用编译器的库,也要注意有没有后门。

所以对于小系统。尽量用自己的库。

3 ------------------- 最大的坑------------------------

当把spi闪存1-4脚连接后,连usb是可以进入FEL模式。

但是把1-4脚断开后,也还是在EFL模式。

不管是重新上电,还是重新连usb,都回不到正常的状态了。

估计闪存的程序丢了。

所以1-4脚不可靠。因为cS片选一直激活,闪存芯片很容易有误操作。

#61 全志 SOC » Melis平台编译环境安装配置说明.doc » 2018-04-13 02:05:17

- sunwei

- 回复: 12

文件说明:

1. Melis平台编译环境安装配置说明.doc 编译环境安装及使用说明;

2. cygwin.2.00.exe cygwin安装文件;

3. dram_DDRII_init_180M.axf DRAM初始化程序;

4. fel_pro.axf 烧码引导程序;

4. boot0.axf 启动引导程序;

使用说明:

1. 烧码:

step1: 板子上电,并reset;

step2: 通过AXD工具下载dram_DDRII_init_180M.axf,运行该程序进行DRAM初始化;

step3: 通过AXD工具下载fel_pro.axf,运行该程序引导烧码,注意此时需要打开Livesuit工具及连接USB;

step4: 等待烧码完成;

2. 启动:

step1: reset开发板;

step2: 通过AXD工具下载dram_DDRII_init_180M.axf,运行该程序进行DRAM初始化;

step3: 通过AXD工具下载boot0.axf,运行该程序引导系统启动;

#63 全志 SOC » DDR 设置 » 2018-04-13 01:23:34

#64 Re: 全志 SOC » spl 引导的编译脚本 » 2018-04-13 01:01:07

#65 全志 SOC » spl 引导的编译脚本 » 2018-04-13 00:59:42

- sunwei

- 回复: 2

#

# (C) Copyright 2000-2011

# Wolfgang Denk, DENX Software Engineering, wd@denx.de.

#

# (C) Copyright 2011

# Daniel Schwierzeck, daniel.schwierzeck@googlemail.com.

#

# (C) Copyright 2011

# Texas Instruments Incorporated - http://www.ti.com/

# Aneesh V <aneesh@ti.com>

#

# This file is released under the terms of GPL v2 and any later version.

# See the file COPYING in the root directory of the source tree for details.

#

# Based on top-level Makefile.

#

include $(SPLDIR)/config.mk

include $(TOPDIR)/include/autoconf.mk

include $(TOPDIR)/include/autoconf.mk.dep

CONFIG_SPL := y

export CONFIG_SPL

TOOLS_DIR := $(TOPDIR)/tools

#链接文件

BOOT0_LDSCRIPT := $(TOPDIR)/sunxi_spl/boot0/main/boot0.lds

# We want the final binaries in this directory

obj := $(OBJTREE)/sunxi_spl/boot0/

BOOT0_HEAD := sunxi_spl/boot0/boot0_head.o

START := sunxi_spl/boot0/boot0_entry.o

LIBS-y += sunxi_spl/boot0/spl/libsource_spl.o

LIBS-y += sunxi_spl/boot0/main/libmain.o

LIBS-y += sunxi_spl/boot0/libs/libgeneric.o

#看文件目录的make文件

LIBS-y += sunxi_spl/spl/lib/libgeneric.o

#目录---u-boot-2014.07\arch\arm\cpu\arm926ejs\sunivw1p1\dram-----------------

LIBS-y += arch/$(ARCH)/cpu/$(CPU)/$(SOC)/dram/libdram.o

LIBS-$(CONFIG_SUNXI_CHIPID) += arch/$(ARCH)/cpu/$(CPU)/$(SOC)/dram/libchipid.o

LIBS := $(addprefix $(OBJTREE)/,$(sort $(LIBS-y)))

#可以不要nand闪存的设备库

LIBNAND-$(CONFIG_STORAGE_MEDIA_NAND) += sunxi_spl/boot0/load_nand/libloadnand.o

LIBNAND-$(CONFIG_STORAGE_MEDIA_NAND) += arch/$(ARCH)/cpu/$(CPU)/$(SOC)/nand/libnand.o

LIBNAND := $(addprefix $(OBJTREE)/,$(sort $(LIBNAND-y)))

#可以不要SD卡闪存的设备库

LIBMMC-$(CONFIG_STORAGE_MEDIA_MMC) += sunxi_spl/boot0/load_mmc/libloadmmc.o

LIBMMC-$(CONFIG_STORAGE_MEDIA_MMC) += arch/$(ARCH)/cpu/$(CPU)/$(SOC)/mmc/libmmc.o

LIBMMC := $(addprefix $(OBJTREE)/,$(sort $(LIBMMC-y)))

#这个需要

LIBSPINOR-$(CONFIG_STORAGE_MEDIA_SPINOR) += sunxi_spl/boot0/load_spinor/libloadspinor.o

LIBSPINOR-$(CONFIG_STORAGE_MEDIA_SPINOR) += arch/$(ARCH)/cpu/$(CPU)/$(SOC)/spinor/libspinor.o

LIBSPINOR := $(addprefix $(OBJTREE)/,$(sort $(LIBSPINOR-y)))

__LIBS := $(subst $(obj),,$(LIBS))

# Special flags for CPP when processing the linker script.

# Pass the version down so we can handle backwards compatibility

# on the fly.

LDPPFLAGS += \

-include $(TOPDIR)/include/u-boot/u-boot.lds.h \

-DBOOT0ADDR=$(CONFIG_BOOT0_RUN_ADDR) \

$(shell $(LD) --version | \

sed -ne 's/GNU ld version \([0-9][0-9]*\)\.\([0-9][0-9]*\).*/-DLD_MAJOR=\1 -DLD_MINOR=\2/p')

ALL-$(CONFIG_STORAGE_MEDIA_NAND) += $(obj)boot0_nand.bin

ALL-$(CONFIG_STORAGE_MEDIA_MMC) += $(obj)boot0_sdcard.bin

ALL-$(CONFIG_STORAGE_MEDIA_SPINOR) += $(obj)boot0_spinor.bin

all: $(ALL-y)

$(obj)boot0_nand.bin: $(obj)boot0_nand.axf

@echo bootaddr is $(CONFIG_BOOT0_RUN_ADDR)

$(OBJCOPY) $(OBJCFLAGS) -O binary $< $@

$(obj)boot0_nand.axf: $(LIBS) $(LIBNAND) $(obj)boot0.lds

$(LD) $(LIBS) $(LIBNAND) $(PLATFORM_LIBGCC) $(LDFLAGS) -T$(obj)boot0.lds -o boot0_nand.axf -Map boot0_nand.map

$(obj)boot0_sdcard.bin: $(obj)boot0_sdcard.axf

$(OBJCOPY) $(OBJCFLAGS) -O binary $< $@

$(obj)boot0_sdcard.axf: $(LIBS) $(LIBMMC) $(obj)boot0.lds

$(LD) $(LIBS) $(LIBMMC) $(PLATFORM_LIBGCC) $(LDFLAGS) -T$(obj)boot0.lds -o boot0_sdcard.axf -Map boot0_sdcard.map

$(obj)boot0_spinor.bin: $(obj)boot0_spinor.axf

$(OBJCOPY) $(OBJCFLAGS) -O binary $< $@

$(obj)boot0_spinor.axf: $(LIBS) $(LIBSPINOR) $(obj)boot0.lds

$(LD) $(LIBS) $(LIBSPINOR) $(PLATFORM_LIBGCC) $(LDFLAGS) -T$(obj)boot0.lds -o boot0_spinor.axf -Map boot0_spinor.map

$(LIBS): depend

$(MAKE) -C $(SRCTREE)$(dir $(subst $(OBJTREE),,$@))

$(LIBNAND): depend

$(MAKE) -C $(SRCTREE)$(dir $(subst $(OBJTREE),,$@))

$(LIBMMC): depend

$(MAKE) -C $(SRCTREE)$(dir $(subst $(OBJTREE),,$@))

$(LIBSPINOR): depend

$(MAKE) -C $(SRCTREE)$(dir $(subst $(OBJTREE),,$@))

$(obj)boot0.lds: $(BOOT0_LDSCRIPT)

@$(CPP) $(ALL_CFLAGS) $(LDPPFLAGS) -ansi -D__ASSEMBLY__ -P - <$^ >$@

depend: .depend

#########################################################################

# defines $(obj).depend target

include $(SRCTREE)/rules.mk

sinclude .depend

#########################################################################

#70 Re: Nuvoton N32905/N32926/NUC972/N9H20/N9H26/N9H30 » 又多一个选择,紫芯内置8MB SDRAM 的ASM9128T » 2018-04-10 01:10:28

#71 全志 SOC » xboot 启动代码分析 » 2018-04-10 00:54:46

- sunwei

- 回复: 11

/*

* start.S

*

* Copyright(c) 2007-2018 Jianjun Jiang <8192542@qq.com>

* Official site: http://xboot.org

* Mobile phone: +86-18665388956

* QQ: 8192542

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the GNU General Public License as published by

* the Free Software Foundation; either version 2 of the License, or

* (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* You should have received a copy of the GNU General Public License

* along with this program; if not, write to the Free Software Foundation,

* Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA

*

*/

/*

* Exception vector table

*/

.text

.arm

.global _start

_start:

/* Boot head information for BROM */

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, 0x3a00

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0 /* 0x40 - boot params, 0x58 - fel boot type, 0x5c - dram size */

_vector:

b reset

ldr pc, _undefined_instruction

ldr pc, _software_interrupt

ldr pc, _prefetch_abort

ldr pc, _data_abort

ldr pc, _not_used

ldr pc, _irq

ldr pc, _fiq

_undefined_instruction:

.word undefined_instruction

_software_interrupt:

.word software_interrupt

_prefetch_abort:

.word prefetch_abort

_data_abort:

.word data_abort

_not_used:

.word not_used

_irq:

.word irq

_fiq:

.word fiq

/*

* The actual reset code

*/

reset:

/* Save boot params to 0x00000040 */

ldr r0, =0x00000040

str sp, [r0, #0] /* 0x00000040 = 保存堆栈*/

str lr, [r0, #4] /* 0x00000044 = 保存返回地址*/

mrs lr, cpsr /* 读 状态机*/

str lr, [r0, #8] /* 0x00000048 = 保存状态寄存器*/

mrc p15, 0, lr, c1, c0, 0 /* 读 MMU及相关的*/

str lr, [r0, #12] /* 0x0000004c = MMU及相关的*/

mrc p15, 0, lr, c1, c0, 0 /* 读 MMU及相关的*/

str lr, [r0, #16] /* 0x00000050 = MMU及相关的*/

/* Check boot type just for fel */

mov r0, #0x0

ldr r1, [r0, #8] /* R1 = 0x00000008地址内的数据*/

ldr r2, =0x4c45462e /* r2 = 0x4c45462e */

cmp r1, r2 /* 比较 r1 和 r2 */

bne 1f /* 不相等跳到 1f = 向后调到 1: */

ldr r1, =0x1 /* r1 = 0x01 */

str r1, [r0, #0x58] /* *(0x00000058) = 0x1 这里放的是启动是不是在FEL模式*/

/* 以上就是 比较0x00000008的内容与0x4c45462e 是不是想等 相等 跳过 ,不等 设置 0x00000058的内容为1

1: nop

/* Enter svc mode and mask interrupts */

mrs r0, cpsr /* 读状态寄存器 */

bic r0, r0, #0x1f /* r0 = r0 & (!0x0000001f) 清零处理器工作模式*/

orr r0, r0, #0xd3 /* r0 = r0 | 0x000000d3 设置处理器为系统模式,并关闭IRQ FIQ 中断*/

msr cpsr, r0 /* 写状态寄存器*/

/* Set vector to the low address */

mrc p15, 0, r0, c1, c0, 0

bic r0, #(1<<13) /* 设置异常向量地址为 0x0到0x1c */

mcr p15, 0, r0, c1, c0, 0

/* Copy vector to the correct address */

adr r0, _vector /*相对寻址到_vector,并把里面的内容读到r0,相对寻址的好处就是,可以做到代码与链接地址无关*/

mrc p15, 0, r2, c1, c0, 0 /* 读协处理器寄存器*/

ands r2, r2, #(1 << 13) /* 检查异常向量地址高端低端设置位 */

ldreq r1, =0x00000000 /* if((向量地址设置位) == 1) r1 = 0x00000000; */

ldrne r1, =0xffff0000 /* if((向量地址设置位) != 1) r1 = 0xffff0000; */

ldmia r0!, {r2-r8, r10}

stmia r1!, {r2-r8, r10} /* 将r2-r8,r10 放到 按顺序放到 r0 指向的地址; */

ldmia r0!, {r2-r8, r10}

stmia r1!, {r2-r8, r10}

/* 常向量地址高端低端设置位,从本代啊的位置拷贝向量到系统设置的向量地址*/

/* Initial system clock, ddr add uart */

bl sys_clock_init

bl sys_dram_init

bl sys_uart_init

/* Copyself to link address 自我复制到链接器编译后的绝对地址。 链接时是ddr的内存地址,要搞清楚这时执行的地址可能在0x0000,或是spi闪存的映射地址*/

adr r0, _start /* r0 = _start相对的地址 */

ldr r1, =_start /* r1 = _start绝对的地址 */

cmp r0, r1 /* 比较有没有跑过现代码 */

beq 1f /* 跑过向后调到 1:*/

bl sys_copyself

1: nop

/* Initialize stacks */

mrs r0, cpsr

bic r0, r0, #0x1f

orr r1, r0, #0x1b /*进入未定义异常*/

msr cpsr_cxsf, r1

ldr sp, _stack_und_end

bic r0, r0, #0x1f

orr r1, r0, #0x17 /*进入中止异常*/

msr cpsr_cxsf, r1

ldr sp, _stack_abt_end

bic r0, r0, #0x1f

orr r1, r0, #0x12 /*进入IRQ异常*/

msr cpsr_cxsf, r1

ldr sp, _stack_irq_end

bic r0, r0, #0x1f

orr r1, r0, #0x11 /*进入FIQ异常*/

msr cpsr_cxsf, r1

ldr sp, _stack_fiq_end

bic r0, r0, #0x1f

orr r1, r0, #0x13 /*进入管理异常*/

msr cpsr_cxsf, r1

ldr sp, _stack_srv_end

/* Copy data section */

ldr r0, _data_start /*目的地址*/

ldr r1, _data_shadow_start /*源地址 */

ldr r2, _data_shadow_end

sub r2, r2, r1 /*拷贝个数*/

bl memcpy /*memcpy(r0,r1,r2); 在keil 里这些是不需要做的*/

/* Clear bss section */

ldr r0, _bss_start

ldr r2, _bss_end

sub r2, r2, r0

mov r1, #0

bl memset /*memset(r0,r1,r2); 在keil 里这些是不需要做的*/

/* Call _main */

ldr r1, =_main

mov pc, r1

_main:

mov r0, #1;

mov r1, #0;

bl xboot_main

b _main

/ * 注意: 非常重要的情况,一定要搞清芯片内部的BROM程序是不是和你现在的启动代码及相关的代码相对应。

否则买到的是特制的BROM的芯片,将来会有很大的麻烦。

因为你需要咨询原厂要他提供特制BROM芯片的用法,再修改现在的代码。

但我估计芯片厂商是和客户签订了协议的,一般不会提供。*/

/* 补记忆

https://blog.csdn.net/gameit/article/details/13169405 协处理寄存器描述

https://www.cnblogs.com/armlinux/archive/2011/03/23/2396833.html 状态寄存器描述

CP15 的寄存器 C0:

MRC P15,0,R0,C0,C0,0 #将主标示符寄存器的内容读到AMR寄存器R0中

MRC P15,0,R0,C0,C0,1 #将cache类型标识符寄存器的内容读到AMR寄存器R0中

CP15 的寄存器 C1:

mrc p15, 0, r0, c1, c0{, 0} ;将 CP15 的寄存器 C1 的值读到r0中

mcr p15, 0, r0, c1, c0{, 0} ;将 r0 的值写到 CP15 的寄存器C1中

CP15 的寄存器 C2:

C2寄存器的别名:Translation table base (TTB) register

C2寄存器用来保存页表的基地址,即一级映射描述符表的基地址。其编码格如下所示:

CP15 的寄存器 C3:

CP15 中的寄存器 C3 定义了 ARM 处理器的 16 个域的访问权限。

CP15 的寄存器 C5:

CP15 中的寄存器 C5 是失效状态寄存器,分为指令状态失效和数据状态失效。

MRC p15, 0, <Rd>, c5, c0, 0 访问数据失效状态寄存器

MRC p15, 0, <Rd>, c5, c0, 1 访问指令状态失效寄存器

CP15的寄存器C6:

CP15 中的寄存器 C6 是失效地址寄存器,其中保存了引起存储访问失效的地址,分为数据失效地址寄存器和指令失效地址寄存器

MRC p15, 0, <Rd>, c6, c0, 0 访问数据失效地址寄存器

MRC p15, 0, <Rd>, c6, c0, 2 访问指令失效地址寄存器

CP15的寄存器C7:

CP15 的 C7 寄存器用来控制 cache 和写缓存,它是一个只写寄存器,读操作将产生不可预知的后果。

访问 CP15 的 C7 寄存器的指令格式如下所示:

mcr p15, 0, <rd>, <c7>, crm, <opcode_2> ;<rd> 、 <crm> 和 <opcode_2> 的不同取值组合,实现不同功能

CP15的寄存器C8:

系统协处理器CP15的寄存器C8就是清除TLB内容的相关操作。它是一个只写的寄存器。

MCR p15,0,Rd,c8,CRm,opcode_2

CP15的寄存器C12

CP15寄存器C12用来设置异常向量基地址,其编码格式如下所示:

MCR p15, 0, <Rd>, c12, c0, 0 ;Rd中存放要修改的异常向量基地址

CP15的寄存器C13

CP15中的寄存器C13用于快速上下文切换。其编码格式如下所示。

*/

/*

cpu 引导过程 当上电时 跑BROM的程序 会检测spi闪存内有没有符合规范的引导信息。 所以这里的_start小段常数里就放了这些信息

注意代码编译好了还需要 用mksunxi.exe将这个位置的某些地方修改一下保存到bin文件,再烧到闪存才有效。

如果再仔细研究一下fel.exe 的代码,里面很多小段小段的2进制代码,这些2进制的汇编源码在fel源代码码里也注释了。

这样就可以直接通过jatg调试器按规则下载那些小段小段的代码到芯片执行,之后直接下载自己的编译代码到内存运行。

就可以快速执行调试代码了,效率比烧闪存要快很多,并且我是想用keil,效率更高,因为可以直观的看断点后的所有寄存器和变量等。

关于怎么在keil下,编译后下载代码到内存,并执行代码,可参考asm9260t.ini 文件

(只要不烧本代码到闪存,新片就会进入FEL模式,并且usb也变成了下载程序的接口)

目前手上没f1c100的板子。在h2+的板子上测试了下xboot,但是先下载spl ,才能下载xboot执行,

并不是像填坑网讲的那样。直接下xboot,因为EFL模式下,会检测到xboot的代码超过了长度。

不知道f1c100是不是支持直接下xboot,还是说他的spi闪存里有spl的代码。

昨天看了填坑网的实验。原来是spi闪存里有spl引导程序 ,也就是原厂固件的前16k,有了这前16k,代码就不需要进入FEL模了,

芯片启动后会执行这里的代码。

我在思考一个问题。

1 对于不是定制的芯片,一定要在程序里做自己的加密和防止代码被复制的可能,当然在开源的代码下,没有必要,因为要遵循开源协议。

国产的系体没有这个限制,因为它的协议是,自己代码的部分可以不开源。

2 到底是定制spl ,还是定制BROM, 否则怎么区别世面上同类被仿照的产品。spl可以不需要芯片厂商的参与,自己解决,相对麻烦少很多。

但代码被复制的可能性很大。也可以通过软件的手段解决,但也会有麻烦事情。

3 很多通用的mcu, 其实都有这些所谓的BROM和SPL,只不过从来没有出现过。

导致他们认为自己的代码很安全。对于芯片厂商都是虚设。

如果某个芯片厂商人员外泄,一切都变得不安全。

只要开网络你们就把我的鼠标搞到不能正常。我靠

1 GM8136s 25的价格不能接受。 2功耗 3 keil 不支持arm v6, 快捷的调试很重要。

*/

.global return_to_fel

return_to_fel:

mov r0, #0x4

mov r1, #'e'

strb r1, [r0, #0]

mov r1, #'G'

strb r1, [r0, #1]

mov r1, #'O'

strb r1, [r0, #2]

mov r1, #'N'

strb r1, [r0, #3]

mov r1, #'.'

strb r1, [r0, #4]

mov r1, #'F'

strb r1, [r0, #5]

mov r1, #'E'

strb r1, [r0, #6]

mov r1, #'L'

strb r1, [r0, #7]

ldr r0, =0x00000040

ldr sp, [r0, #0]

ldr lr, [r0, #4]

ldr r1, [r0, #16]

mcr p15, 0, r1, c1, c0, 0

ldr r1, [r0, #12]

mcr p15, 0, r1, c1, c0, 0

ldr r1, [r0, #8]

msr cpsr, r1

bx lr

/* 将BROM程序 进入本复位代码时保存的现场及相关又恢复,并返回到BROM程序 */

/*

* Exception handlers 下面的需要修改到系统需要的。

* 一般系统会提供一些函数给异常调用,还有保存现场和恢复现场的代码。 这样看xboot,还离做系统很远。

*/

.align 5

undefined_instruction:

b .

.align 5

software_interrupt:

b .

.align 5

prefetch_abort:

b .

.align 5

data_abort:

b .

.align 5

not_used:

b .

.align 5

irq:

ldr sp, _stack_irq_end

sub sp, sp, #72

stmia sp, {r0 - r12}

add r8, sp, #60

stmdb r8, {sp, lr}^

str lr, [r8, #0]

mrs r6, spsr

str r6, [r8, #4]

str r0, [r8, #8]

mov r0, sp

bl arm32_do_irq

ldmia sp, {r0 - lr}^

mov r0, r0

ldr lr, [sp, #60]

add sp, sp, #72

subs pc, lr, #4

.align 5

fiq:

ldr sp, _stack_irq_end

sub sp, sp, #72

stmia sp, {r0 - r12}

add r8, sp, #60

stmdb r8, {sp, lr}^

str lr, [r8, #0]

mrs r6, spsr

str r6, [r8, #4]

str r0, [r8, #8]

mov r0, sp

bl arm32_do_fiq

ldmia sp, {r0 - lr}^

mov r0, r0

ldr lr, [sp, #60]

add sp, sp, #72

subs pc, lr, #4

/*

* The location of section

*/

.align 4

_image_start:

.long __image_start

_image_end:

.long __image_end

_data_shadow_start:

.long __data_shadow_start

_data_shadow_end:

.long __data_shadow_end

_data_start:

.long __data_start

_data_end:

.long __data_end

_bss_start:

.long __bss_start

_bss_end:

.long __bss_end

_stack_und_end:

.long __stack_und_end

_stack_abt_end:

.long __stack_abt_end

_stack_irq_end:

.long __stack_irq_end

_stack_fiq_end:

.long __stack_fiq_end

_stack_srv_end:

.long __stack_srv_end

页次: 1

- 首页

- » 搜索

- » sunwei 发表的帖子