楼主 #1 2018-08-02 15:58:00 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

F1C100S裸奔framebuffer+PWM+GPIO驱动

最近把xboot的几个驱动剥离了出来,特别是framebuffer,终于可以单独使用了

#if TEST_GPIO

gpio_f1c100s_set_dir(&GPIO_PE, 2, GPIO_DIRECTION_OUTPUT);

while(1)

{

gpio_f1c100s_set_value(&GPIO_PE, 2, 0);

gpio_f1c100s_set_value(&GPIO_PE, 2, 1);

}

#endif

#if TEST_FB

{

framebuffer_t fb_f1c100s;

fb_f1c100s_init(&fb_f1c100s);

render_t* render = fb_f1c100s_create(&fb_f1c100s);

for (int i = 0; i < render->pixlen/4;i++)

{

((uint32_t*)render->pixels)[i] = 0xFFFF0000;

}

fb_f1c100s_present(&fb_f1c100s, render);

fb_f1c100s_setbl(&fb_f1c100s, 100);

}

#endif

#if TEST_PWM

pwm_t led_pwm_bl =

{

.virt = 0x01c21000,

.duty = 50,

.period = 1000000,

.channel = 1,

.polarity = true,

.pwm_port = &GPIO_PE,

.pwm_pin = 6,

.pwm_pin_cfg = 3,

};

pwm_f1c100s_init(&led_pwm_bl);

#endif编译:make

烧flash:make write

离线

楼主 #3 2018-08-02 18:25:54 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

要感谢xboot的原代码驱动!话说xboot是GNU license,以它的基础改的代码也应该开源。

另外xboot或者基于xboot改的代码能直接跑商业项目吗?按理得全部开源吧

离线

楼主 #7 2018-08-19 00:04:32 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

framebuffer驱动我还是花了几个晚上功夫的,为了不用xboot的dts还有driver架构,把reset,clock等好几个模块都改了一遍。如果再来一遍V3S的话,应该容易很多,因为两芯片同出一源代码很类似。

不过不打算继续自己搞裸奔了,可重用性太低,累死人。准备直接用xboot或者RTOS这样的平台来开发后续产品,开发驱动有标准,代码容易复用,功能也更强大。比如说切换V3S和F1C100S对xboot来说非常简单,上层完全不用改

目前我把xboot优化到1.3MB大小(带文件系统和图形库),启动到logo只需要0.85s(F1C100S),基本满足需要。V3S没测,上电应该更快。如果V3S和F1C100S支持QSPI就完美了。。。

离线

楼主 #10 2018-08-19 22:15:48 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

感觉你这个编译器不对,我是用xboot指定的5.3.1版

http://pan.baidu.com/s/1dDtssIt

离线

楼主 #11 2018-08-19 22:16:57 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

arm9没有hf的

离线

楼主 #16 2018-08-19 22:54:06 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

mksunxi tool编了吗?

最后几行应该会显示brom been fixed字样,Bootloader size=xxxx

离线

楼主 #19 2018-08-19 23:27:17 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

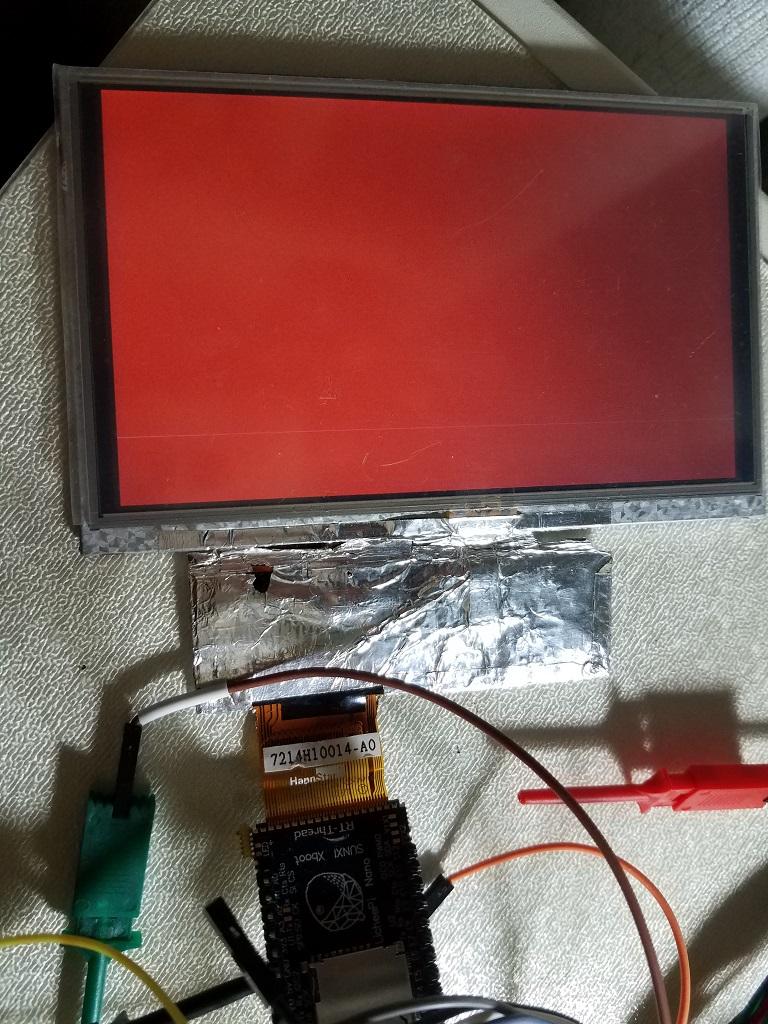

终于搞定,谢谢达哥, 红红的LCD亮起来了.

问下你屏幕有条白线吗?我的有条白线,不知道是代码还有问题还是屏幕硬件有问题了

离线

楼主 #22 2018-08-21 11:45:04 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

https://whycan.cn/files/members/713/QQ20180821092612.jpg

就是这样的,看起来也挺正常, 800x480

下面怎么显示蓝色的?

离线

楼主 #25 2018-08-23 17:57:16 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

:mad哈哈哈,多亏晕哥发现,太惭愧了,每次只要手填一堆数,总要出错。

离线

楼主 #33 2018-08-31 12:19:11 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

编译器差别这么大呀。。。

我都想用llvm了,公司用的就是llvm

离线

楼主 #41 2018-09-30 20:52:14 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

晕哥 说:Gardenia 说:嗯,看到了,xboot启动时间比较慢,如果要做到1秒以内启动,晕哥有没试过?有可行性不?

主要耗时在于spl(boot0)从spi 拷贝 xboot(boot1) 到DRAM,

想办法精简 xboot, 或者分时加载 xboot, 比如再弄个boot2, 系统boot1启动后再加载boot2.好的,谢谢,我试试看。

我做到800ms,主要是把romdisk裁剪了一点,把log关掉,不用的函数关掉,autoboot的一秒等待关掉,基本就差不多了。不要用压缩

离线

楼主 #47 2018-10-01 11:57:31 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

达克罗德 说:framebuffer驱动我还是花了几个晚上功夫的,为了不用xboot的dts还有driver架构,把reset,clock等好几个模块都改了一遍。如果再来一遍V3S的话,应该容易很多,因为两芯片同出一源代码很类似。

不过不打算继续自己搞裸奔了,可重用性太低,累死人。准备直接用xboot或者RTOS这样的平台来开发后续产品,开发驱动有标准,代码容易复用,功能也更强大。比如说切换V3S和F1C100S对xboot来说非常简单,上层完全不用改

目前我把xboot优化到1.3MB大小(带文件系统和图形库),启动到logo只需要0.85s(F1C100S),基本满足需要。V3S没测,上电应该更快。如果V3S和F1C100S支持QSPI就完美了。。。

:lol:现在才看到,原来你已搞定,能分享下代码吗?我信息里面有我邮箱

我也想试试能不能启动之后能不能先初始化spi,提高下spi访问速度,之后spi拷贝速度会高点,没有qspi确实硬伤啊

在老家,只能回去之后整理给你。

我试过把spi速度提高到100mhz,还有优化底层读fifo的代码,提升非常有限

800ms其中有400ms是全志内部boot代码读spl和启动的时间,这时候spi速度只有3mhz,这还没法改,没办法这是全志写死了。所以优化空间也不多了

离线

楼主 #53 2018-10-10 11:02:52 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

楼主休完假了吧?我这边也是需要图形的,方便发我邮箱吗?4201842@qq.com

我试了一下发现我的改动太分散,而且xboot和我另外一个框架绑在一起,不好给你,我还是给你说下几个改动吧

1. skip compress [sys-copyself.c]

+#if CONFIG_LZ_COMPRESS

sys_spi_flash_init();

sys_spi_flash_read(16384, &z, sizeof(struct zdesc_t));

sys_spi_flash_exit();

...

sys_decompress(tmp, ssize, mem, dsize);

}

else

+#endif

2. Disable logs [arch/arm32/mach-f1c100s/include/configs.h]

+#define CONFIG_NO_LOG (1)

3. 优化了SPI读写

/*

* sys-spi-flash.c

*

* Copyright(c) 2007-2018 Jianjun Jiang <8192542@qq.com>

* Official site: http://xboot.org

* Mobile phone: +86-18665388956

* QQ: 8192542

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the GNU General Public License as published by

* the Free Software Foundation; either version 2 of the License, or

* (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* You should have received a copy of the GNU General Public License

* along with this program; if not, write to the Free Software Foundation,

* Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA

*

*/

#include <xboot.h>

enum {

SPI_GCR = 0x04,

SPI_TCR = 0x08,

SPI_IER = 0x10,

SPI_ISR = 0x14,

SPI_FCR = 0x18,

SPI_FSR = 0x1c,

SPI_WCR = 0x20,

SPI_CCR = 0x24,

SPI_MBC = 0x30,

SPI_MTC = 0x34,

SPI_BCC = 0x38,

SPI_TXD = 0x200,

SPI_RXD = 0x300,

};

void sys_spi_flash_init(void)

{

virtual_addr_t addr;

u32_t val;

/* Config GPIOC0, GPIOC1, GPIOC2 and GPIOC3 */

addr = 0x01c20848 + 0x00;

val = read32(addr);

val &= ~(0xf << ((0 & 0x7) << 2));

val |= ((0x2 & 0x7) << ((0 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((1 & 0x7) << 2));

val |= ((0x2 & 0x7) << ((1 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((2 & 0x7) << 2));

val |= ((0x2 & 0x7) << ((2 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((3 & 0x7) << 2));

val |= ((0x2 & 0x7) << ((3 & 0x7) << 2));

write32(addr, val);

/* Deassert spi0 reset */

addr = 0x01c202c0;

val = read32(addr);

val |= (1 << 20);

write32(addr, val);

/* Open the spi0 bus gate */

addr = 0x01c20000 + 0x60;

val = read32(addr);

val |= (1 << 20);

write32(addr, val);

/* Set spi clock rate control register, divided by 4 */

addr = 0x01c05000;

write32(addr + SPI_CCR, 0x00001000);

/* Enable spi0 and do a soft reset */

addr = 0x01c05000;

val = read32(addr + SPI_GCR);

val |= (1 << 31) | (1 << 7) | (1 << 1) | (1 << 0);

write32(addr + SPI_GCR, val);

while(read32(addr + SPI_GCR) & (1 << 31));

val = read32(addr + SPI_TCR);

val &= ~(0x3 << 0);

val |= (1 << 6) | (1 << 2);

write32(addr + SPI_TCR, val);

val = read32(addr + SPI_FCR);

val |= (1 << 31) | (1 << 15);

write32(addr + SPI_FCR, val);

}

void sys_spi_flash_exit(void)

{

virtual_addr_t addr = 0x01c05000;

u32_t val;

/* Disable the spi0 controller */

val = read32(addr + SPI_GCR);

val &= ~((1 << 1) | (1 << 0));

write32(addr + SPI_GCR, val);

}

static void sys_spi_select(void)

{

virtual_addr_t addr = 0x01c05000;

u32_t val;

val = read32(addr + SPI_TCR);

val &= ~((0x3 << 4) | (0x1 << 7));

val |= ((0 & 0x3) << 4) | (0x0 << 7);

write32(addr + SPI_TCR, val);

}

static void sys_spi_deselect(void)

{

virtual_addr_t addr = 0x01c05000;

u32_t val;

val = read32(addr + SPI_TCR);

val &= ~((0x3 << 4) | (0x1 << 7));

val |= ((0 & 0x3) << 4) | (0x1 << 7);

write32(addr + SPI_TCR, val);

}

#define SPI0_BASE (0x01c05000)

static inline void sys_spi_write_txbuf(u8_t * buf, int len)

{

// virtual_addr_t addr = 0x01c05000;

int i;

if(!buf)

len = 0;

write32(SPI0_BASE + SPI_MTC, len & 0xffffff);

write32(SPI0_BASE + SPI_BCC, len & 0xffffff);

for(i = 0; i < len; ++i)

write8(SPI0_BASE + SPI_TXD, *buf++);

}

static int sys_spi_transfer(void * txbuf, void * rxbuf, int len)

{

// virtual_addr_t addr = 0x01c05000;

int count = len;

u8_t * tx = txbuf;

u8_t * rx = rxbuf;

u8_t val;

int n, i;

while(count > 0)

{

n = (count <= 64) ? count : 64;

write32(SPI0_BASE + SPI_MBC, n);

sys_spi_write_txbuf(tx, n);

write32(SPI0_BASE + SPI_TCR, read32(SPI0_BASE + SPI_TCR) | (1 << 31));

// while((read32(SPI0_BASE + SPI_FSR) & 0xff) < n);

for(i = 0; i < n; i++)

{

while((read32(SPI0_BASE + SPI_FSR) & 0xff) == 0);

val = read8(SPI0_BASE + SPI_RXD);

if(rx)

*rx++ = val;

}

if(tx)

tx += n;

count -= n;

}

return len;

}

static int sys_spi_write_then_read(void * txbuf, int txlen, void * rxbuf, int rxlen)

{

if(sys_spi_transfer(txbuf, NULL, txlen) != txlen)

return -1;

if(sys_spi_transfer(NULL, rxbuf, rxlen) != rxlen)

return -1;

return 0;

}

void sys_spi_flash_read(int addr, void * buf, int count)

{

u8_t tx[4];

tx[0] = 0x03;

tx[1] = (u8_t)(addr >> 16);

tx[2] = (u8_t)(addr >> 8);

tx[3] = (u8_t)(addr >> 0);

sys_spi_select();

sys_spi_write_then_read(tx, 4, buf, count);

sys_spi_deselect();

}4. Remove shells and Lua frameworks

+#if XBOOT_SHELL_ENABLE

/* Do auto boot */

Add a comment to this line

do_autoboot();

//run_shell();

system("/application/examples");

}

+#else

+ while(1);

+#endifmake file remove these lines:

- framework \

- framework/base64 \

- framework/display \

- framework/event \

- framework/hardware \

- framework/lang \

- framework/stopwatch \-INCDIRS += xboot/src/external/lua-5.3.4

-SRCDIRS += xboot/src/external/lua-5.3.4

-INCDIRS += xboot/src/external/lua-cjson-2.1.0

-SRCDIRS += xboot/src/external/lua-cjson-2.1.0再把romdisk删掉一些,我只留了ttf文件

5. 参照xboot最新版,加上编译选项 —ffunction-sections和—gc-sections [这个一定要做,能省1.xMB]

6. SPI升到100MHz [arch/arm32/mach-f1c100s/sys-spi-flash.c]

- write32(addr + SPI_CCR, 0x00001001);

+ write32(addr + SPI_CCR, 0x00001000);

7. CPU生到最高频率720Mhz [arch/arm32/mach-f1c100s/sys-clock.c]

- clock_set_pll_cpu(408000000);

+ clock_set_pll_cpu(800000000);

离线

楼主 #56 2018-10-10 22:31:52 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

达克罗德 说:Gardenia 说:楼主休完假了吧?我这边也是需要图形的,方便发我邮箱吗?4201842@qq.com

我试了一下发现我的改动太分散,而且xboot和我另外一个框架绑在一起,不好给你,我还是给你说下几个改动吧

1. skip compress [sys-copyself.c]+#if CONFIG_LZ_COMPRESS

sys_spi_flash_init();

sys_spi_flash_read(16384, &z, sizeof(struct zdesc_t));

sys_spi_flash_exit();

...

sys_decompress(tmp, ssize, mem, dsize);

}

else

+#endif2. Disable logs [arch/arm32/mach-f1c100s/include/configs.h]

+#define CONFIG_NO_LOG (1)

3. 优化了SPI读写

/* * sys-spi-flash.c * * Copyright(c) 2007-2018 Jianjun Jiang <8192542@qq.com> * Official site: http://xboot.org * Mobile phone: +86-18665388956 * QQ: 8192542 * * This program is free software; you can redistribute it and/or modify * it under the terms of the GNU General Public License as published by * the Free Software Foundation; either version 2 of the License, or * (at your option) any later version. * * This program is distributed in the hope that it will be useful, * but WITHOUT ANY WARRANTY; without even the implied warranty of * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the * GNU General Public License for more details. * * You should have received a copy of the GNU General Public License * along with this program; if not, write to the Free Software Foundation, * Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA * */ #include <xboot.h> enum { SPI_GCR = 0x04, SPI_TCR = 0x08, SPI_IER = 0x10, SPI_ISR = 0x14, SPI_FCR = 0x18, SPI_FSR = 0x1c, SPI_WCR = 0x20, SPI_CCR = 0x24, SPI_MBC = 0x30, SPI_MTC = 0x34, SPI_BCC = 0x38, SPI_TXD = 0x200, SPI_RXD = 0x300, }; void sys_spi_flash_init(void) { virtual_addr_t addr; u32_t val; /* Config GPIOC0, GPIOC1, GPIOC2 and GPIOC3 */ addr = 0x01c20848 + 0x00; val = read32(addr); val &= ~(0xf << ((0 & 0x7) << 2)); val |= ((0x2 & 0x7) << ((0 & 0x7) << 2)); write32(addr, val); val = read32(addr); val &= ~(0xf << ((1 & 0x7) << 2)); val |= ((0x2 & 0x7) << ((1 & 0x7) << 2)); write32(addr, val); val = read32(addr); val &= ~(0xf << ((2 & 0x7) << 2)); val |= ((0x2 & 0x7) << ((2 & 0x7) << 2)); write32(addr, val); val = read32(addr); val &= ~(0xf << ((3 & 0x7) << 2)); val |= ((0x2 & 0x7) << ((3 & 0x7) << 2)); write32(addr, val); /* Deassert spi0 reset */ addr = 0x01c202c0; val = read32(addr); val |= (1 << 20); write32(addr, val); /* Open the spi0 bus gate */ addr = 0x01c20000 + 0x60; val = read32(addr); val |= (1 << 20); write32(addr, val); /* Set spi clock rate control register, divided by 4 */ addr = 0x01c05000; write32(addr + SPI_CCR, 0x00001000); /* Enable spi0 and do a soft reset */ addr = 0x01c05000; val = read32(addr + SPI_GCR); val |= (1 << 31) | (1 << 7) | (1 << 1) | (1 << 0); write32(addr + SPI_GCR, val); while(read32(addr + SPI_GCR) & (1 << 31)); val = read32(addr + SPI_TCR); val &= ~(0x3 << 0); val |= (1 << 6) | (1 << 2); write32(addr + SPI_TCR, val); val = read32(addr + SPI_FCR); val |= (1 << 31) | (1 << 15); write32(addr + SPI_FCR, val); } void sys_spi_flash_exit(void) { virtual_addr_t addr = 0x01c05000; u32_t val; /* Disable the spi0 controller */ val = read32(addr + SPI_GCR); val &= ~((1 << 1) | (1 << 0)); write32(addr + SPI_GCR, val); } static void sys_spi_select(void) { virtual_addr_t addr = 0x01c05000; u32_t val; val = read32(addr + SPI_TCR); val &= ~((0x3 << 4) | (0x1 << 7)); val |= ((0 & 0x3) << 4) | (0x0 << 7); write32(addr + SPI_TCR, val); } static void sys_spi_deselect(void) { virtual_addr_t addr = 0x01c05000; u32_t val; val = read32(addr + SPI_TCR); val &= ~((0x3 << 4) | (0x1 << 7)); val |= ((0 & 0x3) << 4) | (0x1 << 7); write32(addr + SPI_TCR, val); } #define SPI0_BASE (0x01c05000) static inline void sys_spi_write_txbuf(u8_t * buf, int len) { // virtual_addr_t addr = 0x01c05000; int i; if(!buf) len = 0; write32(SPI0_BASE + SPI_MTC, len & 0xffffff); write32(SPI0_BASE + SPI_BCC, len & 0xffffff); for(i = 0; i < len; ++i) write8(SPI0_BASE + SPI_TXD, *buf++); } static int sys_spi_transfer(void * txbuf, void * rxbuf, int len) { // virtual_addr_t addr = 0x01c05000; int count = len; u8_t * tx = txbuf; u8_t * rx = rxbuf; u8_t val; int n, i; while(count > 0) { n = (count <= 64) ? count : 64; write32(SPI0_BASE + SPI_MBC, n); sys_spi_write_txbuf(tx, n); write32(SPI0_BASE + SPI_TCR, read32(SPI0_BASE + SPI_TCR) | (1 << 31)); // while((read32(SPI0_BASE + SPI_FSR) & 0xff) < n); for(i = 0; i < n; i++) { while((read32(SPI0_BASE + SPI_FSR) & 0xff) == 0); val = read8(SPI0_BASE + SPI_RXD); if(rx) *rx++ = val; } if(tx) tx += n; count -= n; } return len; } static int sys_spi_write_then_read(void * txbuf, int txlen, void * rxbuf, int rxlen) { if(sys_spi_transfer(txbuf, NULL, txlen) != txlen) return -1; if(sys_spi_transfer(NULL, rxbuf, rxlen) != rxlen) return -1; return 0; } void sys_spi_flash_read(int addr, void * buf, int count) { u8_t tx[4]; tx[0] = 0x03; tx[1] = (u8_t)(addr >> 16); tx[2] = (u8_t)(addr >> 8); tx[3] = (u8_t)(addr >> 0); sys_spi_select(); sys_spi_write_then_read(tx, 4, buf, count); sys_spi_deselect(); }4. Remove shells and Lua frameworks

+#if XBOOT_SHELL_ENABLE

/* Do auto boot */

Add a comment to this line

do_autoboot();

//run_shell();

system("/application/examples");

}

+#else

+ while(1);

+#endifmake file remove these lines:

- framework \

- framework/base64 \

- framework/display \

- framework/event \

- framework/hardware \

- framework/lang \

- framework/stopwatch \-INCDIRS += xboot/src/external/lua-5.3.4

-SRCDIRS += xboot/src/external/lua-5.3.4

-INCDIRS += xboot/src/external/lua-cjson-2.1.0

-SRCDIRS += xboot/src/external/lua-cjson-2.1.0再把romdisk删掉一些,我只留了ttf文件

5. 参照xboot最新版,加上编译选项 —ffunction-sections和—gc-sections [这个一定要做,能省1.xMB]

6. SPI升到100MHz [arch/arm32/mach-f1c100s/sys-spi-flash.c]

- write32(addr + SPI_CCR, 0x00001001);

+ write32(addr + SPI_CCR, 0x00001000);7. CPU生到最高频率720Mhz [arch/arm32/mach-f1c100s/sys-clock.c]

- clock_set_pll_cpu(408000000);

+ clock_set_pll_cpu(800000000);这两天把spi驱动搞了下,dual模式+提高spi速度,都没有很明显速度提升,有点奇怪,有个问题请教下,在刚启动的时候sys_copyself()是在flash里面运行的还是dram,在调用前没看到相关函数的拷贝过程,如果是在flash里面运行的,这里执行效率就相当低了。

全志的brom程序启动时自动从spi nor拷贝最前面的几k代码到内部SRAM后执行的。后来因为SRAM太慢,xboot老大又改成再一次拷贝到dram后再从dram执行copyself,把整个image拷贝到DRAM

离线

楼主 #64 2018-11-18 08:58:03 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

请教,楼主位的framebuffer,有没有画点函数?

framebuffer都有了,画点就是把rgba写到对应行列的那个32位数

离线

楼主 #66 2018-11-18 16:05:46 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

达克罗德 说:Pese 说:请教,楼主位的framebuffer,有没有画点函数?

framebuffer都有了,画点就是把rgba写到对应行列的那个32位数

这样?下载麻烦未测试

void point(x,y,color){

((uint32_t *)render->pixels)[x+800*y] = color;

fb_f1c100s_present(&fb_f1c100s, render);

}

不过裸机真的麻烦,使用了标准库,makefile加-lc -lm -lnosys编译,就报错,外设驱动又不全,玩不来啊

In function `_sbrk':

sbrk.c:(.text._sbrk+0x28): undefined reference to `end'

collect2.exe: error: ld returned 1 exit status

噢gcc是gcc version 7.3.1 20180622 (release) [ARM/embedded-7-branch revision 261907] (GNU Tools for Arm Embedded Processors 7-2018-q2-update)

present是把全屏都更新。你不要每画一个点都更新全屏,而是全部画完才调present

离线

楼主 #68 2018-11-19 12:47:54 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

达克罗德 说:Pese 说:这样?下载麻烦未测试

void point(x,y,color){

((uint32_t *)render->pixels)[x+800*y] = color;

fb_f1c100s_present(&fb_f1c100s, render);

}

不过裸机真的麻烦,使用了标准库,makefile加-lc -lm -lnosys编译,就报错,外设驱动又不全,玩不来啊

In function `_sbrk':

sbrk.c:(.text._sbrk+0x28): undefined reference to `end'

collect2.exe: error: ld returned 1 exit status

噢gcc是gcc version 7.3.1 20180622 (release) [ARM/embedded-7-branch revision 261907] (GNU Tools for Arm Embedded Processors 7-2018-q2-update)present是把全屏都更新。你不要每画一个点都更新全屏,而是全部画完才调present

折腾一下,还是不行,不知道为什么,这是什么原因?

代码和显示如下(按代码应该是有一条绿线的)

https://whycan.cn/files/members/377/1.png

https://whycan.cn/files/members/377/3.jpg

很奇怪,你全屏画蓝色都可以,没理由画一行不行呀。晕哥发现的我在驱动把480写成400这个问题你改了吗?

离线

楼主 #70 2018-11-21 01:16:56 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

改了,所以看到的是全屏蓝色的,奇怪的是全屏刷一个颜色就可以,可这样画线或画一个矩形,就不行,你有空试试上面画线的代码看看!!

原来是我的Bug,defe和debe的divider没有设对。PLL时钟要用f1c100s_tcon_clk_get_rate()来获取,主要是改动一下两个地方:

static void f1c100s_clk_defe_init(void)

{

clk_mux_set_parent(0x01c2010c, 3, 24, 0);

clk_divider_set_rate(0x01c2010c, 4, 0, true, f1c100s_tcon_clk_get_rate(), 198000000);

}

static void f1c100s_clk_debe_init(void)

{

clk_mux_set_parent(0x01c20104, 3, 24, 0);

clk_divider_set_rate(0x01c20104, 4, 0, true, f1c100s_tcon_clk_get_rate(), 198000000);

}main

framebuffer_t fb_f1c100s;

fb_f1c100s_init(&fb_f1c100s);

render_t* render = fb_f1c100s_create(&fb_f1c100s);

for (int i = 0; i < render->pixlen/4;i++)

{

((uint32_t*)render->pixels)[i] = 0xFF0000FF;

}

fb_f1c100s_present(&fb_f1c100s, render);

for (int i = 0; i < 800;i++)

{

((uint32_t*)render->pixels)[i+80000] = 0xFF00FF00;

}

fb_f1c100s_present(&fb_f1c100s, render);

fb_f1c100s_setbl(&fb_f1c100s, 100);

离线

楼主 #84 2018-12-11 20:31:04 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

大侠,我编译的时候出现mksunxi无法编译,还请问大概是什么情况。

我已经使用root用户来编译了,还提示没有权限。

https://whycan.cn/files/members/1297/minimal_f1c100s.jpg

没遇到过,你试试把sunxitool的可执行文件用chmod 777处理下

离线

楼主 #97 2019-01-30 19:02:33 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

那是几个显示相关模块的内部复位管,和时序没什么关系

离线

楼主 #99 2019-02-03 08:15:57 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

你好,达克罗德

我在修改液framebuffer初始化函数的时候,void fb_f1c100s_init(framebuffer_t * fb)函数中,只要修改了频率参数, 您的代码中 原来pdat->timing.pixel_clock_hz = 33000000 ,只要这个参数一旦修改后,不管是变大还是变小。 F1C100S的LCD_CLK硬件引脚就没有信号输出了。

我尝试了下,查询液晶初始化的其他函数,实在没有发现问题所在。

请问下达克罗德,您的代码从XBOOT中移植出来,是否需要修改什么地方,才可以 实现其他分辨率的刷屏频率。

71楼的修改你改了吗

我最近要支持1024x600,成功了我发出来

离线

楼主 #101 2019-02-10 02:01:11 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

你好,达克罗德。

我的工程替换了71楼的 “完整FB-f1c100s.c文件”,编译成功后,修改pdat->timing.pixel_clock_hz ,情况是一样的,LCD_CLK硬件引脚就没有信号输出。

启动时PLL_VIDEO时钟只有198MHZ,而全志要求和pixel时钟的倍数必须大于等于4,实际我发现大于等于6才行。所以33Mhz以上TCON时钟工作不正常

需要把PLL video时钟设高一点

把sys_clock.c中

write32(F1C100S_CCU_BASE + CCU_PLL_VIDEO_CTRL, 0x81004107);时钟输出=24000000*(0x41+1)/(0x07+1)=198Mhz

改为

write32(F1C100S_CCU_BASE + CCU_PLL_VIDEO_CTRL, 0x81004103);时钟输出=24000000*(0x41+1)/(0x03+1)=396Mhz

这时候pixel_clock_hz能设置成更高时钟了

离线

楼主 #104 2019-03-04 19:35:14 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

达克罗德 说:0752ben 说:你好,达克罗德。

我的工程替换了71楼的 “完整FB-f1c100s.c文件”,编译成功后,修改pdat->timing.pixel_clock_hz ,情况是一样的,LCD_CLK硬件引脚就没有信号输出。启动时PLL_VIDEO时钟只有198MHZ,而全志要求和pixel时钟的倍数必须大于等于4,实际我发现大于等于6才行。所以33Mhz以上TCON时钟工作不正常

需要把PLL video时钟设高一点

把sys_clock.c中write32(F1C100S_CCU_BASE + CCU_PLL_VIDEO_CTRL, 0x81004107);时钟输出=24000000*(0x41+1)/(0x07+1)=198Mhz

改为write32(F1C100S_CCU_BASE + CCU_PLL_VIDEO_CTRL, 0x81004103);时钟输出=24000000*(0x41+1)/(0x03+1)=396Mhz

这时候pixel_clock_hz能设置成更高时钟了

你好,达克罗德,我还是没能调通1280*720分辨率输出。上个月忙起来,就没有时间研究了。请问您接付费外包吗?我的联系方式邮箱 243280383@qq.com

不好意思,实在没有时间,我只是业余玩玩,研究也很浅

离线

楼主 #109 2019-06-14 17:48:48 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

你把最终要的头信息都丢了

.global _start

_start:

/* Boot head information for BROM */

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, 0x2000

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0 /* 0x28 - boot type */

.long 0, 0, 0, 0, 0, 0, 0, 0 /* 0x40 - boot params, 0x5c - dram size */

而且ld文件里

.obj/source/start.o (.text)一定要放到最开始

最后还要用tools下面mksunxi对头信息处理一下

离线

楼主 #111 2019-06-14 18:35:39 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

达克罗德 说:你把最终要的头信息都丢了

.global _start

_start:

/* Boot head information for BROM */

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, 0x2000

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0 /* 0x28 - boot type */

.long 0, 0, 0, 0, 0, 0, 0, 0 /* 0x40 - boot params, 0x5c - dram size */

而且ld文件里

.obj/source/start.o (.text)一定要放到最开始最后还要用tools下面mksunxi对头信息处理一下

这么说 中断向量不放到0了? 中断向量首地址是不是要重新在cp15配置了

只是编译的时候放到文件的头,这样就放到flash的头,启动之后,ram或dram内容都是自己控制了。这个spl也就没用了

离线

楼主 #113 2019-06-14 22:06:24 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

brom应该不拷贝这个头,我记得这个头会填上跳转地址的,所以brom知道怎么跳

离线

楼主 #124 2019-07-31 20:20:25 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

不可能这么高分辨率,内存带宽还有CPU主频限制了

离线

楼主 #143 2019-10-31 18:03:14 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

@达克罗德 你好,这个裸机工程能放到eclipse里编译吗?是否可以用eclipse来代替@晕哥的IAR demo来单步调试呢?因为IAR jilink调试需要先烧录xboot,我现在想做的是能直接进行裸机单步并且能点亮屏幕。

eclipse编译肯定可以。调试我不懂。现在基本就靠打印来调试

离线

楼主 #145 2019-11-01 08:16:01 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

达克罗德 说:gui401 说:@达克罗德 你好,这个裸机工程能放到eclipse里编译吗?是否可以用eclipse来代替@晕哥的IAR demo来单步调试呢?因为IAR jilink调试需要先烧录xboot,我现在想做的是能直接进行裸机单步并且能点亮屏幕。

eclipse编译肯定可以。调试我不懂。现在基本就靠打印来调试

谢谢!能分享一下这个裸机的eclipse工程吗?我自己建的编译出一堆错误,无从下手了。

我没有工程。按理eclipse也是执行我写的Makefile就好。不要用eclipse自己的Makefile

离线

楼主 #150 2019-12-10 10:47:37 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

你好@达克罗德 我用这个裸机工程在while(1)里通过寄存器翻转某个IO,示波器测频率只能达到3MHz,有办法提高吗?while里就read32和write32语句写0写1都执行一次读写,按道理不应该这么慢啊

没试过,我估计芯片设计决定的吧,记得有人说过,这种mpu翻转io还不如单片机的

离线

楼主 #167 2020-04-24 09:35:48 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

Nice work.

What "pdat->pwidth" and "pdat->pheight" are? What is "physical- width/height" ?

Is there a bare metal AUDIO or SD card driver?

it is LCD physical size. they are not used, you don't need care about it.

离线

楼主 #172 2020-04-26 18:18:06 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,134

- 积分: 1086.5

Re: F1C100S裸奔framebuffer+PWM+GPIO驱动

大佬你好,xboot支持F1C100S的硬件解码jpg以及音视频的播放吗?

据我所知是不支持的,RTT好像有网友实现了支持

离线