楼主 # 2022-04-27 16:58:23 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 72

D1s/f133-B 跑tina linux,有fb0设备,但是未执行LCD初始化函数

如题,用d1s点一块4寸的720x720的spi屏,系统跑起来后,能看到fb0设备,但是用GPIO模拟spi发命令和数据的引脚上没有量到有波形,一直是高电平,log也没看到跑进过LCD_panel_init函数;

设备树lcd相关的配置:

&lcd0 {

/* part 1 */

lcd_used = <1>;

lcd_driver_name = "axs1832a_720x720";

/* part 2 */

lcd_if = <0>;

lcd_hv_if = <0>;

/* part 3 */

lcd_x = <720>;

lcd_y = <720>;

lcd_width = <71>;

lcd_height = <71>;

lcd_dclk_freq = <35>;

lcd_hbp = <40>;

lcd_ht = <770>;

lcd_hspw = <2>;

lcd_vbp = <19>;

lcd_vt = <749>;

lcd_vspw = <2>;

/* part 4 */

lcd_backlight = <100>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <7>;

lcd_pwm_freq = <19000>;

lcd_pwm_pol = <0>;

lcd_pwm_max_limit = <255>;

lcd_lvds_if = <0>;

lcd_lvds_colordepth = <1>;

lcd_lvds_mode = <0>;

lcd_frm = <0>;

lcd_io_phase = <0x0000>;

lcd_gamma_en = <0>;

lcd_bright_curve_en = <0>;

lcd_cmap_en = <0>;

deu_mode = <0>;

lcdgamma4iep = <22>;

smart_color = <90>;

lcd_gpio_0 = <&pio PE 4 GPIO_ACTIVE_HIGH>;

lcd_gpio_1 = <&pio PD 22 GPIO_ACTIVE_HIGH>;

lcd_gpio_2 = <&pio PE 1 GPIO_ACTIVE_HIGH>;

lcd_gpio_3 = <&pio PE 0 GPIO_ACTIVE_HIGH>;

pinctrl-0 = <&rgb18_pins_a>;

pinctrl-1 = <&rgb18_pins_b>;

}

rgb18_pins_a: rgb18@0 {

pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \

"PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \

"PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \

"PD18", "PD19", "PD20", "PD21";

function = "lcd0";

drive-strength = <30>;

bias-disable;

};

rgb18_pins_b: rgb18@1 {

pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \

"PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \

"PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \

"PD18", "PD19", "PD20", "PD21";

function = "io_disabled";

bias-disable;

};屏驱动代码是拷贝了lichee/linux-5.4/drivers/video/fbdev/sunxi/disp2/disp/lcd/目录下的default_panel.c default_panel.h

在它的基础上加上SPI初始化代码的:

/*

* Allwinner SoCs display driver.

*

* Copyright (C) 2016 Allwinner.

*

* This file is licensed under the terms of the GNU General Public

* License version 2. This program is licensed "as is" without any

* warranty of any kind, whether express or implied.

*/

#include "axs1832a_720x720.h"

#define HIGH 1

#define LOW 0

static void LCD_power_on(u32 sel);

static void LCD_power_off(u32 sel);

static void LCD_bl_open(u32 sel);

static void LCD_bl_close(u32 sel);

static void LCD_panel_init(u32 sel);

static void LCD_panel_exit(u32 sel);

static void LCD_cfg_panel_info(struct panel_extend_para *info)

{

u32 i = 0, j = 0;

u32 items;

u8 lcd_gamma_tbl[][2] = {

/* {input value, corrected value} */

{0, 0},

{15, 15},

{30, 30},

{45, 45},

{60, 60},

{75, 75},

{90, 90},

{105, 105},

{120, 120},

{135, 135},

{150, 150},

{165, 165},

{180, 180},

{195, 195},

{210, 210},

{225, 225},

{240, 240},

{255, 255},

};

u32 lcd_cmap_tbl[2][3][4] = {

{

{LCD_CMAP_G0, LCD_CMAP_B1, LCD_CMAP_G2, LCD_CMAP_B3},

{LCD_CMAP_B0, LCD_CMAP_R1, LCD_CMAP_B2, LCD_CMAP_R3},

{LCD_CMAP_R0, LCD_CMAP_G1, LCD_CMAP_R2, LCD_CMAP_G3},

},

{

{LCD_CMAP_B3, LCD_CMAP_G2, LCD_CMAP_B1, LCD_CMAP_G0},

{LCD_CMAP_R3, LCD_CMAP_B2, LCD_CMAP_R1, LCD_CMAP_B0},

{LCD_CMAP_G3, LCD_CMAP_R2, LCD_CMAP_G1, LCD_CMAP_R0},

},

};

items = sizeof(lcd_gamma_tbl) / 2;

for (i = 0; i < items - 1; i++) {

u32 num = lcd_gamma_tbl[i + 1][0] - lcd_gamma_tbl[i][0];

for (j = 0; j < num; j++) {

u32 value = 0;

value =

lcd_gamma_tbl[i][1] +

((lcd_gamma_tbl[i + 1][1] -

lcd_gamma_tbl[i][1]) * j) / num;

info->lcd_gamma_tbl[lcd_gamma_tbl[i][0] + j] =

(value << 16) + (value << 8) + value;

}

}

info->lcd_gamma_tbl[255] =

(lcd_gamma_tbl[items - 1][1] << 16) +

(lcd_gamma_tbl[items - 1][1] << 8) + lcd_gamma_tbl[items - 1][1];

memcpy(info->lcd_cmap_tbl, lcd_cmap_tbl, sizeof(lcd_cmap_tbl));

}

static s32 LCD_open_flow(u32 sel)

{

/* open lcd power, and delay 50ms */

LCD_OPEN_FUNC(sel, LCD_power_on, 30);

/* open lcd power, than delay 200ms */

LCD_OPEN_FUNC(sel, LCD_panel_init, 50);

/* open lcd controller, and delay 100ms */

LCD_OPEN_FUNC(sel, sunxi_lcd_tcon_enable, 100);

/* open lcd backlight, and delay 0ms */

LCD_OPEN_FUNC(sel, LCD_bl_open, 0);

return 0;

}

static s32 LCD_close_flow(u32 sel)

{

/* close lcd backlight, and delay 0ms */

LCD_CLOSE_FUNC(sel, LCD_bl_close, 0);

/* close lcd controller, and delay 0ms */

LCD_CLOSE_FUNC(sel, sunxi_lcd_tcon_disable, 0);

/* open lcd power, than delay 200ms */

LCD_CLOSE_FUNC(sel, LCD_panel_exit, 200);

/* close lcd power, and delay 500ms */

LCD_CLOSE_FUNC(sel, LCD_power_off, 500);

return 0;

}

static void LCD_power_on(u32 sel)

{

/* config lcd_power pin to open lcd power0 */

sunxi_lcd_power_enable(sel, 0);

sunxi_lcd_pin_cfg(sel, 1);

/*#if defined(CONFIG_FPGA_V7_PLATFORM) || defined(CONFIG_FPGA_V4_PLATFORM)*/

/*struct disp_panel_para *panel_info =*/

/*kmalloc(sizeof(struct disp_panel_para), GFP_KERNEL | __GFP_ZERO);*/

/*bsp_disp_get_panel_info(sel, panel_info);*/

/*if (panel_info->lcd_if == LCD_IF_HV) {*/

/*writel(0x22222222, ioremap(0x0300b06c, 4));*/

/*writel(0x22222222, ioremap(0x0300b070, 4));*/

/*writel(0x22222222, ioremap(0x0300b074, 4));*/

/*writel(0x22222222, ioremap(0x0300b078, 4));*/

/*} else if(panel_info->lcd_if == LCD_IF_LVDS) {*/

/*writel(0x33333333, ioremap(0x0300b06c, 4));*/

/*writel(0x33333333, ioremap(0x0300b070, 4));*/

/*writel(0x33333333, ioremap(0x0300b074, 4));*/

/*writel(0x33333333, ioremap(0x0300b078, 4));*/

/*}*/

/*kfree(panel_info);*/

/*#endif*/

}

static void LCD_power_off(u32 sel)

{

sunxi_lcd_pin_cfg(sel, 0);

/* config lcd_power pin to close lcd power0 */

sunxi_lcd_power_disable(sel, 0);

}

static void LCD_bl_open(u32 sel)

{

sunxi_lcd_pwm_enable(sel);

sunxi_lcd_backlight_enable(sel);

}

static void LCD_bl_close(u32 sel)

{

/* config lcd_bl_en pin to close lcd backlight */

sunxi_lcd_backlight_disable(sel);

sunxi_lcd_pwm_disable(sel);

}

static void SetCsPinLevel(u8 val)

{

if (val) {

sunxi_lcd_gpio_set_value(0, 1, 1);

} else {

sunxi_lcd_gpio_set_value(0, 1, 0);

}

}

static void SetClkPinLevel(u8 val)

{

if (val) {

sunxi_lcd_gpio_set_value(0, 3, 1);

} else {

sunxi_lcd_gpio_set_value(0, 3, 0);

}

}

static void SetMosiPinLevel(u8 val)

{

if (val) {

sunxi_lcd_gpio_set_value(0, 2, 1);

} else {

sunxi_lcd_gpio_set_value(0, 2, 0);

}

}

static void SetResetPinLevel(u8 val)

{

if (val) {

sunxi_lcd_gpio_set_value(0, 0, 1);

} else {

sunxi_lcd_gpio_set_value(0, 0, 0);

}

}

static void SpiWriteAddr(u8 dat)

{

u8 i;

SetCsPinLevel(HIGH);

SetClkPinLevel(LOW);

sunxi_lcd_delay_us(5);

SetCsPinLevel(LOW);

SetClkPinLevel(LOW);

SetMosiPinLevel(LOW);

sunxi_lcd_delay_us(1);

SetClkPinLevel(HIGH);

sunxi_lcd_delay_us(1);

for (i = 0; i < 8; i++) {

SetClkPinLevel(LOW);

if (dat & 0x80) {

SetMosiPinLevel(HIGH);

} else {

SetMosiPinLevel(LOW);

}

dat <<= 1;

sunxi_lcd_delay_us(1);

SetClkPinLevel(HIGH);

sunxi_lcd_delay_us(1);

}

}

static void SpiWriteData(u8 dat)

{

u8 i;

SetClkPinLevel(LOW);

SetMosiPinLevel(HIGH);

sunxi_lcd_delay_us(1);

SetClkPinLevel(HIGH);

sunxi_lcd_delay_us(1);

for (i = 0; i < 8; i++) {

SetClkPinLevel(LOW);

if(dat & 0x80) {

SetMosiPinLevel(HIGH);

} else {

SetMosiPinLevel(LOW);

}

dat <<= 1;

sunxi_lcd_delay_us(1);

SetClkPinLevel(HIGH);

sunxi_lcd_delay_us(1);

}

}

static void LCD_panel_init(u32 sel)

{

printk(KERN_INFO "=====================LCD_panel_init\n");

SpiWriteAddr(0x11);

sunxi_lcd_delay_ms(100);

SpiWriteAddr(0xBB);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x5a);

SpiWriteData(0xa5);

SpiWriteData(0x0F);

SpiWriteAddr(0xc1);

SpiWriteData(0x73);

SpiWriteData(0x71);

SpiWriteData(0x02);

SpiWriteData(0x02);

SpiWriteData(0x71);

SpiWriteData(0x05);

SpiWriteData(0x06);

SpiWriteData(0x11);

SpiWriteData(0x55);

SpiWriteData(0x3F);

SpiWriteData(0xAA);

SpiWriteData(0xa0);

SpiWriteData(0x06);

SpiWriteData(0xFF);

SpiWriteData(0xFF);

SpiWriteData(0x7F);

SpiWriteData(0x4F);

SpiWriteData(0x52);

SpiWriteData(0x00);

SpiWriteData(0x4F);

SpiWriteData(0x52);

SpiWriteData(0x00);

SpiWriteData(0x96);

SpiWriteData(0x06);

SpiWriteData(0xC0);

SpiWriteData(0x01);

SpiWriteData(0x30);

SpiWriteData(0xC0);

SpiWriteData(0x01);

SpiWriteData(0x30);

SpiWriteAddr(0xc3);

SpiWriteData(0x05);

SpiWriteData(0x0A);

SpiWriteData(0x05);

SpiWriteData(0x0a);

SpiWriteData(0x00);

SpiWriteData(0xE0);

SpiWriteData(0x2E);

SpiWriteData(0x22);

SpiWriteData(0x1E);

SpiWriteData(0x78);

SpiWriteData(0x12);

SpiWriteData(0x22);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x0A);

SpiWriteData(0x0A);

SpiWriteData(0x10);

SpiWriteData(0x00);

SpiWriteData(0xF0);

SpiWriteData(0x18);

SpiWriteData(0x18);

SpiWriteData(0x40);

SpiWriteData(0x00);

SpiWriteData(0x22);

SpiWriteData(0x22);

SpiWriteData(0x0C);

SpiWriteData(0x00);

SpiWriteData(0xac);

SpiWriteData(0xca);

//11

SpiWriteAddr(0xCF);

SpiWriteData(0x47);

SpiWriteData(0x32);

SpiWriteData(0x00);

SpiWriteData(0x31);

SpiWriteData(0x55);

SpiWriteData(0x23);

SpiWriteData(0x12);

SpiWriteData(0x12);

SpiWriteData(0x51);

SpiWriteData(0x33);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0xFE);

SpiWriteData(0x01);

SpiWriteAddr(0xCD);

SpiWriteData(0x80);

SpiWriteData(0xd7);

SpiWriteData(0xad);

SpiWriteData(0x73);

SpiWriteData(0x00);

SpiWriteData(0x96);

SpiWriteData(0x0a);

SpiWriteData(0x01);

SpiWriteData(0x00);

SpiWriteData(0x14);

SpiWriteData(0x00);

SpiWriteData(0x04);

SpiWriteData(0xD0);

SpiWriteData(0xF8);

SpiWriteData(0x22);

SpiWriteData(0xD0);

SpiWriteData(0xE3);

SpiWriteData(0x22);

SpiWriteData(0x00);

SpiWriteAddr(0xd0);

SpiWriteData(0x01);

SpiWriteData(0x4A);

SpiWriteData(0xF8);

SpiWriteData(0x13);

SpiWriteData(0x20);

SpiWriteData(0x50);

SpiWriteData(0x07);

SpiWriteData(0xe8);

SpiWriteData(0x02);

SpiWriteData(0x07);

SpiWriteData(0x36);

SpiWriteData(0x05);

SpiWriteData(0x11);

SpiWriteData(0x0A);

SpiWriteData(0x64);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x11);

SpiWriteData(0x64);

SpiWriteData(0x03);

SpiWriteData(0x00);

SpiWriteAddr(0xd3);

SpiWriteData(0x00);

SpiWriteData(0x3d);

SpiWriteData(0x40);

SpiWriteData(0x44);

SpiWriteData(0x46);

SpiWriteData(0x48);

SpiWriteData(0x4a);

SpiWriteData(0x49);

SpiWriteData(0x5c);

SpiWriteData(0x59);

SpiWriteData(0x59);

SpiWriteData(0x5a);

SpiWriteData(0x59);

SpiWriteData(0x5a);

SpiWriteData(0x5a);

SpiWriteData(0x7f);

SpiWriteData(0x94);

SpiWriteData(0xa0);

SpiWriteData(0xaa);

SpiWriteData(0xa6);

SpiWriteData(0xa7);

SpiWriteData(0xb5);

SpiWriteData(0xb2);

SpiWriteData(0xb5);

SpiWriteData(0xbe);

SpiWriteData(0xba);

SpiWriteData(0xb2);

SpiWriteData(0xb9);

SpiWriteData(0xc2);

SpiWriteAddr(0xd4);

SpiWriteData(0x00);

SpiWriteData(0x3d);

SpiWriteData(0x40);

SpiWriteData(0x44);

SpiWriteData(0x46);

SpiWriteData(0x48);

SpiWriteData(0x4a);

SpiWriteData(0x49);

SpiWriteData(0x5c);

SpiWriteData(0x59);

SpiWriteData(0x59);

SpiWriteData(0x5a);

SpiWriteData(0x59);

SpiWriteData(0x5a);

SpiWriteData(0x5a);

SpiWriteData(0x7f);

SpiWriteData(0x94);

SpiWriteData(0xa0);

SpiWriteData(0xaa);

SpiWriteData(0xa6);

SpiWriteData(0xa7);

SpiWriteData(0xb5);

SpiWriteData(0xb2);

SpiWriteData(0xb5);

SpiWriteData(0xbe);

SpiWriteData(0xba);

SpiWriteData(0xb2);

SpiWriteData(0xb9);

SpiWriteData(0xc2);

SpiWriteAddr(0xd5);

SpiWriteData(0x60);

SpiWriteData(0x60);

SpiWriteData(0x85);

SpiWriteData(0x60);

SpiWriteData(0x26);

SpiWriteData(0x44);

SpiWriteData(0x07);

SpiWriteData(0x07);

SpiWriteData(0x00);

SpiWriteData(0x07);

SpiWriteData(0x07);

SpiWriteData(0x00);

SpiWriteData(0x12);

SpiWriteData(0x4c);

SpiWriteData(0xD5);

SpiWriteData(0x15);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x00);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x00);

SpiWriteData(0xd0);

SpiWriteData(0xa2);

SpiWriteData(0x13);

SpiWriteData(0x60);

SpiWriteData(0x60);

SpiWriteData(0x00);

SpiWriteAddr(0xd6);

SpiWriteData(0x10);

SpiWriteData(0x32);

SpiWriteData(0x54);

SpiWriteData(0x76);

SpiWriteData(0x98);

SpiWriteData(0xBA);

SpiWriteData(0xDC);

SpiWriteData(0xFE);

SpiWriteData(0x01);

SpiWriteData(0x83);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x07);

SpiWriteData(0x07);

SpiWriteData(0x00);

SpiWriteData(0x07);

SpiWriteData(0x07);

SpiWriteData(0x00);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x30);

SpiWriteData(0x10);

SpiWriteData(0x33);

SpiWriteData(0x77);

SpiWriteData(0x77);

SpiWriteData(0x40);

SpiWriteAddr(0xdd);

SpiWriteData(0x1d);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1e);

SpiWriteData(0x1f);

SpiWriteData(0x02);

SpiWriteData(0x00);

SpiWriteData(0x0c);

SpiWriteData(0x0e);

SpiWriteData(0x08);

SpiWriteData(0x0a);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteAddr(0xd9);

SpiWriteData(0x1c);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1e);

SpiWriteData(0x1f);

SpiWriteData(0x03);

SpiWriteData(0x01);

SpiWriteData(0x0d);

SpiWriteData(0x0f);

SpiWriteData(0x09);

SpiWriteData(0x0b);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteAddr(0xd7);

SpiWriteData(0x1d);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1e);

SpiWriteData(0x00);

SpiWriteData(0x02);

SpiWriteData(0x0a);

SpiWriteData(0x08);

SpiWriteData(0x0e);

SpiWriteData(0x0c);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteAddr(0xd8);

SpiWriteData(0x1c);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1e);

SpiWriteData(0x01);

SpiWriteData(0x03);

SpiWriteData(0x0b);

SpiWriteData(0x09);

SpiWriteData(0x0f);

SpiWriteData(0x0d);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteData(0x1f);

SpiWriteAddr(0xc4);

SpiWriteData(0x54);

SpiWriteData(0x00);

SpiWriteAddr(0xDF);

SpiWriteData(0x22);

SpiWriteData(0x03);

SpiWriteData(0x33);

SpiWriteData(0xf1);

SpiWriteData(0x33);

SpiWriteData(0x08);

SpiWriteData(0x02);

SpiWriteData(0x17);

SpiWriteData(0x00);

SpiWriteData(0x00);

SpiWriteData(0x20);

SpiWriteData(0x17);

SpiWriteAddr(0xCE);

SpiWriteData(0x01);

SpiWriteData(0x09);

SpiWriteData(0xF0);

SpiWriteData(0xF0);

SpiWriteData(0x03);

SpiWriteData(0x03);

SpiWriteData(0x04);

SpiWriteData(0x04);

SpiWriteData(0x04);

SpiWriteData(0x05);

SpiWriteData(0x06);

SpiWriteData(0x07);

SpiWriteData(0x08);

SpiWriteData(0x09);

SpiWriteData(0x0A);

SpiWriteData(0x0B);

SpiWriteData(0x0C);

SpiWriteData(0x0D);

SpiWriteData(0x0E);

SpiWriteData(0x0F);

SpiWriteData(0x10);

SpiWriteData(0x11);

SpiWriteData(0x12);

SpiWriteData(0x13);

SpiWriteData(0x14);

SpiWriteData(0x15);

SpiWriteData(0x16);

SpiWriteData(0x17);

SpiWriteData(0x18);

sunxi_lcd_delay_ms(200);

SpiWriteAddr(0x29);

return;

}

static void LCD_panel_exit(u32 sel)

{

}

/* sel: 0:lcd0; 1:lcd1 */

static s32 LCD_user_defined_func(u32 sel, u32 para1, u32 para2, u32 para3)

{

return 0;

}

struct __lcd_panel axs1832a_720x720_pannel = {

/* panel driver name, must mach the lcd_drv_name in sys_config.fex */

.name = "axs1832a_720x720",

.func = {

.cfg_panel_info = LCD_cfg_panel_info,

.cfg_open_flow = LCD_open_flow,

.cfg_close_flow = LCD_close_flow,

.lcd_user_defined_func = LCD_user_defined_func,

}

,

};static void LCD_panel_init(u32 sel)

{

printk(KERN_INFO "=====================LCD_panel_init\n");

......

}

LCD_panel_init函数里面有加了打印信息,但是log里面没看到有打印出来,模拟spi的IO口上也没有量到有波形,说明并未跑进LCD_panel_init函数;

打印log:

[113]HELLO! BOOT0 is starting!

[116]BOOT0 commit : 88480af

[118]set pll start

[120]fix vccio detect value:0xc0

[123]periph0 has been enabled

[126]set pll end

[128][pmu]: bus read error

[130]board init ok

[132]ZQ value = 0x2f

[134]get_pmu_exist() = -1

[137]ddr_efuse_type: 0xa

[139]trefi:7.8ms

[141][AUTO DEBUG] single rank and full DQ!

[145]ddr_efuse_type: 0xa

[147]trefi:7.8ms

[149][AUTO DEBUG] rank 0 row = 13

[153][AUTO DEBUG] rank 0 bank = 4

[156][AUTO DEBUG] rank 0 page size = 2 KB

[160]DRAM BOOT DRIVE INFO: V0.33

[163]DRAM CLK = 528 MHz

[165]DRAM Type = 2 (2:DDR2,3:DDR3)

[168]DRAMC read ODT off.

[171]DRAM ODT off.

[172]ddr_efuse_type: 0xa

[175]DRAM SIZE =64 M

[177]dram_tpr4:0x0

[179]PLL_DDR_CTRL_REG:0xf8002b00

[182]DRAM_CLK_REG:0xc0000000

[185][TIMING DEBUG] MR2= 0x0

[189]DRAM simple test OK.

[191]dram size =64

[193]card no is 0

[195]sdcard 0 line count 4

[197][mmc]: mmc driver ver 2021-04-2 16:45

[207][mmc]: Wrong media type 0x0

[210][mmc]: ***Try SD card 0***

[218][mmc]: HSSDR52/SDR25 4 bit

[221][mmc]: 50000000 Hz

[224][mmc]: 15240 MB

[225][mmc]: ***SD/MMC 0 init OK!!!***

[275]Loading boot-pkg Succeed(index=0).

[278]Entry_name = opensbi

[281]Entry_name = u-boot

[285]Entry_name = dtb

[288]mmc not para

▒289]Jump to second Boot.

U-Boot 2018.05-g24521d6 (Feb 11 2022 - 08:52:39 +0000) Allwinner Technology

[00.299]DRAM: 64 MiB

[00.301]Relocation Offset is: 01ee7000

[00.306]secure enable bit: 0

[00.309]CPU=720 MHz,PLL6=600 Mhz,AHB=200 Mhz, APB1=100Mhz MBus=300Mhz

[00.315]flash init start

[00.317]workmode = 0,storage type = 1

[00.321][mmc]: mmc driver ver uboot2018:2021-11-19 15:38:00

[00.326][mmc]: get sdc_type fail and use default host:tm1.

[00.333][mmc]: can't find node "mmc0",will add new node

[00.338][mmc]: fdt err returned <no error>

[00.342][mmc]: Using default timing para

[00.345][mmc]: SUNXI SDMMC Controller Version:0x50310

[00.363][mmc]: card_caps:0x3000000a

[00.366][mmc]: host_caps:0x3000003f

[00.369]sunxi flash init ok

[00.372]line:703 init_clocks

[00.375]drv_disp_init

request pwm success, pwm7:pwm7:0x2000c00.

[00.396]drv_disp_init finish

[00.399]boot_gui_init:start

[00.402]set disp.dev2_output_type fail. using defval=0

[00.409]boot_gui_init:finish

partno erro : can't find partition bootloader

54 bytes read in 1 ms (52.7 KiB/s)

[00.425]bmp_name=bootlogo.bmp size 38454

38454 bytes read in 3 ms (12.2 MiB/s)

[00.444]Loading Environment from SUNXI_FLASH... OK

[00.466]out of usb burn from boot: not need burn key

[00.500]Item0 (Map) magic is bad

[00.503]the secure storage item0 copy0 magic is bad

[00.537]Item0 (Map) magic is bad

[00.540]the secure storage item0 copy1 magic is bad

[00.545]Item0 (Map) magic is bad

partno erro : can't find partition private

root_partition is rootfs

set root to /dev/mmcblk0p5

[00.557]update part info

[00.560]update bootcmd

[00.563]change working_fdt 0x42aa6da0 to 0x42a86da0

disable nand error: FDT_ERR_BADPATH

No reserved memory region found in source FDT

FDT ERROR:get muxsel err returned FDT_ERR_INTERNAL

sunxi_pwm_pin_set_state, fdt_set_all_pin, ret=-1

[00.600]LCD open finish

[00.614]update dts

noncached_alloc(): addr = 0x42c8a080

noncached_alloc(): addr = 0x42c8a0c0

noncached_alloc(): addr = 0x42c8a100

noncached_alloc(): addr = 0x42c8a940

geth_sys_init:634: get node 'gmac0' error

geth_sys_init fail!

[00.635]Board Net Initialization Failed

[00.638]No ethernet found.

Hit any key to stop autoboot: 0

[01.941]no vendor_boot partition is found

Android's image name: d1s-nezha

Detect comp none

[01.958]

Starting kernel ...

[01.960][mmc]: MMC Device 2 not found

[01.964][mmc]: mmc 2 not find, so not exit

** 2 printk messages dropped **

DMA32 [mem 0x0000000040000000-0x0000000043ffffff]

Normal empty

Movable zone start for each node

Early memory node ranges

node 0: [mem 0x0000000040000000-0x0000000043ffffff]

Initmem setup node 0 [mem 0x0000000040000000-0x0000000043ffffff]

On node 0 totalpages: 16384

DMA32 zone: 224 pages used for memmap

DMA32 zone: 0 pages reserved

DMA32 zone: 16384 pages, LIFO batch:3

elf_hwcap is 0x20112d

pcpu-alloc: s0 r0 d32768 u32768 alloc=1*32768

pcpu-alloc: [0] 0

Built 1 zonelists, mobility grouping on. Total pages: 16160

Kernel command line: earlyprintk=sunxi-uart,0x02500000 clk_ignore_unused initcall_debug=0 console=ttyS0,115200 loglevel=8 root=/dev/mmcblk0p5 init=/pseudo_init partitions=boot-resource@mmcblk0p1:env@mmcblk0p2:env-redund@mmcblk0p3:boot@mmcblk0p4:rootfs@mmcblk0p5:recovery@mmcblk0p6:rootfs_data@mmcblk0p7:UDISK@mmcblk0p8 cma=0M snum= mac_addr= wifi_mac= bt_mac= specialstr= gpt=1 androidboot.mode=normal androidboot.hardware=sun20iw1p1 boot_type=1 androidboot.boot_type=1 gpt=1 uboot_message=2018.05-g24521d6(02/11/2022-08:52:39) mbr_

Dentry cache hash table entries: 8192 (order: 4, 65536 bytes, linear)

Inode-cache hash table entries: 4096 (order: 3, 32768 bytes, linear)

Sorting __ex_table...

mem auto-init: stack:off, heap alloc:off, heap free:off

Memory: 55728K/65536K available (4316K kernel code, 397K rwdata, 1681K rodata, 140K init, 229K bss, 9808K reserved, 0K cma-reserved)

SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

rcu: Preemptible hierarchical RCU implementation.

Tasks RCU enabled.

rcu: RCU calculated value of scheduler-enlistment delay is 10 jiffies.

NR_IRQS: 0, nr_irqs: 0, preallocated irqs: 0

plic: mapped 200 interrupts with 1 handlers for 2 contexts.

riscv_timer_init_dt: Registering clocksource cpuid [0] hartid [0]

clocksource: riscv_clocksource: mask: 0xffffffffffffffff max_cycles: 0x588fe9dc0, max_idle_ns: 440795202592 ns

sched_clock: 64 bits at 24MHz, resolution 41ns, wraps every 4398046511097ns

riscv_timer_clockevent depends on broadcast, but no broadcast function available

clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns

Calibrating delay loop (skipped), value calculated using timer frequency.. 48.00 BogoMIPS (lpj=240000)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 512 (order: 0, 4096 bytes, linear)

Mountpoint-cache hash table entries: 512 (order: 0, 4096 bytes, linear)

ASID allocator initialised with 65536 entries

rcu: Hierarchical SRCU implementation.

devtmpfs: initialized

random: get_random_u32 called from bucket_table_alloc.isra.27+0xfe/0x120 with crng_init=0

clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

futex hash table entries: 256 (order: 0, 6144 bytes, linear)

pinctrl core: initialized pinctrl subsystem

NET: Registered protocol family 16

DMA: preallocated 256 KiB pool for atomic allocations

cpuidle: using governor menu

rtc_ccu: sunxi ccu init OK

clock: sunxi ccu init OK

clock: sunxi ccu init OK

iommu: Default domain type: Translated

sunxi iommu: irq = 4

SCSI subsystem initialized

usbcore: registered new interface driver usbfs

usbcore: registered new interface driver hub

usbcore: registered new device driver usb

videodev: Linux video capture interface: v2.00

Advanced Linux Sound Architecture Driver Initialized.

pwm module init!

g2d 5410000.g2d: Adding to iommu group 0

G2D: rcq version initialized.major:252

clocksource: Switched to clocksource riscv_clocksource

sun8iw20-pinctrl 2000000.pinctrl: initialized sunXi PIO driver

NET: Registered protocol family 2

tcp_listen_portaddr_hash hash table entries: 256 (order: 0, 4096 bytes, linear)

TCP established hash table entries: 512 (order: 0, 4096 bytes, linear)

TCP bind hash table entries: 512 (order: 0, 4096 bytes, linear)

TCP: Hash tables configured (established 512 bind 512)

UDP hash table entries: 256 (order: 1, 8192 bytes, linear)

UDP-Lite hash table entries: 256 (order: 1, 8192 bytes, linear)

NET: Registered protocol family 1

sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pc not found, using dummy regulator

spi spi0: spi0 supply spi not found, using dummy regulator

sunxi_spi_resource_get()2151 - [spi0] SPI MASTER MODE

sunxi_spi_resource_get()2189 - Failed to get sample mode

sunxi_spi_resource_get()2194 - Failed to get sample delay

sunxi_spi_resource_get()2198 - sample_mode:-1431633921 sample_delay:-1431633921

sunxi_spi_clk_init()2240 - [spi0] mclk 100000000

sunxi_spi_probe()2653 - [spi0]: driver probe succeed, base ffffffd004058000, irq 31

workingset: timestamp_bits=62 max_order=14 bucket_order=0

squashfs: version 4.0 (2009/01/31) Phillip Lougher

ntfs: driver 2.1.32 [Flags: R/W].

io scheduler mq-deadline registered

io scheduler kyber registered

[DISP]disp_module_init

disp 5000000.disp: Adding to iommu group 0

[DISP] parser_disp_init_para,line:1430:

of_property_read fb0_width fail

[DISP] disp_init,line:2386:

smooth display screen:0 type:1 mode:4

display_fb_request,fb_id:0

Freeing logo buffer memory: 1500K

disp_al_manager_apply ouput_type:1

[DISP] lcd_clk_config,line:732:

disp 0, clk: pll(210000000),clk(210000000),dclk(35000000) dsi_rate(210000000)

clk real:pll(288000000),clk(288000000),dclk(48000000) dsi_rate(0)

sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pd not found, using dummy regulator

[DISP]disp_module_init finish

sunxi_sid_init()551 - insmod ok

pwm-regulator: supplied by regulator-dummy

sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pe not found, using dummy regulator

uart uart0: get regulator failed

uart uart0: uart0 supply uart not found, using dummy regulator

uart0: ttyS0 at MMIO 0x2500000 (irq = 18, base_baud = 1500000) is a SUNXI

sw_console_setup()1808 - console setup baud 115200 parity n bits 8, flow n

printk: console [ttyS0] enabled

misc dump reg init

sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pg not found, using dummy regulator

sunxi-rfkill soc@3000000:rfkill@0: module version: v1.0.9

sunxi-rfkill soc@3000000:rfkill@0: get gpio chip_en failed

sunxi-rfkill soc@3000000:rfkill@0: get gpio power_en failed

sunxi-rfkill soc@3000000:rfkill@0: wlan_busnum (1)

sunxi-rfkill soc@3000000:rfkill@0: Missing wlan_power.

sunxi-rfkill soc@3000000:rfkill@0: wlan clock[0] (32k-fanout1)

sunxi-rfkill soc@3000000:rfkill@0: wlan_regon gpio=131 assert=1

sun8iw20-pinctrl 2000000.pinctrl: pin PE3 already requested by 2500000.uart; cannot claim for 2000000.pinctrl:131

sun8iw20-pinctrl 2000000.pinctrl: pin-131 (2000000.pinctrl:131) status -22

sunxi-rfkill soc@3000000:rfkill@0: can't request wlan_regon gpio 131

sunxi-rfkill: probe of soc@3000000:rfkill@0 failed with error -22

[ADDR_MGT] addr_mgt_probe: module version: v1.0.10

[ADDR_MGT] addr_mgt_probe: success.

sunxi-spinand: AW SPINand MTD Layer Version: 2.0 20201228

sunxi-spinand-phy: AW SPINand Phy Layer Version: 1.10 20200306

sunxi-spinand-phy: not detect any munufacture from id table

sunxi-spinand-phy: get spi-nand Model from fdt fail

sunxi-spinand-phy: get phy info from fdt fail

sunxi-spinand-phy: not detect munufacture from fdt

sunxi-spinand-phy: detect munufacture from id table: Micron

sunxi-spinand-phy: detect spinand id: ffff242c ffffffff

sunxi-spinand-phy: ========== arch info ==========

sunxi-spinand-phy: Model: MT29F2G01ABAGDWB

sunxi-spinand-phy: Munufacture: Micron

sunxi-spinand-phy: DieCntPerChip: 1

sunxi-spinand-phy: BlkCntPerDie: 2048

sunxi-spinand-phy: PageCntPerBlk: 64

sunxi-spinand-phy: SectCntPerPage: 4

sunxi-spinand-phy: OobSizePerPage: 64

sunxi-spinand-phy: BadBlockFlag: 0x0

sunxi-spinand-phy: OperationOpt: 0x8f

sunxi-spinand-phy: MaxEraseTimes: 65000

sunxi-spinand-phy: EccFlag: 0x0

sunxi-spinand-phy: EccType: 6

sunxi-spinand-phy: EccProtectedType: 5

sunxi-spinand-phy: ========================================

sunxi-spinand-phy:

sunxi-spinand-phy: ========== physical info ==========

sunxi-spinand-phy: TotalSize: 256 M

sunxi-spinand-phy: SectorSize: 512 B

sunxi-spinand-phy: PageSize: 2 K

sunxi-spinand-phy: BlockSize: 128 K

sunxi-spinand-phy: OOBSize: 64 B

sunxi-spinand-phy: ========================================

sunxi-spinand-phy:

sunxi-spinand-phy: ========== logical info ==========

sunxi-spinand-phy: TotalSize: 256 M

sunxi-spinand-phy: SectorSize: 512 B

sunxi-spinand-phy: PageSize: 4 K

sunxi-spinand-phy: BlockSize: 256 K

sunxi-spinand-phy: OOBSize: 128 B

sunxi-spinand-phy: ========================================

sunxi-spinand-phy: MT29F2G01ABAGDWB reset rx bit width to 1

sunxi-spinand-phy: MT29F2G01ABAGDWB reset tx bit width to 1

sunxi-spinand-phy: block lock register: 0x00

sunxi-spinand-phy: feature register: 0x10

sunxi-spinand-phy: sunxi physic nand init end

Creating 4 MTD partitions on "sunxi_mtd_nand":

0x000000000000-0x000000100000 : "boot0"

0x000000100000-0x000000500000 : "uboot"

random: fast init done

0x000000500000-0x000000600000 : "secure_storage"

0x000000600000-0x000010000000 : "sys"

random: crng init done

ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

sunxi-ehci: EHCI SUNXI driver

get ehci1-controller wakeup-source is fail.

sunxi ehci1-controller don't init wakeup source

[sunxi-ehci1]: probe, pdev->name: 4200000.ehci1-controller, sunxi_ehci: 0xffffffe00068b870, 0x:ffffffd00406f000, irq_no:31

sunxi-ehci 4200000.ehci1-controller: 4200000.ehci1-controller supply drvvbus not found, using dummy regulator

sunxi-ehci 4200000.ehci1-controller: 4200000.ehci1-controller supply hci not found, using dummy regulator

sunxi-ehci 4200000.ehci1-controller: EHCI Host Controller

sunxi-ehci 4200000.ehci1-controller: new USB bus registered, assigned bus number 1

sunxi-ehci 4200000.ehci1-controller: irq 49, io mem 0x04200000

sunxi-ehci 4200000.ehci1-controller: USB 2.0 started, EHCI 1.00

hub 1-0:1.0: USB hub found

hub 1-0:1.0: 1 port detected

ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

sunxi-ohci: OHCI SUNXI driver

get ohci1-controller wakeup-source is fail.

sunxi ohci1-controller don't init wakeup source

[sunxi-ohci1]: probe, pdev->name: 4200400.ohci1-controller, sunxi_ohci: 0xffffffe00068bc38

sunxi-ohci 4200400.ohci1-controller: 4200400.ohci1-controller supply drvvbus not found, using dummy regulator

sunxi-ohci 4200400.ohci1-controller: 4200400.ohci1-controller supply hci not found, using dummy regulator

sunxi-ohci 4200400.ohci1-controller: OHCI Host Controller

sunxi-ohci 4200400.ohci1-controller: new USB bus registered, assigned bus number 2

sunxi-ohci 4200400.ohci1-controller: irq 50, io mem 0x04200400

hub 2-0:1.0: USB hub found

hub 2-0:1.0: 1 port detected

sunxi-rtc 7090000.rtc: errata__fix_alarm_day_reg_default_value(): ALARM0_DAY_REG=0, set it to 1

sunxi-rtc 7090000.rtc: registered as rtc0

sunxi-rtc 7090000.rtc: setting system clock to 1970-01-01T00:00:04 UTC (4)

sunxi-rtc 7090000.rtc: sunxi rtc probed

i2c /dev entries driver

IR NEC protocol handler initialized

uvcvideo: Unable to create debugfs directory

usbcore: registered new interface driver uvcvideo

USB Video Class driver (1.1.1)

sunxi cedar version 1.1

sunxi-cedar 1c0e000.ve: Adding to iommu group 0

VE: install start!!!

VE: cedar-ve the get irq is 6

VE: install end!!!

VE: sunxi_cedar_probe

sunxi-mmc 4020000.sdmmc: SD/MMC/SDIO Host Controller Driver(v4.21 2021-11-18 10:02)

sunxi-mmc 4020000.sdmmc: ***ctl-spec-caps*** 8

sunxi-mmc 4020000.sdmmc: No vmmc regulator found

sunxi-mmc 4020000.sdmmc: No vqmmc regulator found

sunxi-mmc 4020000.sdmmc: No vdmmc regulator found

sunxi-mmc 4020000.sdmmc: No vd33sw regulator found

sunxi-mmc 4020000.sdmmc: No vd18sw regulator found

sunxi-mmc 4020000.sdmmc: No vq33sw regulator found

sunxi-mmc 4020000.sdmmc: No vq18sw regulator found

sunxi-mmc 4020000.sdmmc: Got CD GPIO

sunxi-mmc 4020000.sdmmc: set cd-gpios as 24M fail

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 0Hz bm PP pm UP vdd 21 width 1 timing LEGACY(SDR12) dt B

sunxi-mmc 4020000.sdmmc: no vqmmc,Check if there is regulator

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

sunxi-mmc 4020000.sdmmc: detmode:gpio irq

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

sunxi-mmc 4021000.sdmmc: SD/MMC/SDIO Host Controller Driver(v4.21 2021-11-18 10:02)

sunxi-mmc 4021000.sdmmc: ***ctl-spec-caps*** 8

sunxi-mmc 4021000.sdmmc: No vmmc regulator found

sunxi-mmc 4021000.sdmmc: No vqmmc regulator found

sunxi-mmc 4021000.sdmmc: No vdmmc regulator found

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

sunxi-mmc 4021000.sdmmc: No vd33sw regulator found

sunxi-mmc 4021000.sdmmc: No vd18sw regulator found

sunxi-mmc 4021000.sdmmc: No vq33sw regulator found

sunxi-mmc 4021000.sdmmc: No vq18sw regulator found

sunxi-mmc 4021000.sdmmc: Cann't get pin bias hs pinstate,check if needed

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

sunxi-mmc 4021000.sdmmc: sdc set ios:clk 0Hz bm PP pm UP vdd 21 width 1 timing LEGACY(SDR12) dt B

sunxi-mmc 4021000.sdmmc: no vqmmc,Check if there is regulator

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

sunxi-mmc 4021000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

sunxi-mmc 4021000.sdmmc: detmode:manually by software

sunxi-mmc 4021000.sdmmc: smc 1 p1 err, cmd 52, RTO !!

ashmem: initialized

sunxi-mmc 4021000.sdmmc: smc 1 p1 err, cmd 52, RTO !!

sunxi-mmc 4021000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

exFAT: Version 1.3.0

sunxi-mmc 4021000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

mmc0: host does not support reading read-only switch, assuming write-enable

[AUDIOCODEC][sunxi_codec_parse_params][2412]:digital_vol:0, lineout_vol:26, mic1gain:31, mic2gain:31 pa_msleep:120, pa_level:1, pa_pwr_level:1

[AUDIOCODEC][sunxi_codec_parse_params][2448]:adcdrc_cfg:0, adchpf_cfg:1, dacdrc_cfg:0, dachpf:0

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing SD-HS(SDR25) dt B

[AUDIOCODEC][sunxi_internal_codec_probe][2609]:codec probe finished

sunxi-mmc 4021000.sdmmc: smc 1 p1 err, cmd 5, RTO !!

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 50000000Hz bm PP pm ON vdd 21 width 1 timing SD-HS(SDR25) dt B

sunxi-mmc 4021000.sdmmc: smc 1 p1 err, cmd 5, RTO !!

sunxi-mmc 4021000.sdmmc: smc 1 p1 err, cmd 5, RTO !!

sunxi-mmc 4020000.sdmmc: sdc set ios:clk 50000000Hz bm PP pm ON vdd 21 width 4 timing SD-HS(SDR25) dt B

sunxi-mmc 4021000.sdmmc: smc 1 p1 err, cmd 5, RTO !!

sunxi-mmc 4021000.sdmmc: sdc set ios:clk 0Hz bm PP pm OFF vdd 0 width 1 timing LEGACY(SDR12) dt B

mmc0: new high speed SDHC card at address 59b4

sid_rd_ver_reg()254 - ver >= 4, soc ver:5

[SNDCODEC][sunxi_card_init][583]:card init finished

sunxi-codec-machine 2030340.sound: 2030000.codec <-> 203034c.dummy_cpudai mapping ok

mmcblk0: mmc0:59b4 14.9 GiB

mmcblk0: p1 p2 p3 p4 p5 p6 p7 p8

input: audiocodec sunxi Audio Jack as /devices/platform/soc@3000000/2030340.sound/sound/card0/input0

[SNDCODEC][sunxi_card_dev_probe][836]:register card finished

NET: Registered protocol family 10

[SNDCODEC][sunxi_hs_init_work][259]:resume-->report switch

Segment Routing with IPv6

NET: Registered protocol family 17

sunxi-i2c sunxi-i2c2: sunxi-i2c2 supply twi not found, using dummy regulator

sunxi-i2c sunxi-i2c2: probe success

sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pb not found, using dummy regulator

get ehci0-controller wakeup-source is fail.

sunxi ehci0-controller don't init wakeup source

[sunxi-ehci0]: probe, pdev->name: 4101000.ehci0-controller, sunxi_ehci: 0xffffffe00068b0e0, 0x:ffffffd004875000, irq_no:2e

[sunxi-ehci0]: Not init ehci0

get ohci0-controller wakeup-source is fail.

sunxi ohci0-controller don't init wakeup source

[sunxi-ohci0]: probe, pdev->name: 4101400.ohci0-controller, sunxi_ohci: 0xffffffe00068b4a8

[sunxi-ohci0]: Not init ohci0

clk: Not disabling unused clocks

ALSA device list:

platform regulatory.0: Direct firmware load for regulatory.db failed with error -2

#0: audiocodec

alloc_fd: slot 0 not NULL!

cfg80211: failed to load regulatory.db

VFS: Mounted root (squashfs filesystem) readonly on device 179:5.

devtmpfs: mounted

Freeing unused kernel memory: 140K

This architecture does not have kernel memory protection.

Run /pseudo_init as init process

mount: mounting none on /dev failed: Device or resource busy

mount: mounting /dev/by-name/rootfs_data on /overlay failed: No such device

Mount Failed: formating /dev/by-name/rootfs_data to ext4 ...

/pseudo_init: line 395: mkfs.ext4: not found

can't run '/etc/preinit': No such file or directory

mount: mounting proc on /proc failed: Device or resource busy

mount: mounting tmpfs on /run failed: No such file or directory

hostname: can't open '/etc/hostname': No such file or directory

------run rc.preboot file-----

/etc/init.d/rcS: line 136: mkfs.ext4: not found

------run rc.modules file-----

------run rc.final file-----

file system registered

configfs-gadget 4100000.udc-controller: failed to start g1: -19

sh: write error: No such device

read descriptors

read strings

insmod_host_driver

[ehci0-controller]: sunxi_usb_enable_ehci

[sunxi-ehci0]: probe, pdev->name: 4101000.ehci0-controller, sunxi_ehci: 0xffffffe00068b0e0, 0x:ffffffd004875000, irq_no:2e

sunxi-ehci 4101000.ehci0-controller: 4101000.ehci0-controller supply hci not found, using dummy regulator

sunxi-ehci 4101000.ehci0-controller: EHCI Host Controller

sunxi-ehci 4101000.ehci0-controller: new USB bus registered, assigned bus number 3

sunxi-ehci 4101000.ehci0-controller: irq 46, io mem 0x04101000

sunxi-ehci 4101000.ehci0-controller: USB 2.0 started, EHCI 1.00

hub 3-0:1.0: USB hub found

hub 3-0:1.0: 1 port detected

[ohci0-controller]: sunxi_usb_enable_ohci

[sunxi-ohci0]: probe, pdev->name: 4101400.ohci0-controller, sunxi_ohci: 0xffffffe00068b4a8

sunxi-ohci 4101400.ohci0-controller: 4101400.ohci0-controller supply hci not found, using dummy regulator

sunxi-ohci 4101400.ohci0-controller: OHCI Host Controller

sunxi-ohci 4101400.ohci0-controller: new USB bus registered, assigned bus number 4

sunxi-ohci 4101400.ohci0-controller: irq 47, io mem 0x04101400

hub 4-0:1.0: USB hub found

hub 4-0:1.0: 1 port detected

host_chose finished!

BusyBox v1.27.2 () built-in shell (ash)

nice: can't execute '/usr/bin/story_ota_bin': No such file or directory

------run profile file-----

_____ _ __ _

|_ _||_| ___ _ _ | | |_| ___ _ _ _ _

| | _ | || | | |__ | || || | ||_'_|

| | | || | || _ | |_____||_||_|_||___||_,_|

|_| |_||_|_||_|_| Tina is Based on OpenWrt!

----------------------------------------------

Tina Linux (Neptune, 61CC0487)

----------------------------------------------

root@TinaLinux:/#

root@TinaLinux:/#

root@TinaLinux:/# ls /dev/

ashmem kmsg mtd2 snd

bus mmcblk0 mtd2ro sunxi-reg

by-name mmcblk0p1 mtd3 sunxi_pwm0

cedar_dev mmcblk0p2 mtd3ro sunxi_soc_info

console mmcblk0p3 mtdblock0 tty

cpu_dma_latency mmcblk0p4 mtdblock1 ttyS0

disp mmcblk0p5 mtdblock2 ubi_ctrl

fb0 mmcblk0p6 mtdblock3 urandom

full mmcblk0p7 null usb-ffs

g2d mmcblk0p8 ptmx video4

gpiochip0 mtd0 pts zero

i2c-2 mtd0ro random

input mtd1 rtc0

ion mtd1ro shm

root@TinaLinux:/# cat /sys/class/

addr_mgt/ ieee80211/ scsi_host/

android_usb/ input/ sound/

bdi/ iommu/ spi_master/

block/ mem/ sunxi_dump/

cedar_ve/ misc/ sunxi_info/

devlink/ mmc_host/ sunxi_pwm_char_class/

disp/ mtd/ tty/

dma/ net/ ubi/

g2d/ power_supply/ udc/

gpio/ pwm/ udc_reg/

graphics/ rc/ usb_role/

hci_reg/ regulator/ video4linux/

hwmon/ rtc/ wakeup/

i2c-adapter/ scsi_device/

i2c-dev/ scsi_disk/

root@TinaLinux:/# cat /sys/class/graphics/fb0/

bits_per_pixel mode state

blank modes stride

console name subsystem/

cursor pan uevent

dev power/ virtual_size

device/ rotate waiting_for_supplier

root@TinaLinux:/# cat /sys/class/graphics/fb0/mode

mode modes

root@TinaLinux:/# cat /sys/class/graphics/fb0/modes

U:720x720p-60

root@TinaLinux:/#有大佬知道是什么原因吗?

离线

楼主 #1 2022-04-27 17:55:45 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 72

Re: D1s/f133-B 跑tina linux,有fb0设备,但是未执行LCD初始化函数

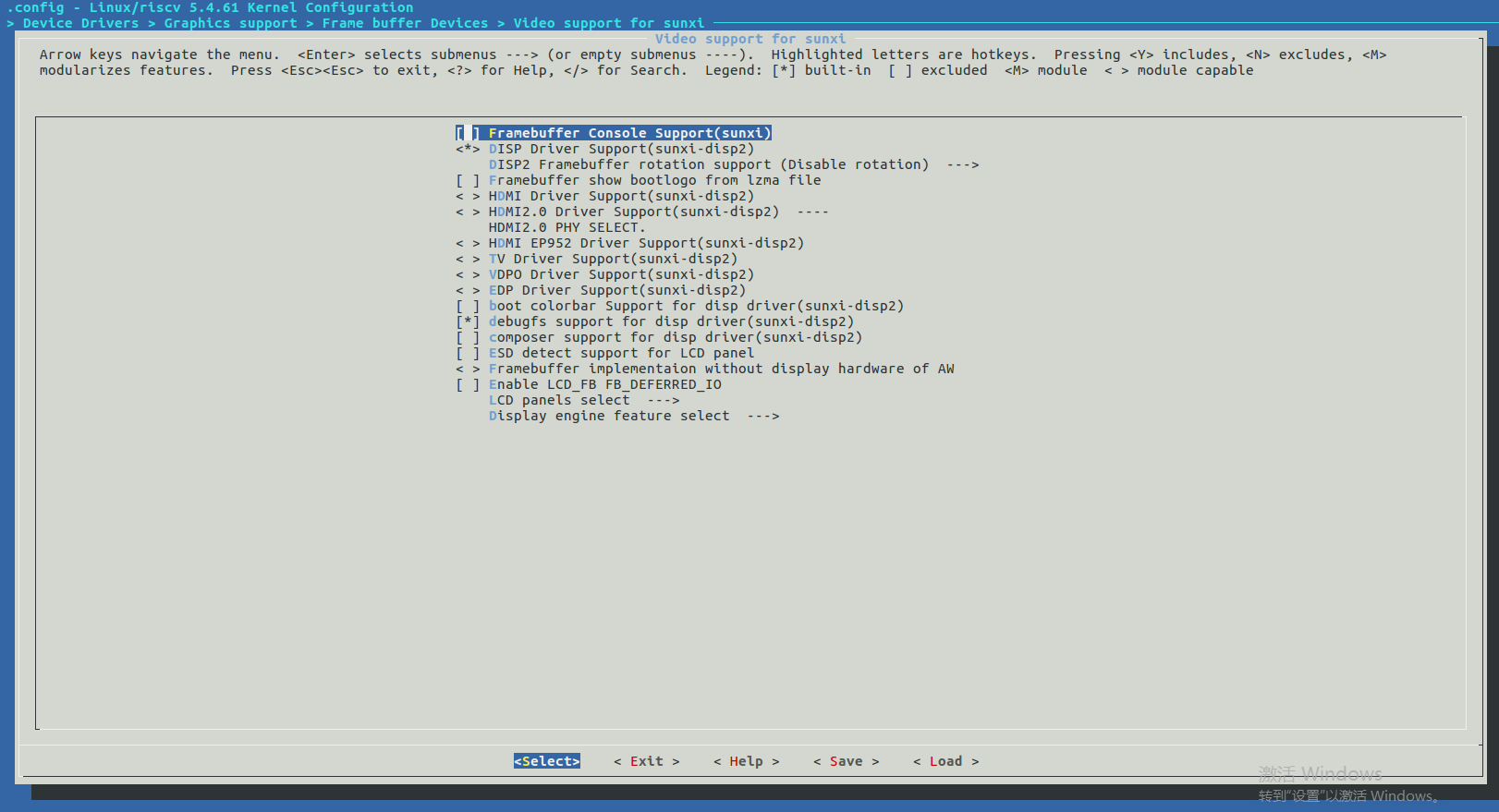

驱动配置信息:

离线

楼主 #2 2022-04-28 16:25:58 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 72

Re: D1s/f133-B 跑tina linux,有fb0设备,但是未执行LCD初始化函数

根据log定位到drivers/video/fbdev/sunxi/disp2/disp/dev_disp_debugfs.c中:

int dispdbg_init(void)

{

my_dispdbg_root = debugfs_create_dir("dispdbg", NULL);

printk(KERN_INFO "[%s] %s: %d\n", __FILE__, __FUNCTION__, __LINE__);

if (!debugfs_create_file

("command", 0644, my_dispdbg_root, NULL, &command_ops))

goto Fail;

if (!debugfs_create_file

("name", 0644, my_dispdbg_root, NULL, &name_ops))

goto Fail;

if (!debugfs_create_file

("start", 0644, my_dispdbg_root, NULL, &start_ops))

goto Fail;

printk(KERN_INFO "[%s] %s: %d\n", __FILE__, __FUNCTION__, __LINE__);

if (!debugfs_create_file

("param", 0644, my_dispdbg_root, NULL, ¶m_ops))

goto Fail;

if (!debugfs_create_file

("info", 0644, my_dispdbg_root, NULL, &info_ops))

goto Fail;

if (!debugfs_create_file

("dbglvl", 0644, my_dispdbg_root, NULL, &dbglvl_ops))

goto Fail;

#if defined(CONFIG_SUNXI_MPP)

if (debugfs_mpp_root) {

if (!debugfs_create_file("vo", 0644, debugfs_mpp_root, NULL,

&vo_ops))

goto Fail;

}

#endif /*endif CONFIG_SUNXI_MPP */

return 0;

Fail:

printk(KERN_INFO "[%s] %s: %d\n", __FILE__, __FUNCTION__, __LINE__);

debugfs_remove_recursive(my_dispdbg_root);

my_dispdbg_root = NULL;

return -ENOENT;

}

static const struct file_operations start_ops = {

.write = dispdbg_start_write,

.read = dispdbg_start_read,

.open = dispdbg_start_open,

.release = dispdbg_start_release,

};

static ssize_t dispdbg_start_write(struct file *file, const char __user *buf,

size_t count, loff_t *ppos)

{

printk(KERN_INFO "[%s] %s: %d\n", __FILE__, __FUNCTION__, __LINE__);

if (count >= sizeof(dispdbg_priv.start))

return 0;

if (copy_from_user(dispdbg_priv.start, buf, count)) {

pr_warn("copy_from_user fail\n");

return 0;

}

if (dispdbg_priv.start[count - 1] == 0x0A)

dispdbg_priv.start[count - 1] = 0;

else

dispdbg_priv.start[count] = 0;

printk(KERN_INFO "[%s] %s: %d\n", __FILE__, __FUNCTION__, __LINE__);

dispdbg_process();

return count;

}

static void dispdbg_process(void)

{

......

if (!strncmp(dispdbg_priv.command, "enable", 6)) {

printk(KERN_INFO "[%s] %s: %d\n", __FILE__, __FUNCTION__, __LINE__);

lcd->enable(lcd);

}

......

}调用的层次是

dispdbg_init()

if (!debugfs_create_file

("start", 0644, my_dispdbg_root, NULL, &start_ops));

dispdbg_start_write();

dispdbg_process();

if (!strncmp(dispdbg_priv.command, "enable", 6)) {

printk(KERN_INFO "[%s] %s: %d\n", __FILE__, __FUNCTION__, __LINE__);

lcd->enable(lcd);

}

在lcd->enable(lcd)中最后会调用到LCD_panel_init函数;

log看到的是只执行了:

if (!debugfs_create_file

("start", 0644, my_dispdbg_root, NULL, &start_ops));

start_ops里的.wrire函数dispdbg_start_write没有执行到,导致了LCD_panel_init函数没有被执行;

是要在应用程序里面操作fb0设备才会执行dispdbg_start_write 进行初始化?

但是用cat /dev/urandom > /dev/fb0 并没有看到dispdbg_start_write被执行到的log;

离线

楼主 #4 2022-04-28 16:51:33 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 72

Re: D1s/f133-B 跑tina linux,有fb0设备,但是未执行LCD初始化函数

是 NV3052C 驱动芯片吗?

不是,是公司弄的一颗芯片......

离线

楼主 #6 2022-04-28 17:34:22 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 72

Re: D1s/f133-B 跑tina linux,有fb0设备,但是未执行LCD初始化函数

岁月快快快 说:哇酷小二 说:是 NV3052C 驱动芯片吗?

不是,是公司弄的一颗芯片......

逻辑分析仪搭一下,很容易判断问题的。

不是时序的问题,是初始化函数都没跑进去,发不了spi初始化数据。。。

离线

楼主 #7 2022-04-29 11:13:00 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 72

Re: D1s/f133-B 跑tina linux,有fb0设备,但是未执行LCD初始化函数

修改了uboot的屏驱动和设备树,就可以初始化了,这样的话不就是内核里面的屏驱动没起作用

最近编辑记录 岁月快快快 (2022-04-29 11:14:24)

离线

#8 2022-04-29 11:52:04 分享评论

离线